- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

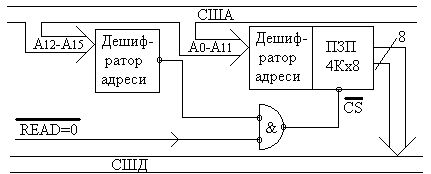

5.5 Інтерфейс з пзп

Розглянемо задачу розробки інтерфейсу для ПЗП або ППЗП. Нехай постійний ЗП має ємність 4 Кбайт. Тоді до адресних ліній ПЗП під'єднано безпосередньо 12 молодших розрядів (А0 – А11) (рисунок 5.4). Дешифратор, вмонтований в ПЗП дозволяє мати доступ до будь-яких з 4096 (212=4096) 8-розрядних слів ПЗП.

Рисунок 5.4 - Приклад організації інтерфейсу з ПЗП

Адресні

лінії чотирьох старших розрядів (А12-А15)

ідуть в пристрій комбінованої логіки

- дешифратор адреси. Для доступу до ПЗП

і зчитування з нього даних МП повинен

активізувати лінії адреси А0-А11,

встановити L-сигнал READ

і L-рівень на виході дешифратора. Тоді

на виході логічного елемента “І”

появиться сигнал L-рівня, яким активізується

вхід

![]() вибору кристала.

вибору кристала.

Допустимо, що МП необхідно звернутись до пам'яті за адресою 0000Н (0000 0000 0000 00002). Молодших 12 бітів

підключаються

до адресних ліній А0-А11

дешифратора ПЗП. Старші розряди

декодуються

дешифратором адреси. Якщо (А12-А15)=00002,

дешифратор адреси видає на виході сигнал

L-рівня, при допомозі якого активізується

вхід

![]() .

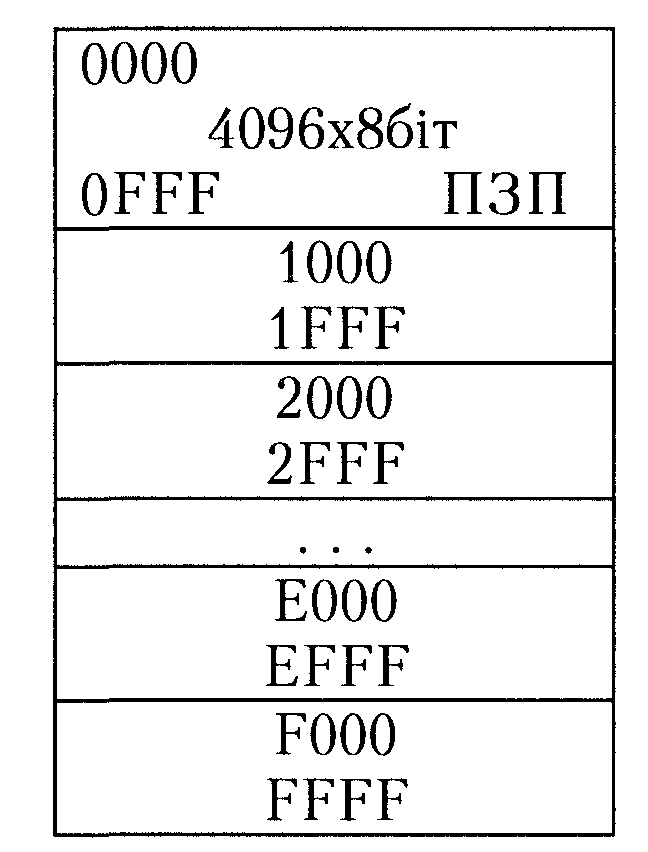

Адресне поле МП (для К580) має ємність

64Кбайт (65 536 комірок пам'яті), які можна

поділити на 16 сегментів по 4К кожний.

Роль дешифратора адреси в тому, щоб

забезпечити МП доступ тільки до одного

із сегментів одночасно. Якщо на 4 входи

дешифратора подаються 0000, то доступним

є нульовий сегмент ( поле пам'яті

0000-ОFFFН). Якщо на його входах 0001, тоді

доступним є перший сегмент (поле пам'яті

1000-1FFFН). Таким чином старші розряди (4

біти) вибирають сегмент пам'яті, а молодші

12 біт визначають потрібну комірку

пам'яті в цьому сегменті (рисунок 5.5 ).

.

Адресне поле МП (для К580) має ємність

64Кбайт (65 536 комірок пам'яті), які можна

поділити на 16 сегментів по 4К кожний.

Роль дешифратора адреси в тому, щоб

забезпечити МП доступ тільки до одного

із сегментів одночасно. Якщо на 4 входи

дешифратора подаються 0000, то доступним

є нульовий сегмент ( поле пам'яті

0000-ОFFFН). Якщо на його входах 0001, тоді

доступним є перший сегмент (поле пам'яті

1000-1FFFН). Таким чином старші розряди (4

біти) вибирають сегмент пам'яті, а молодші

12 біт визначають потрібну комірку

пам'яті в цьому сегменті (рисунок 5.5 ).

Пам'ять МПС

Рисунок 5.5

Описаний спосіб відрізняється простотою і досконалістю.

-

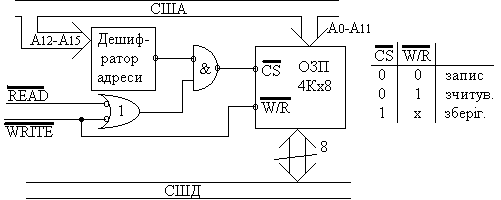

Інтерфейс з озп

Інтерфейс для ОЗП будується аналогічно, як і для ПЗП, але з деякими додатковими схемами керування записом (ввід даних в ОЗП) і зчитування (вивід даних з ОЗП).

Рисунок 5.6 – Приклад

побудови інтерфейсу з ОЗП

Схема декодування адреси в коло керування ОЗП ємністю 4к8, працює згідно до таблички істинності (рисунок 5.6 ).

Вхідний

сигнал

![]() повинен мати низький рівень незалежно

від того, буде виконуватись операція

зчитування чи запису. Якщо сигнал

повинен мати низький рівень незалежно

від того, буде виконуватись операція

зчитування чи запису. Якщо сигнал

![]() МП має високий рівень, в той час коли

МП має високий рівень, в той час коли

![]() - низький, інформація із ОЗП виводиться

на шину даних, щоб МП міг ії зчитати. У

цьому випадку за сигналом

- низький, інформація із ОЗП виводиться

на шину даних, щоб МП міг ії зчитати. У

цьому випадку за сигналом

![]() відпирається шинний формувач з трьома

станами на виході ОЗП. Якщо сигнал

відпирається шинний формувач з трьома

станами на виході ОЗП. Якщо сигнал

![]() при

цьому

L-рівня, відпирання формувачів не

відбувається, а дані записуються для

зберігання в комірку пам'яті, адреса

якої подана на ША ОЗП.

при

цьому

L-рівня, відпирання формувачів не

відбувається, а дані записуються для

зберігання в комірку пам'яті, адреса

якої подана на ША ОЗП.

Сигнал

![]() в схемі має низький рівень, коли сигнал

вибірки адреси ОЗП і сигнали

в схемі має низький рівень, коли сигнал

вибірки адреси ОЗП і сигнали

![]() або

або

![]() також

L-рівня. Лінія

також

L-рівня. Лінія

![]() з'єднана

з входом

з'єднана

з входом

![]() ОЗП, який має внутрішнє з'єднання за

схемою “I” з другим входом

ОЗП, який має внутрішнє з'єднання за

схемою “I” з другим входом

![]() .

Таким чином сигнал

.

Таким чином сигнал

![]() ігнорується

до тих пір, доки

ігнорується

до тих пір, доки

![]() Н-рівня.

Н-рівня.

Приклад:

Нехай ОЗП ємністю 4К необхідно розмістити

в третьому сегменті зверху. Тоді

дешифратор адреси для активізації

вибору кристала повинен дешифрувати

сигнал (А12-А15)=00102

з рівнем L-сигнала. Молодші розряди

адреси (А0-А11)

декодуються внутрішнім дешифратором

ОЗП. Тоді при

![]() Н-рівня відбувається зчитування, а при

L-рівні - запис.

Н-рівня відбувається зчитування, а при

L-рівні - запис.

Пам’ять МПС

-

0000 H

ПЗП 4К8

ОFFF H

1000 H

1FFF H

2000 H

ОЗП 4К8

2FFF H

. . .

F000 H

FFFF H

Рисунок 5.7