- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

Центральний процесорний елемент К1810 ВМ 86 є однокристальним 16-бітовим МП, виконаним за високоякісною n-МОП технологією. Кристал містить біля 29 000 транзисторів і споживає потужність 1.7 Вт від джерела +5В. Схема випускається в 40-вивідному корпусі. Синхронізується однофазними імпульсами з частотою 25 МГц від зовнішнього генератора. Швидкодія МП на операціях обробки даних складає 1.66-106 оп/с при періоді тактових імпульсів 200 нc.

МП ВМ86 має 14 16-ти бітових внутрішніх регістрів і утворює 16-ти бітову ШД для зв'язку із зовнішньою пам'яттю і портами вводу-виводу. ША має 20 ліній, що дозволяє адресувати пам'ять в 1Мбайт=220=1 048 576 Байтів. При використанні операцій вводу-виводу використовуються 8- або 16-бітові адреси, сумарна ємність памяті яких складає 64 КБайт. У ВІС ВМ86 реалізована багаторівнева система переривань по вектору, число яких складає 256.

МП ВМ86 є результатом удосконалення МП ВМ80 і архітектура обох має багато спільного. Програмно-доступні вузли і системи команд ВМ80 можуть бути підмножиною вузлів і системи команд ВМ86.

МП ВМ86 є аналогом МП відомої фірми Intel 8086, а ВМ88 - 8088. Ці мікропроцесори є основою персональних ЕОМ типу ІВМ РС/ХТ.

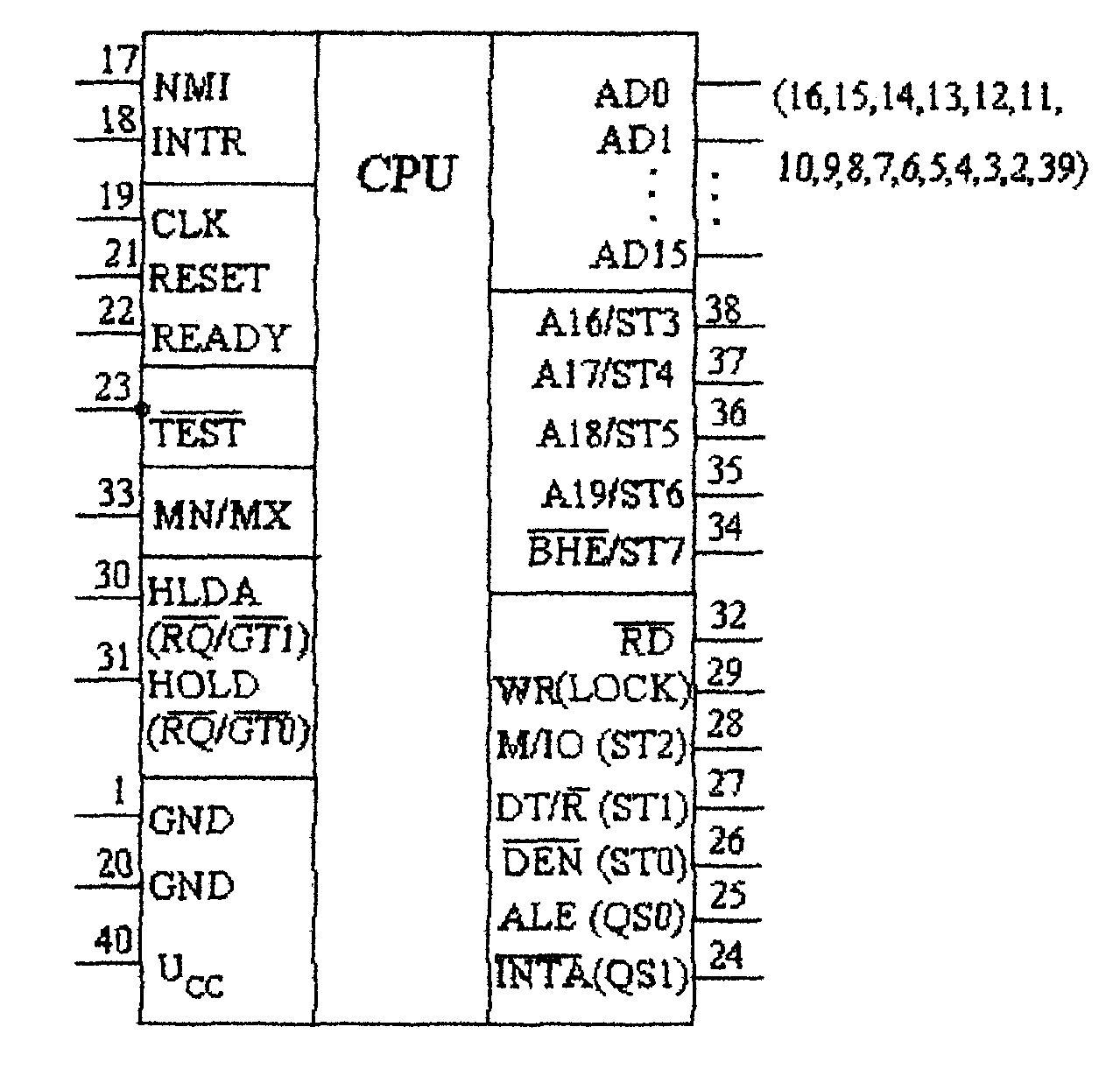

Призначення виводів МП

Призначення виводів МП залежить від режиму його роботи. Вісім виводів МП мають подвійне призначення (позначення в дужках відповідає максимальному режиму). В таблиці 4.7. приведені використання виводів МП, які є загальними для режиму роботи МП з мінімальною та максимальною конфігурацією, в таблиці 4.8-призначення виводів тільки в мінімальному режимі, а в таблиці 4.9 - використання тільки в максимальному режимі. Буквою Z позначені тристабільні виводи. Детальніше можна ознайомитись з даним матеріалом в літературі ([2], с. 158-164; [З], с.8-14; [4], с.227-229).

Рисунок 4.24 - Умовне графічне зображення МП К1810 ВМ86

Таблиця 4.7

|

Позначення |

Призначення |

Тип |

|

АD15-АDО |

Лінії шини адреси/даних (ШАД) |

Вихід (z) |

|

А16/S3 |

Лінії адреси/стану. Під час такту Т1 містять |

Вихід (z) |

|

А17/S4 |

старші біти адреси при зверненні до пам'яті і |

|

|

А18/S5 |

ЗП, а в такті Т2, ТЗ, ТW і Т4 - інформацію |

|

|

А 19/S6 |

про стан МП |

|

|

ВНЕ/S7 |

Дозвіл старшого байта шини/стан |

Вихід (z) |

|

RD |

Читання, строб який вказує, що МП виконує |

Вихід (z) |

|

|

цикл читання |

|

|

RDU |

Готовність, підтвердження того, що адресо- |

Вхід |

|

|

ваний пристрій готовий для взаємообміну з |

|

|

|

МП даними |

|

|

INTR |

Запит переривання, при якому МП перехо- |

Вхід |

|

|

дить на підпрограму обробки переривань, |

|

|

|

коли є дозвіл |

|

|

NMI |

Немасковане переривання, викликає перери- |

Вхід |

|

|

вання за фіксованим вектором, яке не може |

|

|

|

бути заперечене програмнo |

|

|

ТЕSТ |

Вхідний сигнал., який перевіряється коман- |

Вхід |

|

|

дою WAIT, за якою при TEST=1 наступає |

|

|

|

режим "очікування" |

|

|

CLK, (CLC) |

Тактові імпульси синхронізації роботи МП |

Вхід |

|

|

Обнуління, заставляє МП одразу припинити |

|

|

RESЕТ(СLR) |

дії і почати виконання програми спочатку |

Вхід |

|

МN(MX)

(МХ)

|

Мінімальний/ максимальний режим роботи МП |

Вхід

|

Таблиця 4.8

|

Позначення |

Призначення |

Тип |

|

INTA |

Підтвердження переривань, спробує читання |

Вихід |

|

|

вектора переривань |

|

|

ALE(STB) |

Дозвіл регістра-фіксатора адреси, стробує |

Вихiд |

|

|

появу адресної інформації на ШАД |

|

|

DEN(DE) |

Дозвіл даних, стробує. появу даних на ШАД |

Вихід (z) |

|

DT/DR(OP/IP)

|

Передача (прийом) даних, визначає напря |

Вихід (z) |

|

|

мок пересилання даних на ШАД |

|

|

M/IO |

Звернення до ЗП або пристрою вводу-виводу |

Вихід (z) |

|

|

в даному циклі шини |

|

|

WR

|

Запис, строб про виконання МП циклу запи- |

Вихід (z) |

|

|

су |

|

|

HOLD

|

Запит захоплення, зовнішній пристрій запи |

Вхід |

|

|

тує шини МП |

|

|

HLDA |

Підтвердження захоплення, МП перевів |

Вихід |

|

|

свої шини в третій стан |

|

Таблиця 4.9

|

Позначення |

Призначення |

Тип |

|

S2,S1,S0(SТ2- |

Лінії стану, характеризують тип виконувано- |

Вихід (z) |

|

SТО) |

го циклу; необхідний для синтезу керуючих |

|

|

|

сигналів |

|

|

RQ/GTO |

Запит/представлення, використовується для |

Вхід/вихід |

|

RQ/GTI |

обміну сигналами між процесорами в бага- |

|

|

(RQ/ЕО) |

топроцесорній системі, для формування про- |

|

|

(RQ/Е1) |

цедури використання шин |

|

|

LOСК |

Блокування (зайнята) шини, інформуються |

Вихід |

|

|

інші процесори і пристрої, що вони не мо- |

|

|

|

жуть запитувати шину |

|

|

QS1,QS0 |

Стан черги, вказує стан внутрішньої 6- |

Вихід |

|

|

байтової черги команд МП |

|