- •Радиотехнические сигналы

- •1.1. Классификация сигналов

- •1.2. Гармонические сигналы и их представление

- •1.3. Спектральное представление сигналов

- •2.1. Общие понятия и элементы теории электрических цепей

- •Основные электрические величины

- •Идеальные элементы цепей

- •Пассивные двухполюсники

- •Активные двухполюсники

- •Законы Кирхгофа

- •2.2 Методы анализа электрических цепей

- •2.2.1. Основы метода комплексных амплитуд

- •2.2.2. Комплексное сопротивление и комплексная проводимость

- •2.2.3. Методы составления уравнений состояния цепей

- •2.2.4. Элементы теории четырехполюсников

- •2.3. Частотные характеристики линейных цепей

- •3. Основы полупроводниковой электроники

- •3.1. Электрофизические свойства полупроводников

- •3.2. Электронно-дырочный переход

- •3.3. Диоды

- •3.4. Транзисторы

- •3.4.1. Биполярные транзисторы

- •3.4.2. Полевые транзисторы

- •3.4.2.1. Полевые транзисторы с управляющим p-n переходом

- •3.4.2.2. Полевые транзисторы с индуцированным каналом

- •3.4.2.3. Полевые транзисторы со встроенным каналом

- •3.4.3. Дифференциальные параметры и эквивалентные

- •4. Усиление электрических сигналов

- •4.1. Общие сведения

- •4.2. Основные положения линейной теории усиления сигналов

- •4.2.1. Анализ режима покоя. Схемотехника усилительных цепей.

- •4.2.2. Анализ режима усиления

- •4.3. Частотные характеристики усилителя на резисторах

- •4.4. Избирательные усилители

- •4.1.1. Резонансный усилительный каскад с общим эмиттером

- •4.1.2. Каскады со связанными контурами

- •4.5. Обратные связи в электронных усилителях

- •4.6. Повторители напряжения

- •4.7. Усилители постоянного тока

- •4.8. Операционные усилители

- •4.9. Оконечные каскады усилителей мощности

- •5. Генерирование электрических колебаний

- •5.1. Общие сведения

- •5.2. Автогенераторы гармонических колебаний

- •5.2.2. Трехточечные lc – автогенераторы

- •6. Автогенераторы релаксационных колебаний

- •6.1. Общие сведения

- •6.2. Мультивибратор на биполярных транзисторах

- •6.3. Мультивибратор на операционном усилителе

- •7. Нелинейные и параметрические преобразования сигналов.

- •7.1. Общие сведения

- •7.2. Нелинейное резонансное усиление и умножение частоты

- •7.3. Модуляция сигналов

- •7.3.1. Амплитудная модуляция

- •7.3.2. Угловая модуляция

- •7.4. Детектирование сигналов

- •7.4.2. Детектирование сигналов с угловой модуляцией.

- •7.5. Преобразование частоты

- •7.6. Синхронное детектирование

- •7.7. Параметрическое усиление

- •8. Источники вторичного электропитания

- •8.1. Общие сведения

- •8.2. Выпрямители

- •8.2.1. Однополупериодный выпрямитель

- •8.2.2. Мостовой двухполупериодный выпрямитель.

- •8.3. Сглаживающие фильтры.

- •8.4. Стабилизаторы напряжения

- •9. Основы цифровой техники

- •9.1. Общие сведения о цифровой обработке сигналов

- •9.2. Цифровое представление информации. Цифровые коды

- •9.3. Основы алгебры логики

- •9.4. Логические элементы (лэ)

- •9.5. Представление логических переменных электрическими сигналами

- •9.6. Базовые логические элементы. Их классификация,

- •9.7. Классификация логических устройств

- •9.8. Комбинационные логические устройства (клу)

- •9.8.2. Логическое устройство неравнозначности (Исключающее или).

- •9.8.3. Логическое устройство равнозначности

- •9.8.4. Полусумматор одноразрядных двоичных чисел.

- •9.8.5. Сумматор одноразрядных двоичных чисел.

- •9.8.6. Сумматор одноразрядных десятичных чисел.

- •9.8.7. Преобразователи кодов

- •9.9. Последовательностные логические устройства (плу)

- •9.9.1. Триггеры

- •9.9.2. Счетчики.

- •9.9.3. Регистры.

- •9.10. Аналого-цифровые и цифро-аналоговые преобразователи

- •9.11. Запоминающие устройства

- •9.12. Примеры цифровых систем

- •9.12.1. Электронные часы

- •9.12.2. Микропроцессорные системы

- •10. Линейные цепи с распределенными

- •10.1. Общие сведения о длинной линии

- •10.2. Телеграфные уравнения

- •10.3. Длинная линия. Гармонический волновой процесс

- •10.3.1. Общее решение телеграфных уравнений

- •10.3.2. Прямые и обратные волны

- •10.3.3. Отражение волн в длинной линии

- •10.3.4. Интерференция прямых и обратных волн

- •10.3.5. Пример построения интерференционной картины

- •10.3.6. Входное сопротивление длинной линии

- •10.4. Комплексный коэффициент передачи и передаточная функция системы с длинной линией

- •10.4.1. Постановка задачи

- •10.4.2. Способ, основанный на представлении рассматриваемой системы совокупностью функциональных узлов

- •10.4.3. Способ, основанный на использовании граничных условий

- •10.5. Примеры практического применения длинных линий

9.8.6. Сумматор одноразрядных десятичных чисел.

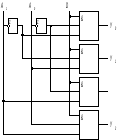

Так как один разряд десятичных чисел представляется четырьмя разрядами двоичных чисел, то сумматор одноразрядных десятичных чисел будет содержать 4 последовательно включенных сумматора одноразрядных двоичных чисел. Схема и условное графическое обозначение одноразрядного сумматора десятичных чисел показаны на рис. 9.11а и рис. 9.11б соответственно.

а) б)

Рис. 9.11. Схема и условное графическое обозначение одноразрядного

сумматора десятичных чисел

9.8.7. Преобразователи кодов

Для преставления информации в цифровой технике применяют различные цифровые коды. В ЭВМ при выполнении операций используются несколько разновидностей двоичных кодов: прямой, обратный, дополнительный и т.д. В цифровых системах связи применяют, например, коды с проверкой четности, коды Хемминга. Такие коды уменьшают вероятность появления ошибок и позволяют даже их исправлять.

Например,

в

процессоре

преобразователь прямого кода в обратный

отрицательное двоичное число X

по значению знакового разряда (Z=1)

переводит в обратный код

.

Положительное число (Z=0)

он передает на выход без изменения

.

Положительное число (Z=0)

он передает на выход без изменения

.

Эту логическую функцию в каждом разряде

выполняет логическое устройство

“Исключающее ИЛИ”

.

Эту логическую функцию в каждом разряде

выполняет логическое устройство

“Исключающее ИЛИ” .

В цифровых системах всегда возникает

необходимость в преобразовании информации

из одного кода в другой. Эту логическую

функцию выполняютпреобразователи

кодов.

К преобразователям кодов относятся и

шифраторы, и дешифраторы. На рис. 9.12

приведены УГО преобразователя кодов,

шифратора и дешифратора соответственно.

.

В цифровых системах всегда возникает

необходимость в преобразовании информации

из одного кода в другой. Эту логическую

функцию выполняютпреобразователи

кодов.

К преобразователям кодов относятся и

шифраторы, и дешифраторы. На рис. 9.12

приведены УГО преобразователя кодов,

шифратора и дешифратора соответственно.

DD1 DD2 DD3

Рис. 9.12. УГО преобразователя кодов, шифратора и дешифратора

9.8.8. Шифраторы и дешифраторы.

Шифратором

(кодером) называется КЛУ, которое

преобразует M-разрядный

код в

N-разрядный

двоичный код, причем

.

Шифратор каждой из 2M

комбинации входных переменных однозначно

ставит в соответствие набор из 2N

выходных переменных. Поскольку

.

Шифратор каждой из 2M

комбинации входных переменных однозначно

ставит в соответствие набор из 2N

выходных переменных. Поскольку

,

то для передачи цифровой информации на

выходе шифратора требуется меньше линий

связи, т.е. шифратор производит “сжатие”

информации.

,

то для передачи цифровой информации на

выходе шифратора требуется меньше линий

связи, т.е. шифратор производит “сжатие”

информации.

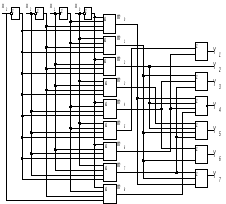

Рассмотрим принцип работы шифраторов на примере шифратора из 10 в 4, который преобразует одноразрядные десятичные числа от 0 до 9 в прямой двоично-десятичный код. Это КЛУ имеет 10 входов и 4 выхода. При подаче 1 на один из 10 входов на выходе формируется 4-х разрядный прямой двоичный код, соответствующий номеру входа, на который был подан уровень 1.

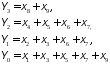

Характер функционирования устройства задает таблица истинности (табл. 9.3). Используя таблицу истинности можно записать следующие алгебраический выражения:

На рис. 9.13 приведена соответствующая логическая схема шифратора из 10 в 4.

Таблица 9.3

Таблица истинности шифратора из 10 в 4

|

№ |

x9 |

x8 |

x7 |

x6 |

x5 |

x4 |

x3 |

X2 |

x1 |

x0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 1 2 3 4 5 6 7 8 9 |

0 0 0 0 0 0 0 0 0 1 |

0 0 0 0 0 0 0 0 1 0 |

0 0 0 0 0 0 0 1 0 0 |

0 0 0 0 0 0 1 0 0 0 |

0 0 0 0 0 1 0 0 0 0 |

0 0 0 0 1 0 0 0 0 0 |

0 0 0 1 0 0 0 0 0 0 |

0 0 1 0 0 0 0 0 0 0 |

0 1 0 0 0 0 0 0 0 0 |

1 0 0 0 0 0 0 0 0 0 |

0 0 0 0 0 0 0 0 1 1 |

0 0 0 0 1 1 1 1 0 0 |

0 0 1 1 0 0 1 1 0 0 |

0 1 0 1 0 1 0 1 0 1 |

Рис. 9.13. Логическая схема шифратора из 10 в 4

Дешифраторы (декодеры) – это КЛУ, которые информацию, представленную в виде двоичного кода преобразуют в исходный М-разрядный код. Дешифраторы выполняют операцию обратную шифраторам.

В цифровых системах дешифраторы часто исполняют роль “детектора”. Они распознают кодовые комбинации и выдают нужную информацию. Дешифраторы входят в состав исполнительных устройств и в зависимости от входного кода команды формируют сигнал управления для других блоков цифровых систем . Так, например в ЗУ по коду адреса дешифратор вырабатывает сигнал на подключение к шине данных ячейки памяти с указанным номером.

Для индикации одноразрядных десятичных чисел на световых табло, в цифровых измерительных приборах, в калькуляторах широко используются семисегментные индикаторы. Для их работы 4-х разрядный двоично-десятичный код с помощью дешифратора из 4 в 7 преобразуется в 7 выходных функций. Рассмотрим принцип работы такого дешифратора. Вид семисегментного индикатора показан на рис. 9.14. Его сегменты пронумеруем, как показано на рис. 9.14 , а их состояние будем описывать логическими функциями (Yn, n = 1, 2, 3, 4, 5, 6, 7).

Рис. 9.14. Общий вид семи сегментного индикатора

Пусть логическая функция равна нулю (Y=0) в случае, когда сектор светится, и Y=1 – когда сектор не светится. Логику работы дешифратора описывает таблица истинности, которая представлена в таблице 9.4.

Таблица 9.4

Таблица истинности дешифратора из 4 в 7

|

|

X3 |

X2 |

X1 |

X0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

mi |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

|

3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

|

4 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

5 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

6 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

|

8 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

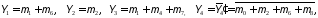

Используя обозначения логических произведений mi на каждом из наборов входных переменных, которые приведены в последнем столбце таблицы, выходные логические функции запишем в следующем виде

Из

таблицы истинности следует, что логическая

функция

принимает значение логической единицы

на шести наборах входных переменных и

равна логическому нулю на четырех

наборах. Поэтому для уменьшения количества

слагаемых сначала записали выражение

для ее инверсии:

принимает значение логической единицы

на шести наборах входных переменных и

равна логическому нулю на четырех

наборах. Поэтому для уменьшения количества

слагаемых сначала записали выражение

для ее инверсии: ,

а затем, используя двойное отрицание,

логическую функцию

,

а затем, используя двойное отрицание,

логическую функцию представили как

представили как .

Вариант логической схемы дешифратора

из 4 в 7 , который соответствует приведенным

формулам без упрощения алгебраического

выражения (оптимизации) показан на

рис. 9.15.

.

Вариант логической схемы дешифратора

из 4 в 7 , который соответствует приведенным

формулам без упрощения алгебраического

выражения (оптимизации) показан на

рис. 9.15.

Рис. 9.15. Логическая схема дешифратора из 4 в 7

9.8.9. Мультиплексоры и демультиплексоры.

Мультиплексоры – это КЛУ, выполняющие управляемую передачу данных из нескольких источников (каналов) в один выходной канал. Мультиплексоры имеют две группы входов: информационные (D0, D1,…, DN) и адресные (A0, A1, …, AM). Количество информационных входов связаны с разрядностью адресных входов соотношением N=2M.

Принцип работы мультиплексора состоит в следующем: К выходному каналу подключается информационный входной канал, номер которого совпадает с кодом адреса.

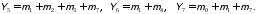

Для примера, синтезируем мультиплексор с двухразрядным адресом. Данному словесному описанию работы мультиплексора соответствует таблица истинности (рис. 9.16а). По таблице истинности записываем алгебраическое выражение в виде суммы логических произведений, состоящих из адресных кодов, умноженных на значение выходной функции:

.

.

Здесь под значением выходной функции подразумеваются входные данные, поступающие по входному каналу, номер которого совпадает с кодом адреса. Полученным алгебраическим выражениям соответствует логическая схема, показанная на рис. 9.16б. УГО мультиплексора представлено на рис. 9.16в.

|

|

|

| ||||||||

|

а) |

б) |

в) |

Рис. 9.16. Таблица истинности, схема и УГО мультиплексора

с двухразрядным адресным входом

Демультиплексор – это КЛУ, которое выполняет управляемую передачу данных от одного источника информации в один из нескольких выходных каналов. Демультиплексор имеет один информационный вход, M-разрядный адресный вход и N выходных каналов. Количество информационных выходных каналов определяется разрядностью адресных входов соотношением N=2M. Принцип работы демультиплексора состоит в следующем. По коду адреса информационный входной канал подключается к выходному каналу, номер которого совпадает с кодом адреса, т.е. демультиплексор имеет N выходных функций. Данному словесному описанию работы демультиплексора в случае двухразрядного адресного входа соответствует таблица истинности (рис. 9.17а). Как видно из таблицы истинности логика работы демультиплексора описывается алгебраическими выражениями в виде логических произведений, состоящих из адресных кодов, умноженных на значение входной функции:

.

.

Полученным алгебраическим выражениям соответствует логическая схема, показанная на рис. 9.17б. УГО демультиплексора представлено на рис. 9.17в.

|

|

|

| |||||||||||||||||||||||||||||||||||

|

а) |

б) |

в) |

Рис. 9.17. Таблица истинности, схема и УГО демультиплексора

с двухразрядным адресным входом