- •4. Використання комп’ютерів в економіці, науці та техніці.

- •8. Структурні схеми комп’ютерів різних поколінь

- •11. Види архітектур комп’ютерів.

- •13. Мікропрограмна реалізація комп’ютерів.

- •14. Багаторівнева організація еом.

- •15.Багатопроцесорна архітектура

- •16.Матричные микропроцессоры

- •24. Архітектура Intel.

- •26. Канальна архітектура

- •40. Організація системи вводу - виводу.

- •41. Контролер вводу – виводу.

- •42.Програмно - керований обмін інформацією між пристроями комп’ютера.

- •45.Апаратні інтерфейси комп’ютера

- •46. Синхронізація в апаратних інтерфейсах комп’ютера. Функції контролера переривань.

- •47. Топологія апаратних інтерфейсів комп’ютера. Особливості реалізації сучасних апаратних інтерфейсів комп’ютера

- •48. Ввід/вивід аналогової інформації. Ввід/вивід дискретних сигналів.

- •53.Введення до іменованих конвеєрів

- •54. Ідея конвеєра команд та вигода від нього, причини збоїв в конвеєрі.

- •55. Ячейки, адреси, машинні слова, розряди, біти, байти.

- •57.Представлення чисел в форматі з фіксованою точкою (представлення беззнакових чисел, представлення знакових чисел в прямому та допоміжному кодах).

- •58. Особливості складання та віднімання цілих чисел (на прикладі персонального комп’ютера - пк).

- •59. Представлення чисел в форматі з плаваючою точкою (на прикладі пк).

- •60. Кодування ascii (American Standart Code for Information Interchange) та стандарт Unicode. Кодування українського тексту (Windows-1251, koi8 та ін.,.

- •64. Типові схеми постійно запам’ятовуючих та оперативно запам’ятовуючих пристроїв комп’ютерів.

- •66. Системні плати, склад, характеристики та порівняння.

- •67.Дискова память,сегмент та зміщення

- •68. Регістри компю’терів

- •69. Контролери комп’ютерів.

- •72. Організація буфера клавіатури.

- •73. Звукові карти та мультимедійні системи.

- •74. Системи охолодження та вентиляції.

- •75. Монітори та їх характеристика.

- •76. Принтери та їх характеристика.

- •77. Сканери та їх характеристика.

- •78. Пристрої управління та їх характеристика (миш, клавіатура, джойстик та ін.).

- •79. Накопичувачі та їх характеристика (fdd, hdd ).

- •80. Накопичувачі та їх характеристика (cd-r, cd-rw, dvd rom, dvd ram, Zip).

- •81. Накопичувачі та їх характеристика (магнітно-оптичні змінні пристрої, флеш-пам’ять та ін.).

- •82. Пристрої зв’язку (модеми, факс-модеми та ін. ).

- •83. Структура таблиці розміщення файлів на магнітних дисках. Типи файлів (імена, формати, розширення) та їх структура.

- •84 Структура даних на носіях інформації

- •4.1 Структура даних на магнітному диску

- •88. Адресация данных и команд.

- •89. Універсальність комп’ютерів: принцип фон-Неймана; гарвардський принцип.

- •92. (Модульний принцип побудови, масштабованість, сумісність програмного забезпечення. Орієнтування на клас задач. Модернізованість.

- •93. Вибір основних складових комп’ютера: процесор, чипсет, тип та об'єм озп, материнська плата, відеокарта, диск, монітор.

- •94. Вибір периферійних пристроїв комп’ютера: сd, dvd, сd-r, cd-rw, флеш-пам’ять.

- •95. Вибір периферійних пристроїв комп’ютера: принтер, сканер, мультимедіа.

- •96. Вибір периферійних пристроїв комп’ютера: модем, факс-модем та ін.

- •97. Перевірка архітектури комп’ютера та його складових. Методи та засоби.

- •98. Тестування та перевірка: оперативної та дискової пам’яті комп’ютера.

- •102. Тестування та перевірки: модема та факс - модема.

- •104. Дайте визначення та охарактерізуйте категорії регістрів

- •107. Визначить функції команди int в Асемблері. Переривання в Асемблері.

- •108. Макроозначення та функції в Асемблері. Макроозначення Invoke.

- •109. Змінні в Асемблері. Їх розміщення.

- •110. Особливості Асемблера в Windows. Створення вікон.

- •112.Опишіть технологію компіляції програм на Асемблері.

- •116. Еом .Характеристики апаратних засоби зберігання й обробки інформації .

- •118. Системний блок персонального комп'ютера- характеристика.

- •119. Апаратні засоби пк

- •120. Процесор (центральный процесор (цп) пк

- •121. Оперативна пам'ять пк та її характеристики.

- •122. Статична пам'ять (sram) у сучасних пк та її характеристики

- •123. Динамічна пам'ять (dram) у сучасних пк та її характеристики

- •126. Постановка задачі . Етапи.

- •127. Які етапи містить наукова постановка задачі

- •128. Характеристика , визначення й опис вхідної/вихідної інформації в постановці задачі.

- •129. Визначення та аналіз разработки алгоритму/алгоритмів рішення задачі.

- •130. Що визначає опис технологічного процесу обробки даних задачі.

- •Характеристика програм, комплексів програм та систем (Приклади)

- •Документування программ

- •Що визначає надійність программного забезпечення(программных средств).

- •Що визначає ефективність технічних засобів.

- •Що визначає ефективність програмних засобів

- •Етапи підготовки програми.

- •137. Модульна структура побудови програмного забезпечення та її характеристики

- •138. Етапи підготовки програм та комплексів программ.

- •140. Агоритми.- характеристика, призначення, функції, принципи побудови.

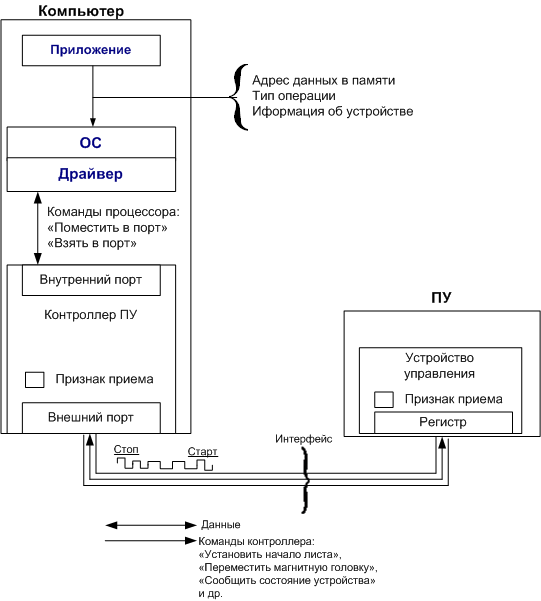

42.Програмно - керований обмін інформацією між пристроями комп’ютера.

Для обміну даними між комп'ютером і периферійним пристроєм (ПП) в комп'ютері передбачений зовнішній інтерфейс (мал. 1.6), тобто набір проводів, що з'єднують комп'ютер і периферійний пристрій, а також набір правив обміну інформацією по цих проводах (іноді замість терміну інтерфейс вживається термін протокол детальніше про ці важливі терміни ми ще поговоримо). Прикладами інтерфейсів, що використовуються в комп'ютерах, є паралельний інтерфейс Centronics, призначений, як правило, для підключення принтерів, і послідовний інтерфейс RS-232C, через який підключаються миша, модем і багато інших пристроїв. Інтерфейс реалізовується з боку комп'ютера сукупністю апаратних і програмних засобів: контролером ПП і спеціальною програмою, керуючою цим контролером, яку часто називають драйвером відповідного периферійного пристрою.

Зі сторони ПП інтерфейс частіше за все реалізовується апаратним пристроєм управління, хоч зустрічаються і програмно-керовані периферійні пристрої.

Програма, що виконується процесором, може обмінюватися даними за допомогою команд введення/виведення з будь-якими модулями, підключеними до внутрішньої шини комп'ютера, в тому числі і з контролерами ПП.

Периферійні пристрої можуть приймати від комп'ютера як дані, наприклад байти інформації, яку треба роздрукувати на папері, так і команди управління, у відповідь на які ПП може виконати спеціальні дії, наприклад перевести головку диска на необхідну доріжку або ж виштовхнути лист паперу з принтера. Периферійний пристрій використовує зовнішній інтерфейс комп'ютера не тільки для прийому інформації, але і для передачі інформації в комп'ютер, тобто обмін даними по зовнішньому інтерфейсу, як правило, є двонаправленим. Так, наприклад, навіть принтер, який за своїй природою є пристроєм виведення, повертає в комп'ютер дані про свій стан.

Контроллери ПП приймають команди і дані від процесора в свій внутрішній буфер, який часто називається регістром або портом, потім виконують необхідні перетворення цих даних і команд відповідно до форматів, зрозумілих ПП, і видають їх на зовнішній інтерфейс.

Розподіл обов'язків між контролером і драйвером ПП може бути різним, але звичайно контролер виконує набір простих команд по управлінню ПП, а драйвер використовує ці команди, щоб примусити пристрій здійснювати більш складні дії по деякому алгоритму. Наприклад, контролер принтера може підтримувати такі елементарні команди, як “Друк символу”, “перехід рядка”, “Повернення каретки” і т. п. Драйвер же принтера за допомогою цих команд організує друк рядків символів, розділення документа на сторінки і інші більш високорівневі операції. Для одного і того ж контролера можна розробити різні драйвери, які будуть управляти даним ПП по-різному одні краще, а інші гірше в залежності від досвіду і здібностей програмістів, їх що розробили.

|

МАЛ. 1.6. Зв'язок комп'ютера з периферійним пристроєм |

Розглянемо схему передачі одного байта інформації від прикладної програми на периферійний пристрій. Програма, яка повинна виконати обмін даними з ПП, звертається до драйвера цього пристрою, повідомляючи йому як параметр адресу байта пам'яті, яку треба передати. Драйвер завантажує значення цього байта в буфер контролера ПП, який починає послідовно передавати біти в лінію зв'язку, представляючи кожний біт відповідним електричним сигналом. Щоб пристрою управління ПП стало зрозуміло, що починається передача байта, перед передачею першого біта інформації контролер ПП формує стартовий сигнал специфічної форми, а після передачі останнього інформаційного біта стоповий сигнал. Ці сигнали синхронізують передачу байта.

Крім інформаційних бітів, контролер може передавати біт контролю парності для підвищення достовірності обміну. Пристрій управління, виявивши на відповідній лінії стартовий біт, виконує підготовчі дії і починає приймати інформаційні біти, формуючи з них байт в своєму приймальному буфері. Якщо передача супроводиться бітом парності, то виконується перевірка правильності передачі: при правильно виконаній передачі у відповідному регістрі пристрою управління встановлюється ознака завершення прийому інформації.

Звичайно на драйвер покладаються найбільш складні функції протоколу (наприклад, підрахунок контрольної суми послідовності байтів, що передаються, аналіз стану периферійного пристрою, перевірка правильності виконання команди). Але навіть самий примітивний драйвер контролера повинен підтримувати як мінімум дві операції: “Взяти дані з контролера в оперативну пам'ять” і “Передати дані з оперативної пам'яті в контролер”.

Існують як вельми спеціалізовані інтерфейси, придатні для підключення вузького класу пристроїв (наприклад, графічних моніторів високої розподільної здатності), так і інтерфейси загального призначення, що є стандартними і що дозволяють підключати різні периферійні пристрої. Прикладом такого інтерфейсу є інтерфейс RS-232C, який підтримується багатьма терміналами, принтерами, маніпуляторами типу “миша” і багатьма іншими пристроями.

43 Організація апаратних переривань в комп’ютері.

Організація апаратних переривань у персональному комп`ютері

Як ви знаєте, персональні комп`ютери почалися з IBM PC. Його архітектура передбачала вісім ліній апаратних переривань (IRQ), якими керував спеціальний контролер. Кожної з них призначався номер, що визначав пріоритет переривання й адреса його оброблювача (так називаний вектор переривання). Нова архітектура, IBM PC AT, передбачала ще вісім ліній переривань, для яких використовувався другий контролер, що підключається до однієї з лінії переривання першого контролера. На жаль, дана архітектура стала останньої після того, як фірма IBM утратила можливість керувати розвитком створеної їй платформи, тому всі сучасні комп`ютери як і раніше мають тільки шістнадцять переривань, одне з яких використовується другим контролером.

У комп`ютера IBM PC AT була тільки одна шина, по якій пристрої могли спілкуватися з процесором і пам`яттю - ISA. Більшість ліній переривань були закріплені за стандартними ISA-пристроями, що залишилися були зарезервовані на майбутнє. Коли це майбутнє наступило, з`ясувалося, що новій універсальній шині PCI дісталося всього чотири вільних переривання. Тому і був придуманий хитрий механізм спільного використання переривань (IRQ Sharing) і динамічного перевизначення номерів (IRQ Steering чи Mapping).

Суть механізму керування перериваннями PCI-пристроїв у наступному. У загальному випадку існує чотири фізичних лінії PCI-переривань, називаних PIRQ0, PIRQ1, PIRQ2 і PIRQ3. Вони підключені до контролера переривань. Кожен PCI-пристрій зі своєї сторони як би має чотири рознімання, називані INT A, INT B, INT C і INT D. Підключати лінії до рознімань можна в будь-якому порядку. Наприклад, для першого PCI-слота можна зробити таке розведення: PIRQ0 - INT A, PIRQ1 - INT B, PIRQ2 - INT C, PIRQ3 - INT D. А для другого - по-іншому: PIRQ0 - INT B, PIRQ1 - INT C, PIRQ2 - INT D, PIRQ3 - INT A. Звичайний пристрій вимагає тільки одну лінію переривання, підключену до INT A. Будучи встановленим у перший слот, пристрій використовує лінію PIRQ0, а в другому слоті на тім же контакті буде лінія PIRQ1. Тим самим пристрою в різних слотах будуть використовувати різні фізичні лінії переривань. Апаратний конфлікт між ними буде виключений.

Шина AGP, будучи по суті спеціалізованою модифікацією PCI, теж використовує одну з ліній PIRQ - звичайно PIRQ0.

Для сучасних систем чотирьох ліній виявляється недостатньо, тому в нових чіпсетах часто застосовуються вісім ліній PIRQ, що точно так само в різних комбінаціях підключаються до слотів PCI і убудованих у плату пристроям.

Лінії PIRQ підключаються до контролера переривань. Їм, як і іншим лініям, призначаються логічні IRQ-номери. Якщо на одній фізичній лінії знаходяться кілька пристроїв (а це припустимо), то усі вони будуть мати той самий номер IRQ. Якщо пристрої знаходяться на різних фізичних лініях, вони все рівно можуть одержати однакові номери IRQ. Нормальні драйвери дозволять їм вільно працювати без утрати продуктивності, тому що шина PCI усе рівно може захоплюватися тільки одним пристроєм. Головне - розпізнати, від якого пристрою прийшов сигнал.

Номера лініям PIRQ призначаються автоматично завдяки горезвісному механізму Plug&Play. Але адже є і ISA-пристрою, що підтримують Plug&Play. Вони теж мають можливість автоматично одержати номер IRQ. Але їхня лінія переривання належить їм монопольно, і якщо такий же номер одержить одна з ліній PIRQ, виникне нерозв`язний конфлікт.

Отже, ми з`ясували, що пристрою PCI повинні бути позбавлені проблем з конфліктами IRQ. Якщо вони, звичайно, правильно працюють, а так буває не завжди. До того ж драйвери повинні підтримувати механізм спільного використання переривань. Пристрою ISA не вміють поділятися лініями переривань і тому є провокаторами конфліктів. Отже, задача усунення конфліктів зводиться до правильного розподілу номерів (джерело проблем - ISA-пристрою і "криві" драйвери) чи до розведення по різних фізичних лініях ("криві" PCI-контролери).

Давайте розглянемо, яким образом у системі відбувається розподіл номерів, і як ми можемо вплинути на цей процес.

Карта переривань

Як я вже говорив, більшість номерів IRQ уже зайняті стандартними пристроями, точніше, призначені їхнім лініям переривань. Пройдемося один по одному:

0 - системний таймер (номер завжди зайнятий);

1 - клавіатура (номер завжди зайнятий);

2 - другий контролер переривань (завжди зайнятий);

3 - порт COM2 (може бути відключений, а номер - звільнений);

4 - порт COM1 (може бути відключений, а номер - звільнений);

5 - порт LPT2 (звичайно номер вільний);

6 - контролер гнучких дисків (може бути відключений, а номер - звільнений);

7 - порт LPT1 (якщо не в режимі EPP чи ECP, те номер вільний);

8 - годинник реального часу (завжди зайнятий);

9 - вільний;

10 - вільний;

11 - вільний;

12 - миша PS/2 (може бути вільний, якщо немає такої миші);

13 - співпроцесор (завжди зайнятий);

14 і 15 - контролер твердих дисків (може бути відключений, а номер - звільнений).

У типовій системі вільні номери 5, 7, 9-11, тобто п`ять з п`ятнадцяти. Крім того, можна змело відключити COM2 і LPT1-порти, збільшивши число вільних номерів до семи. Вільні - не виходить, що не зайнято, просто між ними можлива вільне перетасування.

У будь-якій системі мається три стандартних PCI-пристрої - ACPI-, USB-контролери і відеокарта, кожне з який займе по одному номері. Складний пристрій (наприклад, звукова карта) може зажадати кілька ліній - INT A, INT B і т.д. для своїх компонентів, що між собою не будуть конфліктувати (ніяк різні фізичні лінії), а от з іншими пристроями - запросто.

Довідатися, як у даний момент розподілені номери переривань, можна декількома способами. На самому початку завантаження комп`ютера з`являється текстова таблиця конфігурації. Відразу після її йде перелік PCI-пристроїв із указівкою призначеного їм номера IRQ. Інший спосіб працює в Windows 9x. У панелі керування є іконка "Система", а у аплеті, що запуститься, - закладка "Пристрої". Вибираємо властивості пристрою "Комп`ютер", і там будуть перераховані всі пристрої з вказанням їх IRQ.

У Windows 2000 у нас немає доступу до керування перериваннями, тому для перегляду списку IRQ потрібно скористатися стандартною інформаційною утилітою (Панель керування/Адміністрування/Керування комп`ютером/Зведення про систему/Ресурси апаратури).

Що таке IRQ

Переривання - це базовий механізм реакції системи на виникаючі події. Апаратні переривання, називані звичайно IRQ (Interrupt ReQuest) - це фізичні сигнали, за допомогою яких контролер пристрою інформує процесор про необхідність обробити деякий запит. Умовно схема обробки переривання виглядає в такий спосіб:

процесор одержує сигнал переривання і його номер;

по спеціальній таблиці відшукується адреса програми, відповідальної за обробку переривання з даним номером - обробника переривання;

процесор припиняє поточну роботу і переключається на виконання оброблювача (у загальному випадку це деякий драйвер);

драйвер одержує доступ до пристрою і перевіряє причину виникнення переривання;

запускаються запитані дії - ініціалізація, конфігурування пристрою, обмін даними й ін.

драйвер завершує роботу, і процесор повертається до перерваної задачі.

Очевидно, що для коректної роботи механізму переривань необхідне виконання двох умов: по-перше, сигнал запиту повинний доходити до процесора, і, по-друге, драйвер-оброблювач повинен правильно реагувати на цей сигнал. У випадку конфлікту не дотримується друга умова: сигнал переривання приходить, але реакція на нього виявляється неправильної, у результаті чого ми маємо (у кращому випадку) непрацездатний пристрій.

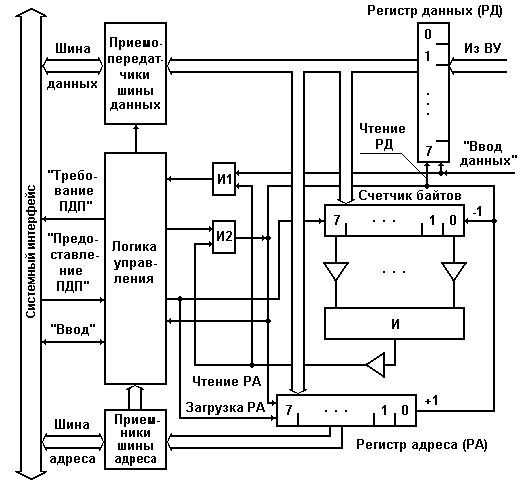

44. Обмін в режимі прямого доступу між пристроями комп’ютера.

Одним із способів обміну даними з ВУ є обмін в режимі прямого доступу до пам'яті (ПДП). У цьому режимі обмін даними між ВУ і основною пам'яттю МІКРОЕОМ відбувається без участі процесора. Обміном в режимі ПДП управляє не програма, що виконується процесором, а електронні схеми, зовнішні по відношенню до процесора. Зазвичай схеми, керівники обміном в режимі ПДП, розміщуються або в спеціальному контроллері, який називається контроллером прямого доступу до пам'яті, або в контроллері самого ВУ.

Обмін даними в режимі ПДП дозволяє використовувати в МІКРОЕОМ швидкодіючі зовнішні пристрої, що запам'ятовують, такі, наприклад, як накопичувачі на жорстких магнітних дисках, оскільки ПДП може забезпечити час обміну одним байтом даних між пам'яттю і ВЗУ, рівне циклу звернення до пам'яті.

Для реалізації режиму прямого доступу до пам'яті необхідно забезпечити безпосередній зв'язок контроллера ПДП і пам'яті МІКРОЕОМ. Для цієї мети можна було б використовувати спеціально виділені шини адреси і даних, що зв'язують контроллер ПДП з основною пам'яттю. Але таке рішення не можна визнати оптимальним, оскільки це приведе до значного ускладнення МІКРОЕОМ в цілому, особливо при підключенні декілька ВЗУ. В цілях скорочення кількості ліній в шинах МІКРОЕОМ контроллер ПДП підключається до пам'яті за допомогою шин адреси і даних системного інтерфейсу. При цьому виникає проблема сумісного використання шин системного інтерфейсу процесором і контроллером ПДП. Можна виділити два основні способи її рішення: реалізація обміну в режимі ПДП з "захопленням циклу" і в режимі ПДП з блокуванням процесора.

Існують два різновиди прямого доступу до пам'яті з "захопленням циклу". Найбільш простій спосіб організації ПДП полягає в тому, що для обміну використовуються ті машинні цикли процесора, в яких він не обмінюється даними з пам'яттю. У такі цикли контроллер ПДП може обмінюватися даними з пам'яттю, не заважаючи роботі процесора. Проте виникає необхідність виділення таких циклів, щоб не відбулося тимчасового перекриття обміну ПДП з операціями обміну, що ініціюються процесором. У деяких процесорах формується спеціальний сигнал, що управляє, вказуючий цикли, в яких процесор не звертається до системного інтерфейсу. При використанні інших процесорів для виділення таких циклів необхідне застосування в контроллерах ПДП спеціальних селектирующих схем, що ускладнює їх конструкцію. Застосування розглянутого способу організації ПДП не знижує продуктивності МІКРОЕОМ, але при цьому обмін в режимі ПДП можливий тільки у випадкові моменти часу одиночними байтами або словами.

Поширенішим є ПДП з "захопленням циклу" і примусовим відключенням процесора від шин системного інтерфейсу. Для реалізації такого режиму ПДП системний інтерфейс МІКРОЕОМ доповнюється двома лініями для передачі сигналів, що управляють, "Вимога прямого доступу до пам'яті" (ТПДП) і "Надання прямого доступу до пам'яті" (ППДП).

Сигнал ТПДП, що управляє, формується контроллером прямого доступу до пам'яті. Процесор, отримавши цей сигнал, припиняє виконання чергової команди, не чекаючи її завершення, видає на системний інтерфейс сигнал ППДП, що управляє, і відключається від шин системного інтерфейсу. З цієї миті всі шини системного інтерфейсу управляються контроллером ПДП. Контроллер ПДП, використовуючи шини системного інтерфейсу, здійснює обмін одним байтом або словом даних з пам'яттю МІКРОЕОМ і потім, знявши сигнал ТПДП, повертає управління системним інтерфейсом процесору. Як тільки контроллер ПДП буде готовий до обміну наступним байтом, він знов "захоплює" цикл процесора і т.д. У проміжках між сигналами ТПДП процесор продовжує виконувати команди програми. Тим самим виконання програми сповільнюється, але у меншій мірі, чим при обміні в режимі переривань.

Застосування в МІКРОЕОМ обміну даними з ВУ в режимі ПДП завжди вимагає попередньої підготовки, а саме: для кожного ВУ необхідно виділити область пам'яті, використовувану при обміні, і вказати її розмір, тобто кількість записуваних в пам'ять або читаних з пам'яті байт (слів) інформації. Отже, контроллер ПДП повинен обов'язково мати в своєму складі регістр адреси і лічильник байт (слів). Перед початком обміну з ВУ в режимі ПДП процесор повинен виконати програму завантаження. Ця програма забезпечує запис у вказані регістри контроллера ПДП початкової адреси виділеної ВУ пам'яті і її розміру в байтах або словах залежно від того, якими порціями інформації ведеться обмін. Сказане не відноситься до початкового завантаження програм в пам'ять в режимі ПДП. В цьому випадку вміст регістра адреси і лічильника байт слів встановлюється перемикачами або перемичками безпосередньо на платі контроллера.

Блок-схема

простого контроллера ПДП,

що забезпечує введення даних в пам'ять

МІКРОЕОМ за ініціативою ВУ

в режимі ПДП

"Захоплення циклу", приведена на

мал. 3.17.

Мал. 3.17. Контроллер ПДП для введення даних з ВУ в режимі "Захоплення циклу" і відключенням процесора від шин системного інтерфейсу

Перед початком чергового сеансу введення даних з ВУ процесор завантажує в регістри його контроллера наступну інформацію: у лічильник байт - кількість що приймаються байт даних, а в регістр адреси - початкова адреса області пам'яті для даних, що вводяться. Тим самим контроллер готується до виконання операції введення даних з ВУ в пам'ять МІКРОЕОМ в режимі ПДП.

Байти даних з ВУ поступають в регістр даних контроллера в постійному темпі. При цьому кожен байт супроводжується сигналом, що управляє, з ВУ "Введення даних", яке забезпечує запис байта даних в регістр даних контроллера. По цьому ж сигналу і при ненульовому стані лічильника байт контроллер формує сигнал ТПДП. По у відповідь сигналу процесора ППДП контроллер виставляє на шини адреси і даних системного інтерфейсу вміст своїх регістрів адреси і даних відповідно. Формуючи сигнал, що управляє, "Висновок", контроллер ПДП забезпечує запис байта даних з свого регістра даних в пам'ять МІКРОЕОМ. Сигнал ППДП використовується в контроллері і для модифікації лічильника байт і регістра адреси. По кожному сигналу ППДП з вмісту лічильника байт віднімається одиниця, і як тільки вміст лічильника стане рівний нулю, контроллер припинить формування сигналів "Вимога прямого доступу до пам'яті".

На прикладі простого контроллера ПДП ми розглянули тільки процес підготовки контроллера і безпосередньо передачу даних в режимі ПДП. На практиці будь-який сеанс обміну даними з ВУ в режимі ПДП завжди ініціюється програмою, що виконується процесором, і включає два наступні етапи. 1. На етапі підготовки ВУ до чергового сеансу обміну процесор в режимі программно-управляемого обміну опитує стан ВУ (перевіряє його готовність до обміну) і посилає у ВУ команди, що забезпечують підготовку ВУ до обміну. Така підготовка може зводитися, наприклад, до переміщення головок на необхідну доріжку в накопичувачі на жорсткому диску. Потім виконується завантаження регістрів контроллера ПДП. На цьому підготовка до обміну в режимі ПДП завершується і процесор перемикається на виконання іншої програми. 2. Обмін даними в режимі ПДП починається після завершення підготовчих операцій у ВУ за ініціативою або ВУ, як це було розглянуто вище, або процесора. В цьому випадку контроллер ПДП необхідно доповнити регістром стану і управління, вміст якого визначатиме режим роботи контроллера ПДП. Один з розрядів цього регістра ініціюватиме обмін даними з ВУ. Завантаження інформації в регістр стану і управління контроллера ПДП проводиться програмним шляхом.

Найбільш поширеним є обмін в режимі прямого доступ до пам'яті з блокуванням процесора. Він відрізняється від ПДП з "захопленням циклу" тим, що управління системним інтерфейсом передається контроллеру ПДП не на час обміну одним байтом, а на час обміну блоком даних. Такий режим ПДП використовується в тих випадках, коли час обміну одним байтом з ВУ зіставно з циклом системної шини.

У МІКРОЕОМ можна використовувати декілька ВУ, що працюють в режимі ПДП. Надання таким ВУ шин системного інтерфейсу для обміну даними проводиться на пріоритетній основі. Пріоритети ВУ реалізуються так само, як і при обміні даними в режимі переривання, але замість сигналів, що управляють, "Вимога переривання" і "Надання переривання" (мал. 18 Організація переривань в МІКРОЕОМ) використовуються сигнали "Вимога прямого доступу" і "Надання прямого доступу", відповідно.