- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

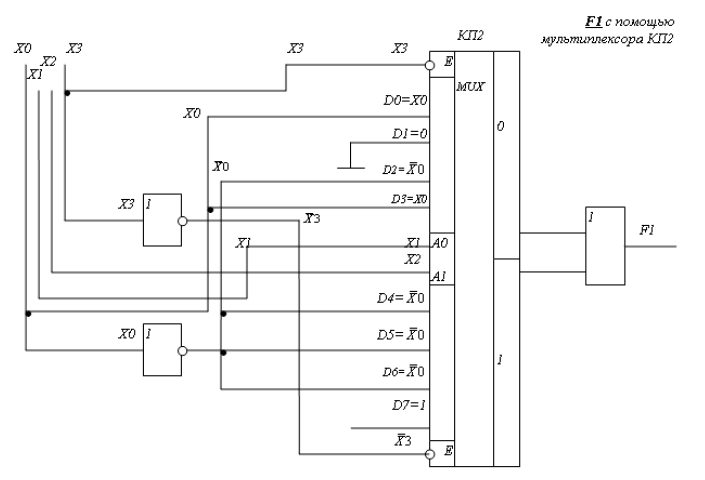

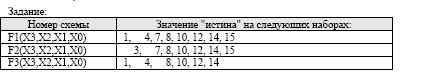

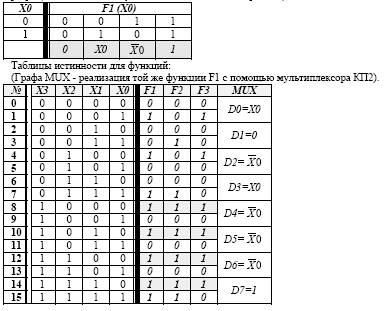

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

Использование мультиплексоров и дешифраторов для построения логических функций.

Пример реализации логической функции на мультиплексора (л/р N2)

Д ля

мультиплексора комбинации соответствуют

(т.к. значимым в данном случае является

только младший разряд, а остальные

выступают только в качестве адресных):

ля

мультиплексора комбинации соответствуют

(т.к. значимым в данном случае является

только младший разряд, а остальные

выступают только в качестве адресных):

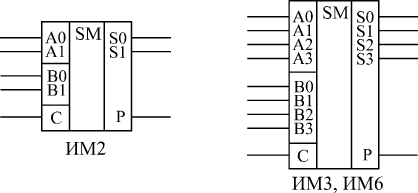

9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

Микросхемы сумматоров (английское Adder), как следует из их названия, предназначены для суммирования двух входных двоичных кодов, то есть выходной код будет равен арифметической сумме двух входных кодов.

Сумма двух двоичных чисел с числом разрядов N может иметь число разрядов (N + 1). Этот дополнительный (старший) разряд называется выходом переноса.

С умматоры

бывают

одноразрядные

(для суммирования двух одноразрядных

чисел), 2-х

разрядные

(суммируют 2-х разрядные числа) и

4-х разрядные

(суммируют 4-х разрядные числа).

умматоры

бывают

одноразрядные

(для суммирования двух одноразрядных

чисел), 2-х

разрядные

(суммируют 2-х разрядные числа) и

4-х разрядные

(суммируют 4-х разрядные числа).

Рис. 6.1. Примеры микросхем сумматоров

В цифровых устройствах применяются одноразрядные суммирующие схемы на два и три входа, причем первую называют полусумматором, вторую - полным одноразрядным сумматором.

Помимо выходных разрядов суммы и выхода переноса, сумматоры имеют вход расширения (другое название - вход переноса) С для объединения нескольких сумматоров с целью увеличения разрядности. Если на этот вход приходит единица, то выходная сумма увеличивается на единицу, если же приходит нуль, то выходная сумма не увеличивается. Если используется одна микросхема сумматора, то на ее вход расширения С необходимо подать нуль. Сумматоры могут использоваться также для суммирования чисел в отрицательной логике (когда логической единице соответствует электрический нуль, и наоборот, логическому нулю соответствует электрическая единица). Но в этом случае входной сигнал переноса С также становится инверсным, поэтому при использовании одной микросхемы сумматора на вход С надо подать электрическую единицу (высокий уровень напряжения). Инверсным становится и выходной сигнал переноса Р, низкий уровень напряжения на нем (электрический нуль) соответствует наличию переноса. То есть получается, что сумматор абсолютно одинаково работает как с положительной, так и с отрицательной логикой.

Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

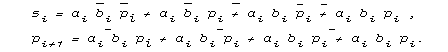

Как видно из выражения для si , сумма двух чисел будет равна 1, если равны 1 или ai , или bi , или pi , а также все цифры. Перенос происходит, когда две цифры из ai , bi , или pi равны единице или равны единице все цифры.

В многоразрядных сумматорах существует возможность параллельной обработки информации. Обработка многоразрядных чисел возможна двумя способами:

можно последовательно раскладывать - разряд за разрядом; в этом случае будет использоваться минимальное количество оборудования;

возможность параллельной обработки информации.

Деление по способу организации процесса суммирования: комбинационные и накапливающие.

К омбинационный

сумматор

- это некоторое логическое устройство,

обеспечивающее получение сигналов

суммы и переноса при одновременной

подаче кодов исходных слов.

омбинационный

сумматор

- это некоторое логическое устройство,

обеспечивающее получение сигналов

суммы и переноса при одновременной

подаче кодов исходных слов.

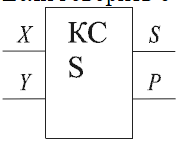

Если говорить о сумматоре комбинационного типа: у нас имеется некоторая схема КС (рис->):

На её входы одновременно приходят данные: первый операнд X и второй операнд Y.

Отличительная особенность комбинационной схемы сумматора - одновременная подача первого и второго слагаемых.

Способы организации цепей переноса в сумматорах:

Существует несколько способов организации цепей переноса в многоразрядных сумматорах:

• групповой,

• последовательный,

• сквозной,

• параллельный

Вот мы недавно с вами говорили о счётчиках - счётчики тоже фактически выполняют роль суммирования.

Ну, там что суммируется? К числу каждый раз прибавляется заданное число - например, единица. Или - может вычитаться - тогда прибавляется минус единица.

Организация переноса в счётчиках построена так же, как организация переноса в сумматорах. Когда мы рассматривали схему синхронного счётчика, мы работали со схемой параллельного переноса. То есть одновременно организовывался перенос за один такт; и была соответствующая комбинационная схема, которая сразу вырабатывала перенос, анализируя состояния всех разрядов вашего счётчика.

А вот счётчик асинхронного типа - там перенос будет организовываться либо как сквозной, либо как последовательный.