- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

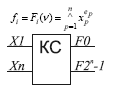

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

Для обратного преобразования двоичных чисел в небольшие по значению десятичные числа используются дешифраторы (называемые также декодерами). Входы дешифратора предназначаются для подачи двоичных чисел, выходы последовательно нумеруются десятичными числами. При подаче на входы двоичного числа появляется сигнал на определенном выходе, номер которого соответствует входному числу.

Дешифраторы имеют широкое применение. В частности, они используются в устройствах, печатающих на бумаге выводимые из цифрового устройства числа или текст. В таких устройствах двоичное число, поступая на вход дешифратора, вызывает появление сигнала на определенном его выходе. С помощью этого сигнала производится печать символа, соответствующего входному двоичному числу.

Дешифраторы (наряду с дешифраторами, мультиплексорами, демультиплексорами - все они относятся к классу схем двойного назначения) широко используются для коммутации в устройствах процессорной техники, и вычислительной технике.

Д ешифратор

-

это некоторая комбинационная схема;

назначение её можно реализовать в

следующем виде:

ешифратор

-

это некоторая комбинационная схема;

назначение её можно реализовать в

следующем виде:

Она будет иметь n входов и 2n выходов (полный дешифратор).

При любой комбинации поступающих на вход сигналов всегда будет возбуждён только один из выходов.

Номер этого возбуждённого выхода будет определяться номером набора.

Р![]() ассмотрим

простейший случай,

когда количество входов этой комбинационной

схемы =1. Схема будет реализована очень

просто: это будет некий инвертер; на

него подаётся наша переменная x1. И будет

два выхода: F1=x1 и F2=x1

вырожденный

дешифратор

типа 1 на 2 ( 1→2 ).

ассмотрим

простейший случай,

когда количество входов этой комбинационной

схемы =1. Схема будет реализована очень

просто: это будет некий инвертер; на

него подаётся наша переменная x1. И будет

два выхода: F1=x1 и F2=x1

вырожденный

дешифратор

типа 1 на 2 ( 1→2 ).

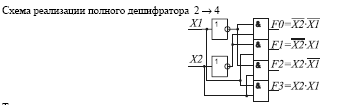

Вообще, если схема реализует 2n выходов - это полный дешифратор (когда n входов и 2n выходов => обозначается: n→2n ).

Кроме полного - есть может быть ещё и неполный дешифратор - это такая комбинационная схема, которая имеет n входов и будет иметь количество выходов N <2n . Такой дешифратор обычно обозначается (n x N).

Неполные дешифраторы обычно бывают 4x10.

У прямого дешифратора - единица может быть только на одном из выходов. Запишем схему полного прямого дешифратора на 4 входа:

Е сли

у этого дешифратора (который мы сейчас

нарисовали) мы заменим все элементы И

на элементы "И-НЕ", то мы получим

дешифратор

с инверсией.

При любой комбинации сигналов, подаваемых

на дешифратор, у нас всегда будет нулевой

уровень только на одном из входов.

сли

у этого дешифратора (который мы сейчас

нарисовали) мы заменим все элементы И

на элементы "И-НЕ", то мы получим

дешифратор

с инверсией.

При любой комбинации сигналов, подаваемых

на дешифратор, у нас всегда будет нулевой

уровень только на одном из входов.

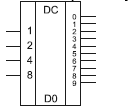

Если говорить об условном графическом обозначении (УГО) дешифраторов, то его можно представить следующим образом: изображение имеет дополнительные поля; у входов обычно записывают веса разрядов 1-2-4-8; у выходов - записываются номера наборов.

В большинстве англоязычных обозначений DC - Decoder.

Если дешифратор выполнен по схеме с открытым коллектором, это обозначается в УГО.

Т акая

реализация позволяет достаточно

легко расширять количество выходов.

Как это делается? Сигнал на старший

разряд второго дешифратора подаётся

как инверсия старшего разряда первого

дешифратора (через инвертер). Когда

этот сигнал =1 - работает первая половинка;

когда =0 - вторая:

акая

реализация позволяет достаточно

легко расширять количество выходов.

Как это делается? Сигнал на старший

разряд второго дешифратора подаётся

как инверсия старшего разряда первого

дешифратора (через инвертер). Когда

этот сигнал =1 - работает первая половинка;

когда =0 - вторая: