- •1. Неймановская структура эвм. Устройство управления с "жесткой логикой" и программируемой логикой и их влияние на структуру эвм и систем.

- •2. Типы интерфейсов. Правила для разработчиков интерфейса.

- •3. Системы счисления, используемые в информационных системах и их особенности. Выбор оптимальной системы счисления для эвм и информационных систем.

- •4. Правило перевода целых и дробных чисел из одной позиционной системы счисления в другую.

- •5. Форма и диапазон представления чисел с плавающей запятой в информационных системах

- •6. Форма и диапазон представления чисел с фиксированной запятой в информационных системах

- •7. Влияние основания системы счисления на диапазон представления чисел в эвм и информационных системах

- •9. Кодирование двоичных чисел при выполнении арифметических операций. Пк и ок. Выполнение в них алгебраического сложения чисел.

- •10.Дополнительный код. Выполнение алгебраического сложения чисел.

- •11. Сложение двоичных чисел, представленных в форме с плавающей запятой.

- •12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

- •13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

- •14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

- •15. Основные законы и задачи алгебры логики.

- •16. Способы задания переключательных функций. Понятие о функционально полных наборах переключательных функций.

- •17. Методы минимизации переключательных функций в базисе и-не; или-не; и, или, не.

- •18. Минимизация переключательных функций методом уменьшения числа инверсий.

- •19. Синхронные и асинхронные триггерные схемы

- •20. Применение триггерных схем для подавления дребезга контактов.

- •22. Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета кратным степени 2.

- •23.Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета не кратным степени 2 (с произвольным модулем).

- •24.Операционные узлы эвм. Регистры памяти (накопительные).

- •25.Операционные узлы эвм. Регистры сдвига.

- •26. Операционные узлы эвм. Регистры реверсивные.

- •27. Синхронные двоичные счетчики с параллельным переносом.

- •28.Структура буферного (сверхоперативного) запоминающего устройства с прямой адресацией

- •29. Линейные и многоступенчатые дешифраторы.

- •30. Шифраторы (кодеры).

- •31.32.Мультиплексоры.

- •33. Демультиплексор.

- •34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

- •35. Синтез сумматора на 3 входа (полного сумматора) в базисе и-или-не.

- •36. Структурная организация эвм. Организация связи между блоками эвм. Типы интерфейсов.

- •37. Двоичный сумматор накапливающего типа

- •38. Десятичный сумматор.

- •39. Многоразрядные последовательные и параллельные сумматоры.

- •40. Вычисления логических условий.

- •41. Схемы сравнения слов на равенство и неравенство.

- •43. Принципы построения микропрограммных автоматов с "жесткой логикой". Абстрактная и структурная модели цифровых автоматов.

- •44. Способы задания цифровых автоматов. Автоматы Мили и Мура.

- •45. Система прерывания с циклическим опросом.

- •46. Канонический метод структурного синтеза автоматов.

- •47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

- •48. Микропрограммируемый автомат Уилкса.

- •49. Синтез микропрограммного автомата Мура по граф-схеме алгоритма

- •50. Управляющие автоматы с программируемой логикой. Способы кодирования микрокоманд. Прямое и косвенное кодирование микроопераций.

- •51. Структура и функционирование микропрограммируемого управляющего автомата.

- •52. Принцип выполнения умножения двоичных чисел с плавающей и фиксированной запятой.

- •53. Структура памяти эвм. Запоминающие устройства, их основные параметры.

- •54. Оперативное, постоянное и внешнее запоминающее устройство.

- •55. Структура запоминающего устройства с произвольным доступом.

- •56. Двоичные счетчики со сквозным переносом. Двоичный синхронный суммирующий счётчик со сквозным ускоренным переносом на jk-триггерах

- •57. Структура запоминающего устройства со стековой организацией.

- •58. Структура запоминающего устройства с магазинной организацией.

- •59. Организация оперативной памяти. Многоблочная память.

- •60. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов.

- •61. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти.

- •62.Организация прямого доступа к памяти

- •63. Двоичные сумматоры. Синтез сумматора на 2 входа

- •64. Программируемая логическая матрица и проектирование схем с их использованием

- •65. Команды эвм. Форматы команд, адресность и модификация команд. Признаки адресации информпации. Неявная и непосредственная адресация.

- •66. Прямая и прямая регистровая адресация.

- •67. Косвенная регистровая адресация

- •68. Задачи, возлагаемые на систему адресации. Автоинкрементая и автодекрементная адресация.

- •69. Принципы защиты информации. Защита информации при страничной адресации.

- •70. Организация виртуальной памяти

- •71. Принципы организации системы прерывания программ. Характеристики систем прерывания. Система прерывания с регистром прерывания.

- •Система с регистром прерывания

- •Система прерывания с циклическим доступом

- •Система прерывания с запоминанием состояния

- •72. Минимизация абстрактных автоматов.

- •73. Арифметико-логические устройства (алу). Классификация алу.

- •74. Методы умножения двоичных чисел.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •75. Умножение двоичных чисел с фиксированной запятой в дополнительных кодах.

- •76. Граф-схема умножения двоичных чисел с фиксированной запятой.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •77. Защита от прерываний. Маскирование сигналов прерывания.

12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

1) N1>0; N2>0

2) N1<0; N2<0

3) N1>0; N2<0

4) N1<0; N2>0

N1=+0,0111 N1OK=0,0111

N2=+0,1110 N2OK=0,1110

N3OK=1,0101

N3=-0,1010=-

N1=-0,0111 N1OK=1,1001

N2=-0,1110 N2OK=1,0010

N3OK=10,1011

N3=+

13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

Модифицированное кодирование

00 +

11 –

NМОК=

NМДК=

N1=-0,1010 N1МОК=11,0101

N2=-0,1000 N2МОК=11,0110

N3МОК=110,1011

N3МОК=10,1100

N1=+0,1010 N1МДК=00,1010

N2=+0,1001 N2МДК=00,1001

N3МДК=01,0011

N1=-0,1010 N1МДК=11,0110

N2=-0,0110 N2МДК=11,1010

N3МДК=111,0000

Модификационные коды упрощают устройство обнаружения переполнения, но вдвое снижают диапазон представления чисел.

±1234567 ±±123456

N1=+0,1110·2+5

N2=+0,1010·2+3

5-3=2

N1=+0,1110·2+5

N2=+0,00101·2+5

N3=(0,11100+0,00101)·2+5=1,00001·2+5

0,00001·2+6

N3=0,10000·22

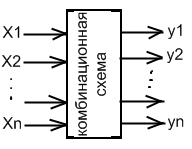

14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

Обработка информации ведется с помощью 2 схем

К комбинационным схемам относятся схемы, в которых выходной сигнал определяется комбинационными сигналами на выходе

В цифровом автомате выходной сигнал определяется как действующими входными сигналами, так и сигналами, поступающими в предыдущий момент времени.

15. Основные законы и задачи алгебры логики.

|

Закон |

Для ИЛИ |

Для И |

|

Переместительный |

X v Y=Y v X |

X*Y=Y*X |

|

Сочетательный |

Xv(YvZ)=(XvY)vZ |

(X*Y)*Z=X*(Y*Z) |

|

Распределительный |

X*(YvZ)=X*YvX*Z |

Xv(Y*Z)=(XvY)*(XvZ) |

|

Правила Де Моргана |

|

|

|

Идемпотенции |

XvX=X |

X*X=X |

|

Поглощения |

Xv(X*Y)=Y |

X*(XvY)=X |

|

Склеивания |

(X*Y)v( |

(XvY)( |

|

Операция переменной с ее инверсией |

Xv |

X* |

|

Операции с константами |

Xv0=X ; Xv1=1 |

X*1=X ; X*0=0 |

|

Двойного отрицания |

|

|

Задачи:

1. Производить логический анализ схемы. По логической схеме составить описание ее работы логическими выражениями.

2. Выполнить синтез логической схемы, то есть построить оптимальную из простых.

3. Определить логически полный набор логических элементов.

=

= v

v

*Y)=Y

*Y)=Y vY)=Y

vY)=Y =1

=1 =0

=0 =X

=X =X

=X