- •1. Неймановская структура эвм. Устройство управления с "жесткой логикой" и программируемой логикой и их влияние на структуру эвм и систем.

- •2. Типы интерфейсов. Правила для разработчиков интерфейса.

- •3. Системы счисления, используемые в информационных системах и их особенности. Выбор оптимальной системы счисления для эвм и информационных систем.

- •4. Правило перевода целых и дробных чисел из одной позиционной системы счисления в другую.

- •5. Форма и диапазон представления чисел с плавающей запятой в информационных системах

- •6. Форма и диапазон представления чисел с фиксированной запятой в информационных системах

- •7. Влияние основания системы счисления на диапазон представления чисел в эвм и информационных системах

- •9. Кодирование двоичных чисел при выполнении арифметических операций. Пк и ок. Выполнение в них алгебраического сложения чисел.

- •10.Дополнительный код. Выполнение алгебраического сложения чисел.

- •11. Сложение двоичных чисел, представленных в форме с плавающей запятой.

- •12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

- •13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

- •14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

- •15. Основные законы и задачи алгебры логики.

- •16. Способы задания переключательных функций. Понятие о функционально полных наборах переключательных функций.

- •17. Методы минимизации переключательных функций в базисе и-не; или-не; и, или, не.

- •18. Минимизация переключательных функций методом уменьшения числа инверсий.

- •19. Синхронные и асинхронные триггерные схемы

- •20. Применение триггерных схем для подавления дребезга контактов.

- •22. Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета кратным степени 2.

- •23.Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета не кратным степени 2 (с произвольным модулем).

- •24.Операционные узлы эвм. Регистры памяти (накопительные).

- •25.Операционные узлы эвм. Регистры сдвига.

- •26. Операционные узлы эвм. Регистры реверсивные.

- •27. Синхронные двоичные счетчики с параллельным переносом.

- •28.Структура буферного (сверхоперативного) запоминающего устройства с прямой адресацией

- •29. Линейные и многоступенчатые дешифраторы.

- •30. Шифраторы (кодеры).

- •31.32.Мультиплексоры.

- •33. Демультиплексор.

- •34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

- •35. Синтез сумматора на 3 входа (полного сумматора) в базисе и-или-не.

- •36. Структурная организация эвм. Организация связи между блоками эвм. Типы интерфейсов.

- •37. Двоичный сумматор накапливающего типа

- •38. Десятичный сумматор.

- •39. Многоразрядные последовательные и параллельные сумматоры.

- •40. Вычисления логических условий.

- •41. Схемы сравнения слов на равенство и неравенство.

- •43. Принципы построения микропрограммных автоматов с "жесткой логикой". Абстрактная и структурная модели цифровых автоматов.

- •44. Способы задания цифровых автоматов. Автоматы Мили и Мура.

- •45. Система прерывания с циклическим опросом.

- •46. Канонический метод структурного синтеза автоматов.

- •47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

- •48. Микропрограммируемый автомат Уилкса.

- •49. Синтез микропрограммного автомата Мура по граф-схеме алгоритма

- •50. Управляющие автоматы с программируемой логикой. Способы кодирования микрокоманд. Прямое и косвенное кодирование микроопераций.

- •51. Структура и функционирование микропрограммируемого управляющего автомата.

- •52. Принцип выполнения умножения двоичных чисел с плавающей и фиксированной запятой.

- •53. Структура памяти эвм. Запоминающие устройства, их основные параметры.

- •54. Оперативное, постоянное и внешнее запоминающее устройство.

- •55. Структура запоминающего устройства с произвольным доступом.

- •56. Двоичные счетчики со сквозным переносом. Двоичный синхронный суммирующий счётчик со сквозным ускоренным переносом на jk-триггерах

- •57. Структура запоминающего устройства со стековой организацией.

- •58. Структура запоминающего устройства с магазинной организацией.

- •59. Организация оперативной памяти. Многоблочная память.

- •60. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов.

- •61. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти.

- •62.Организация прямого доступа к памяти

- •63. Двоичные сумматоры. Синтез сумматора на 2 входа

- •64. Программируемая логическая матрица и проектирование схем с их использованием

- •65. Команды эвм. Форматы команд, адресность и модификация команд. Признаки адресации информпации. Неявная и непосредственная адресация.

- •66. Прямая и прямая регистровая адресация.

- •67. Косвенная регистровая адресация

- •68. Задачи, возлагаемые на систему адресации. Автоинкрементая и автодекрементная адресация.

- •69. Принципы защиты информации. Защита информации при страничной адресации.

- •70. Организация виртуальной памяти

- •71. Принципы организации системы прерывания программ. Характеристики систем прерывания. Система прерывания с регистром прерывания.

- •Система с регистром прерывания

- •Система прерывания с циклическим доступом

- •Система прерывания с запоминанием состояния

- •72. Минимизация абстрактных автоматов.

- •73. Арифметико-логические устройства (алу). Классификация алу.

- •74. Методы умножения двоичных чисел.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •75. Умножение двоичных чисел с фиксированной запятой в дополнительных кодах.

- •76. Граф-схема умножения двоичных чисел с фиксированной запятой.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •77. Защита от прерываний. Маскирование сигналов прерывания.

47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

Обычно при проектировании различных устройств предварительно составляются так называемые содержательная граф-схема алгоритма (ГСА), в которой внутри условных и операторных вершин записаны не элементы множеств X и Y, а логические условия и микрооперации в содержательных терминах.

После

построения содержательной ГСА логические

условия и микрооперации кодируются

символами

![]() соответственно.

соответственно.

Пусть автомат Мили задан в виде ГСА. Для определения числа состояний автомата необходимо произвести разметку ГСА, которая выполняется в следующем порядке:

-

символом аО отмечается вход первой вершины, следующей за начальной, а также вход конечной вершины.

-

входы вершин, следующих за операторными вершинами, отмечаются символами а1, а2, и т.д.

-

входы двух различных вершин, за исключением конечной и первой, следующей за начальной, не могут быть отмечены одинаковыми символами.

-

не одна из вершин не отмечается двумя состояниями.

После разметки ГСА строится граф автомата Мили.

Закодировать состояния автомата можно следующим образом:

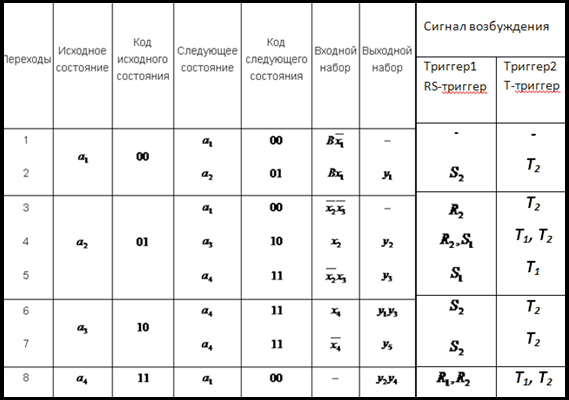

Для построения функций возбуждения и выходов используется структурная таблица, которая отчасти повторяет таблицу переходов, но содержит коды состояний и перечень сигналов возбуждения, формируемых на переходе (аn, аm). В столбце сигналов возбуждения указывается сигнал St, если триггер на переходе (аn, аm) переключается из состояния 0 в состояние 1, и сигнал Rt, если триггер переключается из состояния 1 в состояние 0 . Сигналом Tt триггеры переключаются по счётному выходу.

Таблица 1.Структурная таблица автомата Мили

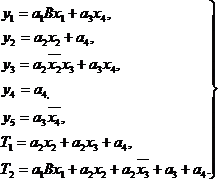

На основании таблицы 1 строится каноническая система функций выходов и возбуждения

На основе систем булевых функций канонической системы строятся функциональные схемы автоматов Мили на RS- и T- триггерах.

СхемаструктурногоавтоматаМили:

48. Микропрограммируемый автомат Уилкса.

Уилкс предложил микропрограммную концепцию организации управления как средство систематизированного структурированного проектирования устройств управления компьютеров.

В основе идеи лежит тот факт, что для инициирования любой микрооперации достаточно сформировать сигнал управления на соответствующей линии управления, т.е. перевести такую линию в активное состояние. Это может быть представлено с помощью двоичных цифр 1 (активное состояние – есть сигнал управления) и 0 (пассивное состояние – нет сигнала управления). Для указания микроопераций, выполняемых в данном такте, можно сформировать управляющее слово, в котором каждый бит соответствует одной управляющей линии. Такое управляющее слово соответствует микрокоманде. Таким образом, микрокоманда может быть представлена управляющим словом со своей комбинацией нулей и единиц.

Последовательность микрокоманд, реализующих определенный машинный цикл, образует микропрограмму. В терминологии на английском языке микропрограмму часто называют firmware.

Микропрограммы для каждой команды компьютерной системы размещаются в специальном ЗУ, называемом памятью микропрограмм. Процесс формирования сигналов управления можно реализовать, последовательно (с каждым тактовым импульсом) извлекая микрокоманды микропрограммы из памяти и интерпретируя содержащуюся в них информацию о сигналах управления. Отличительней особенностью УУ с программируемой логикой является хранение микрокоманд в виде кодов в специализированном запоминающем устройстве – памяти микропрограмм. Каждой машинной команде в этом ЗУ в явной форме соответствует микропрограмма,поэтому такой метод управления называется микропрограммированием, а устройства управления с программируемой логикой называют микропрограммными.

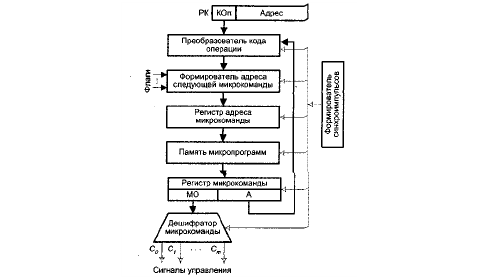

В общем виде устройство микропрограммного управления включает: память микропрограмм (РМП), регистр адреса микрокоманды (РAM), регистр микрокоманды (РМК), дешифратор микрокоманд (ДшМК), преобразователь кода операции, формирователь адреса следующеймикрокоманды Ф(АСМ), формирователь синхроимпульсов (ФСИ).

Запуск микропрограммы выполнения операции осуществляется путем передачи кода операции из РК на вход преобразователя, в котором код операции преобразуется в начальный адрес микропрограммы

Этот адрес поступает через ФАСМ в регистр адреса микрокоманды. Выбранная по адресу Ан из ПМП микрокоманда заносится в РМК. Каждая микрокоманда в общем случае содержит микрооперационную (МО) и адресную (А) части. Микрооперационная часть микрокоманды поступает на дешифратор микрокоманды, на выходе которого образуются управляющие сигналы Ci, инициирующие выполнение микроопераций в исполнительных устройствах и узлах системы. Адресная частьмикрокоманды подается в ФАСМ, где формируется адрес следующей микрокоманды Амк. Этот адрес может зависеть от адреса на выходе преобразователя кода операции Aн, адресной части текущей микрокоманды А и значений осведомительных сигналов (флагов) X, поступающих от исполнительных устройств. Сформированный адрес микрокоманды снова записывается в РАМ, и процесс повторяется до окончания микропрограммы. Разрядность адресной (RА) и микрооперационной (RМО) частей микрокоманды определяются из соотношений

где N МК – общее количество микрокоманд; NСУ – общее количество формируемых

сигналов управления.

В свою очередь,

необходимая емкость памяти микропрограмм

равна

![]()