- •1. Неймановская структура эвм. Устройство управления с "жесткой логикой" и программируемой логикой и их влияние на структуру эвм и систем.

- •2. Типы интерфейсов. Правила для разработчиков интерфейса.

- •3. Системы счисления, используемые в информационных системах и их особенности. Выбор оптимальной системы счисления для эвм и информационных систем.

- •4. Правило перевода целых и дробных чисел из одной позиционной системы счисления в другую.

- •5. Форма и диапазон представления чисел с плавающей запятой в информационных системах

- •6. Форма и диапазон представления чисел с фиксированной запятой в информационных системах

- •7. Влияние основания системы счисления на диапазон представления чисел в эвм и информационных системах

- •9. Кодирование двоичных чисел при выполнении арифметических операций. Пк и ок. Выполнение в них алгебраического сложения чисел.

- •10.Дополнительный код. Выполнение алгебраического сложения чисел.

- •11. Сложение двоичных чисел, представленных в форме с плавающей запятой.

- •12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

- •13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

- •14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

- •15. Основные законы и задачи алгебры логики.

- •16. Способы задания переключательных функций. Понятие о функционально полных наборах переключательных функций.

- •17. Методы минимизации переключательных функций в базисе и-не; или-не; и, или, не.

- •18. Минимизация переключательных функций методом уменьшения числа инверсий.

- •19. Синхронные и асинхронные триггерные схемы

- •20. Применение триггерных схем для подавления дребезга контактов.

- •22. Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета кратным степени 2.

- •23.Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета не кратным степени 2 (с произвольным модулем).

- •24.Операционные узлы эвм. Регистры памяти (накопительные).

- •25.Операционные узлы эвм. Регистры сдвига.

- •26. Операционные узлы эвм. Регистры реверсивные.

- •27. Синхронные двоичные счетчики с параллельным переносом.

- •28.Структура буферного (сверхоперативного) запоминающего устройства с прямой адресацией

- •29. Линейные и многоступенчатые дешифраторы.

- •30. Шифраторы (кодеры).

- •31.32.Мультиплексоры.

- •33. Демультиплексор.

- •34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

- •35. Синтез сумматора на 3 входа (полного сумматора) в базисе и-или-не.

- •36. Структурная организация эвм. Организация связи между блоками эвм. Типы интерфейсов.

- •37. Двоичный сумматор накапливающего типа

- •38. Десятичный сумматор.

- •39. Многоразрядные последовательные и параллельные сумматоры.

- •40. Вычисления логических условий.

- •41. Схемы сравнения слов на равенство и неравенство.

- •43. Принципы построения микропрограммных автоматов с "жесткой логикой". Абстрактная и структурная модели цифровых автоматов.

- •44. Способы задания цифровых автоматов. Автоматы Мили и Мура.

- •45. Система прерывания с циклическим опросом.

- •46. Канонический метод структурного синтеза автоматов.

- •47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

- •48. Микропрограммируемый автомат Уилкса.

- •49. Синтез микропрограммного автомата Мура по граф-схеме алгоритма

- •50. Управляющие автоматы с программируемой логикой. Способы кодирования микрокоманд. Прямое и косвенное кодирование микроопераций.

- •51. Структура и функционирование микропрограммируемого управляющего автомата.

- •52. Принцип выполнения умножения двоичных чисел с плавающей и фиксированной запятой.

- •53. Структура памяти эвм. Запоминающие устройства, их основные параметры.

- •54. Оперативное, постоянное и внешнее запоминающее устройство.

- •55. Структура запоминающего устройства с произвольным доступом.

- •56. Двоичные счетчики со сквозным переносом. Двоичный синхронный суммирующий счётчик со сквозным ускоренным переносом на jk-триггерах

- •57. Структура запоминающего устройства со стековой организацией.

- •58. Структура запоминающего устройства с магазинной организацией.

- •59. Организация оперативной памяти. Многоблочная память.

- •60. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов.

- •61. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти.

- •62.Организация прямого доступа к памяти

- •63. Двоичные сумматоры. Синтез сумматора на 2 входа

- •64. Программируемая логическая матрица и проектирование схем с их использованием

- •65. Команды эвм. Форматы команд, адресность и модификация команд. Признаки адресации информпации. Неявная и непосредственная адресация.

- •66. Прямая и прямая регистровая адресация.

- •67. Косвенная регистровая адресация

- •68. Задачи, возлагаемые на систему адресации. Автоинкрементая и автодекрементная адресация.

- •69. Принципы защиты информации. Защита информации при страничной адресации.

- •70. Организация виртуальной памяти

- •71. Принципы организации системы прерывания программ. Характеристики систем прерывания. Система прерывания с регистром прерывания.

- •Система с регистром прерывания

- •Система прерывания с циклическим доступом

- •Система прерывания с запоминанием состояния

- •72. Минимизация абстрактных автоматов.

- •73. Арифметико-логические устройства (алу). Классификация алу.

- •74. Методы умножения двоичных чисел.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •75. Умножение двоичных чисел с фиксированной запятой в дополнительных кодах.

- •76. Граф-схема умножения двоичных чисел с фиксированной запятой.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •77. Защита от прерываний. Маскирование сигналов прерывания.

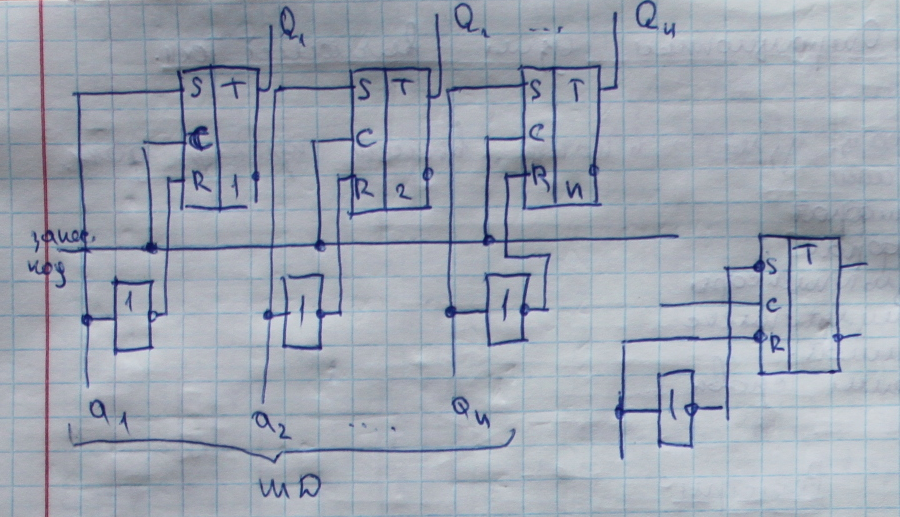

24.Операционные узлы эвм. Регистры памяти (накопительные).

Регистры памяти представляют собой набор синхронных триггеров , каждый из которых хранит один разряд двоичного числа. Ввод (запись, загрузка) и вывод (считывание) информации производится одновременно во всех разрядах параллельным кодом. Запись обеспечивается тактовым импульсом. С приходом очередного тактового импульса происходит обновление записанной информации.

25.Операционные узлы эвм. Регистры сдвига.

Регистры сдвига представляют собой последовательно соединенную цепочку триггеров. Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов.

Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и универсальные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций.

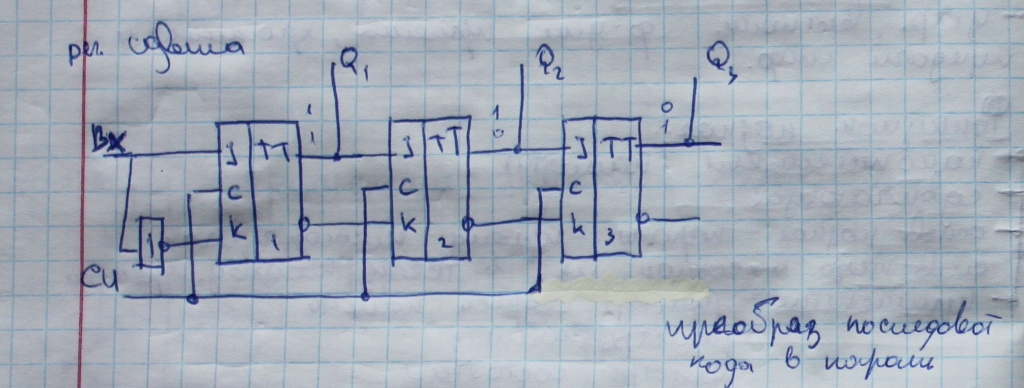

26. Операционные узлы эвм. Регистры реверсивные.

Регистры – это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром связано комбинационное устройство с помощью которого обеспечивается выполнение следующих операций над словами: прием слова в регистр; передача слова из регистра; поразрядовые логические операции; сдвиг слова влево или вправо на заданное число разрядов; преобразование последовательного кода слова в параллельный и обратно; установка регистра в начальное состояние (сброс).

Регистры классифицируются по следующим видам: регистры хранения (регистры памяти); регистры сдвигающие. В свою очередь сдвигающие регистры по способу ввода-вывода информации делятся на параллельные, последовательные, комбинированные, а по направлению передачи информации на однонаправленные и реверсивные.

Важнейшие характеристики регистров разрядность и быстродействие. Разрядность определяется количеством триггеров для хранения числа. Быстродействие характеризуется максимальной тактовой частотой, с которой может производиться запись, чтение и сдвиг информации.

Реверсивные регистры должны содержать логические схемы управления, обеспечивающие прохождение сигнала с выхода Q i-го триггера на вход D i-1-го триггера при сдвиге кода вправо и прохождение этого же сигнала на вход D i+1-го при реализации сдвига кода влево. Схема построения реверсивного регистра приведена на рис. 210.

Направление сдвига кода определяется подачей требуемых сигналов управления на соответствующие входы. Так, в схеме, показанной на рис. 210, при подаче на вход S0 напряжения логической единицы сдвиг кода будет происходить влево (в сторону старших разрядов), поскольку логическая схема управления 2И - 2И - 2ИЛИ будет разрешать прохождение сигналов с выходов Q i-го триггера на вход D i-го триггера, и наоборот, при подаче на вход S1 напряжения логической единицы будет разрешено прохождение сигнала с выхода Q i-го триггера на вход D i1-го триггера - будет реализовываться сдвиг кода вправо (в сторону младших разрядов).

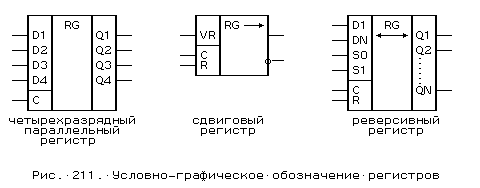

Выводы микросхем, показанных на рис. 211, следующие: D1-DN - входы D-триггеров соответствующих разрядов при записи информации в параллельном коде; Q1-QN - прямые выходы Q-триггеров; С - вход тактовых импульсов; R - вход обнуления; S0,S1 - входы управления направлением сдвига; VR - вход последовательного кода при сдвиге вправо (R - от англ. Right), при сдвиге кода влево применяется обозначение VL - (Left).