- •1. Неймановская структура эвм. Устройство управления с "жесткой логикой" и программируемой логикой и их влияние на структуру эвм и систем.

- •2. Типы интерфейсов. Правила для разработчиков интерфейса.

- •3. Системы счисления, используемые в информационных системах и их особенности. Выбор оптимальной системы счисления для эвм и информационных систем.

- •4. Правило перевода целых и дробных чисел из одной позиционной системы счисления в другую.

- •5. Форма и диапазон представления чисел с плавающей запятой в информационных системах

- •6. Форма и диапазон представления чисел с фиксированной запятой в информационных системах

- •7. Влияние основания системы счисления на диапазон представления чисел в эвм и информационных системах

- •9. Кодирование двоичных чисел при выполнении арифметических операций. Пк и ок. Выполнение в них алгебраического сложения чисел.

- •10.Дополнительный код. Выполнение алгебраического сложения чисел.

- •11. Сложение двоичных чисел, представленных в форме с плавающей запятой.

- •12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

- •13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

- •14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

- •15. Основные законы и задачи алгебры логики.

- •16. Способы задания переключательных функций. Понятие о функционально полных наборах переключательных функций.

- •17. Методы минимизации переключательных функций в базисе и-не; или-не; и, или, не.

- •18. Минимизация переключательных функций методом уменьшения числа инверсий.

- •19. Синхронные и асинхронные триггерные схемы

- •20. Применение триггерных схем для подавления дребезга контактов.

- •22. Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета кратным степени 2.

- •23.Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета не кратным степени 2 (с произвольным модулем).

- •24.Операционные узлы эвм. Регистры памяти (накопительные).

- •25.Операционные узлы эвм. Регистры сдвига.

- •26. Операционные узлы эвм. Регистры реверсивные.

- •27. Синхронные двоичные счетчики с параллельным переносом.

- •28.Структура буферного (сверхоперативного) запоминающего устройства с прямой адресацией

- •29. Линейные и многоступенчатые дешифраторы.

- •30. Шифраторы (кодеры).

- •31.32.Мультиплексоры.

- •33. Демультиплексор.

- •34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

- •35. Синтез сумматора на 3 входа (полного сумматора) в базисе и-или-не.

- •36. Структурная организация эвм. Организация связи между блоками эвм. Типы интерфейсов.

- •37. Двоичный сумматор накапливающего типа

- •38. Десятичный сумматор.

- •39. Многоразрядные последовательные и параллельные сумматоры.

- •40. Вычисления логических условий.

- •41. Схемы сравнения слов на равенство и неравенство.

- •43. Принципы построения микропрограммных автоматов с "жесткой логикой". Абстрактная и структурная модели цифровых автоматов.

- •44. Способы задания цифровых автоматов. Автоматы Мили и Мура.

- •45. Система прерывания с циклическим опросом.

- •46. Канонический метод структурного синтеза автоматов.

- •47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

- •48. Микропрограммируемый автомат Уилкса.

- •49. Синтез микропрограммного автомата Мура по граф-схеме алгоритма

- •50. Управляющие автоматы с программируемой логикой. Способы кодирования микрокоманд. Прямое и косвенное кодирование микроопераций.

- •51. Структура и функционирование микропрограммируемого управляющего автомата.

- •52. Принцип выполнения умножения двоичных чисел с плавающей и фиксированной запятой.

- •53. Структура памяти эвм. Запоминающие устройства, их основные параметры.

- •54. Оперативное, постоянное и внешнее запоминающее устройство.

- •55. Структура запоминающего устройства с произвольным доступом.

- •56. Двоичные счетчики со сквозным переносом. Двоичный синхронный суммирующий счётчик со сквозным ускоренным переносом на jk-триггерах

- •57. Структура запоминающего устройства со стековой организацией.

- •58. Структура запоминающего устройства с магазинной организацией.

- •59. Организация оперативной памяти. Многоблочная память.

- •60. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов.

- •61. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти.

- •62.Организация прямого доступа к памяти

- •63. Двоичные сумматоры. Синтез сумматора на 2 входа

- •64. Программируемая логическая матрица и проектирование схем с их использованием

- •65. Команды эвм. Форматы команд, адресность и модификация команд. Признаки адресации информпации. Неявная и непосредственная адресация.

- •66. Прямая и прямая регистровая адресация.

- •67. Косвенная регистровая адресация

- •68. Задачи, возлагаемые на систему адресации. Автоинкрементая и автодекрементная адресация.

- •69. Принципы защиты информации. Защита информации при страничной адресации.

- •70. Организация виртуальной памяти

- •71. Принципы организации системы прерывания программ. Характеристики систем прерывания. Система прерывания с регистром прерывания.

- •Система с регистром прерывания

- •Система прерывания с циклическим доступом

- •Система прерывания с запоминанием состояния

- •72. Минимизация абстрактных автоматов.

- •73. Арифметико-логические устройства (алу). Классификация алу.

- •74. Методы умножения двоичных чисел.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •75. Умножение двоичных чисел с фиксированной запятой в дополнительных кодах.

- •76. Граф-схема умножения двоичных чисел с фиксированной запятой.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •77. Защита от прерываний. Маскирование сигналов прерывания.

34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

Постоянные запоминающие устройства (ПЗУ) предназначены для хранения информации, например, таблиц, программ, каких-либо констант. Информация в ПЗУ хранится при отключенном источнике питания, т. е. ПЗУ являются энергонезависимыми микросхемами памяти и работают только в режиме многократного считывания информации.

По способу занесения информации в ПЗУ (программирования) их делят на 3 группы:

-

Однократно программируемые изготовителем, называемые масочными (заказными) или сокращенно ПЗУМ (ROM).

-

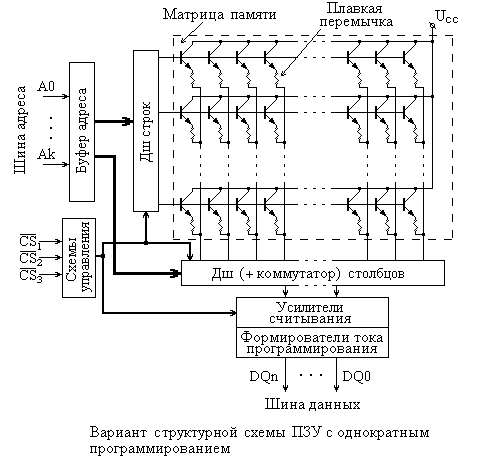

Однократно программируемые пользователем (обычно способом пережигания плавких перемычек на кристалле) или ППЗУ (PROM).

-

Многократно программируемые пользователем (репрограммируемые) или РПЗУ (EPROM).

В однократно программируемых ПЗУ вместо элемента памяти, как в ОЗУ, ставится перемычка между шинами в виде пленочных проводников, диодов, транзисторов. Наличие перемычки соответствует лог. 1, ее отсутствие - лог. 0 или наоборот. Процесс программирования таких ПЗУ заключается в пережигании ненужных перемычек и поэтому в дальнейшем ПЗУ такого рода программировать нельзя.

Программируемое ПЗУ

Программируемые пользователем ПЗУ (ППЗУ) похожи на масочные и отличаются от них тем, что пережигание перемычек (программирование) осуществляет пользователь. Для этого в структуре микросхемы предусмотрены специальные устройства, стоящие на выходах и обеспечивающие формирование тока программирования. Микросхемы ППЗУ выпускаются с целыми металлопленочными перемычками из легкоплавкого материала (например, нихрома) с низким сопротивлением. Процесс программирования состоит в пережигании этих перемычек.

Для программирования ППЗУ, у которых в исходном состоянии записаны лог. 0, необходимо подвести код адреса программируемого элемента и подать на выход, к которому этот элемент памяти относится, одиночный импульс напряжения. При этом через перемычку протекает ток, достаточный для ее пережигания. Пережигать одновременно можно только одну перемычку. На остальные выводы микросхемы ППЗУ должны быть поданы уровни лог. 0. Далее задается следующий адрес и процесс повторяется. Это обобщенный вид процесса программирования.

Для программирования микросхем ППЗУ, у которых в исходном состоянии записаны лог. 1, необходимо на выводы подать лог. 1, а на выход, к которому относится элемент памяти, подать лог. 0.

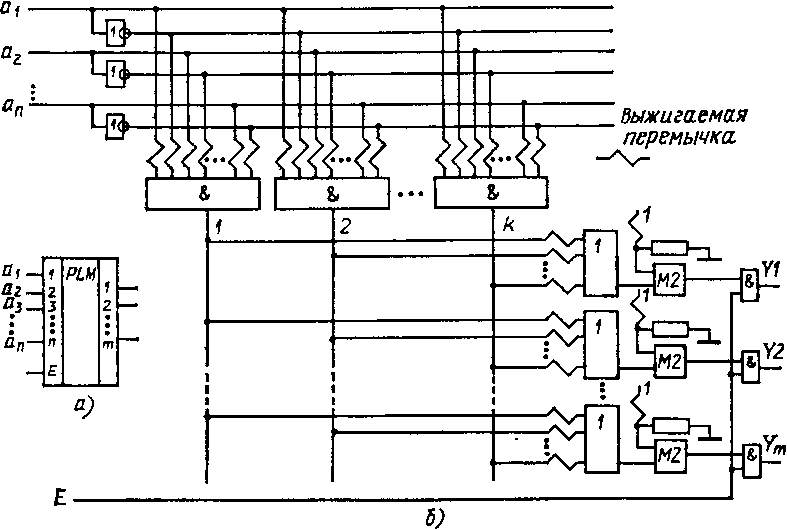

Программируемая логическая матрица

Программируемые логические матрицы (ПЛМ) являются разновидностью ППЗУ. Микросхема ПЛМ включает в себя операционную часть из матрицы И, матрицы ИЛИ, входных и выходных усилителей, программирующую часть из адресных формирователей и программируемого дешифратора. Матрица И выполняет операции логического умножения над входными переменными и их инверсными значениями. Требуемые логические произведения формируются путем пережигания ненужных перемычек между строками и столбцами. Аналогично формируется матрица ИЛИ.