- •1. Неймановская структура эвм. Устройство управления с "жесткой логикой" и программируемой логикой и их влияние на структуру эвм и систем.

- •2. Типы интерфейсов. Правила для разработчиков интерфейса.

- •3. Системы счисления, используемые в информационных системах и их особенности. Выбор оптимальной системы счисления для эвм и информационных систем.

- •4. Правило перевода целых и дробных чисел из одной позиционной системы счисления в другую.

- •5. Форма и диапазон представления чисел с плавающей запятой в информационных системах

- •6. Форма и диапазон представления чисел с фиксированной запятой в информационных системах

- •7. Влияние основания системы счисления на диапазон представления чисел в эвм и информационных системах

- •9. Кодирование двоичных чисел при выполнении арифметических операций. Пк и ок. Выполнение в них алгебраического сложения чисел.

- •10.Дополнительный код. Выполнение алгебраического сложения чисел.

- •11. Сложение двоичных чисел, представленных в форме с плавающей запятой.

- •12. Переполнение разрядной сетки при выполнении алгебраического сложения в обратном и дополнительном кодах.

- •13. Методы обнаружения переполнения разрядной сетки. Модифицированные обратный и дополнительный коды.

- •14. Логические основы эвм и систем. Понятие логической комбинационной схемы и цифрового автомата.

- •15. Основные законы и задачи алгебры логики.

- •16. Способы задания переключательных функций. Понятие о функционально полных наборах переключательных функций.

- •17. Методы минимизации переключательных функций в базисе и-не; или-не; и, или, не.

- •18. Минимизация переключательных функций методом уменьшения числа инверсий.

- •19. Синхронные и асинхронные триггерные схемы

- •20. Применение триггерных схем для подавления дребезга контактов.

- •22. Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета кратным степени 2.

- •23.Операционные узлы эвм. Двоичные счетчики с коэффициентом пересчета не кратным степени 2 (с произвольным модулем).

- •24.Операционные узлы эвм. Регистры памяти (накопительные).

- •25.Операционные узлы эвм. Регистры сдвига.

- •26. Операционные узлы эвм. Регистры реверсивные.

- •27. Синхронные двоичные счетчики с параллельным переносом.

- •28.Структура буферного (сверхоперативного) запоминающего устройства с прямой адресацией

- •29. Линейные и многоступенчатые дешифраторы.

- •30. Шифраторы (кодеры).

- •31.32.Мультиплексоры.

- •33. Демультиплексор.

- •34. Постоянные запоминающие устройства матричного и программируемого пользователем типа, их назначение и структура.

- •35. Синтез сумматора на 3 входа (полного сумматора) в базисе и-или-не.

- •36. Структурная организация эвм. Организация связи между блоками эвм. Типы интерфейсов.

- •37. Двоичный сумматор накапливающего типа

- •38. Десятичный сумматор.

- •39. Многоразрядные последовательные и параллельные сумматоры.

- •40. Вычисления логических условий.

- •41. Схемы сравнения слов на равенство и неравенство.

- •43. Принципы построения микропрограммных автоматов с "жесткой логикой". Абстрактная и структурная модели цифровых автоматов.

- •44. Способы задания цифровых автоматов. Автоматы Мили и Мура.

- •45. Система прерывания с циклическим опросом.

- •46. Канонический метод структурного синтеза автоматов.

- •47. Синтез микропрограммного автомата Мили по граф-схеме алгоритма.

- •48. Микропрограммируемый автомат Уилкса.

- •49. Синтез микропрограммного автомата Мура по граф-схеме алгоритма

- •50. Управляющие автоматы с программируемой логикой. Способы кодирования микрокоманд. Прямое и косвенное кодирование микроопераций.

- •51. Структура и функционирование микропрограммируемого управляющего автомата.

- •52. Принцип выполнения умножения двоичных чисел с плавающей и фиксированной запятой.

- •53. Структура памяти эвм. Запоминающие устройства, их основные параметры.

- •54. Оперативное, постоянное и внешнее запоминающее устройство.

- •55. Структура запоминающего устройства с произвольным доступом.

- •56. Двоичные счетчики со сквозным переносом. Двоичный синхронный суммирующий счётчик со сквозным ускоренным переносом на jk-триггерах

- •57. Структура запоминающего устройства со стековой организацией.

- •58. Структура запоминающего устройства с магазинной организацией.

- •59. Организация оперативной памяти. Многоблочная память.

- •60. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов.

- •61. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти.

- •62.Организация прямого доступа к памяти

- •63. Двоичные сумматоры. Синтез сумматора на 2 входа

- •64. Программируемая логическая матрица и проектирование схем с их использованием

- •65. Команды эвм. Форматы команд, адресность и модификация команд. Признаки адресации информпации. Неявная и непосредственная адресация.

- •66. Прямая и прямая регистровая адресация.

- •67. Косвенная регистровая адресация

- •68. Задачи, возлагаемые на систему адресации. Автоинкрементая и автодекрементная адресация.

- •69. Принципы защиты информации. Защита информации при страничной адресации.

- •70. Организация виртуальной памяти

- •71. Принципы организации системы прерывания программ. Характеристики систем прерывания. Система прерывания с регистром прерывания.

- •Система с регистром прерывания

- •Система прерывания с циклическим доступом

- •Система прерывания с запоминанием состояния

- •72. Минимизация абстрактных автоматов.

- •73. Арифметико-логические устройства (алу). Классификация алу.

- •74. Методы умножения двоичных чисел.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •75. Умножение двоичных чисел с фиксированной запятой в дополнительных кодах.

- •76. Граф-схема умножения двоичных чисел с фиксированной запятой.

- •1) Умножение начиная с младших разрядов множителя:

- •2) Умножение начиная со старших разрядов множителя:

- •77. Защита от прерываний. Маскирование сигналов прерывания.

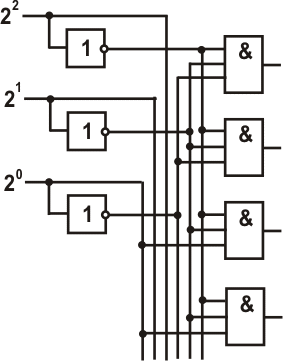

29. Линейные и многоступенчатые дешифраторы.

Дешифратор (декодер) - устройство, преобразующее двоичный код в позиционный (или иной). Другими словами, дешифратор осуществляет обратный перевод двоичных чисел. Единице в каком-либо разряде позиционного кода соответствует комбинация нулей и единиц в двоичном коде, а отсюда следует, что для преобразования необходимо иметь не только прямые значения переменных, но еще и инверсии.

На схеме показаны всего четыре логических элемента И, хотя их должно быть восемь. Три инвертора создают инверсии переменных. Палки, спускающиеся в никуда на самом деле подводят сигналы прямого и инверсного кода к остальным четырем элементам И. Если разрядов будет четыре, то элементы будут четырехвходовыми, понадобится четыре инвертора и 16 элементов И.

Простейший дешифратор:

Логика работы

микросхемы такова: на входы данных

микросхемы подается цифровой код. В

данном случае — это любое трехразрядное

двоичное число. Смысл работы такого

дешифратора — выдать активный сигнал

только на одном из своих выходов. На том

выходе, номер которого соответствует

двоичному коду, присутствующему на его

входах D0...D2.

Это таблица истинности данного дешифратора. Важное значение имеет вход выбора микросхемы CS. Этот вход позволяет включить или выключить всю микросхему. Микросхема работает только в том случае, если на вход CS дешифратора подан разрешающий нулевой сигнал. В противном случае микросхема выключается и на всех ее выходах устанавливается сигнал логической единицы.

|

Входы |

Выходы |

||||||||||

|

D2 |

D1 |

D0 |

CS |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

0 |

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

0 |

|

|

0 |

1 |

0 |

0 |

|

|

|

|

|

0 |

|

|

|

0 |

1 |

1 |

0 |

|

|

|

|

0 |

|

|

|

|

1 |

0 |

0 |

0 |

|

|

|

0 |

|

|

|

|

|

1 |

0 |

1 |

0 |

|

|

0 |

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

X |

X |

X |

1 |

1 |

|

|

|

|

|

|

|

Главное назначение линейного дешифратора—функция выбора одного из нескольких электронных устройств. Например, выбор одной из нескольких микросхем памяти. Каждая такая микросхема должна иметь свой собственный вход CS. К каждому выходу дешифратора подключается одна такая микросхема. Вернее, подключается ее вход CS.

Теперь, если на входы D0—D1 дешифратора подать номер выбираемой микросхемы, она включится, а остальные семь микросхем отключатся. При выключении самого дешифратора отключаются и все подключенные к нему микросхемы.