- •Электротехника и электроника Учебное пособие

- •«Информационные системы и технологии»

- •Введение

- •1 Основные законы электрических цепей. Методы расчета цепей постоянного тока

- •Топологические характеристики, элементы и схемы электрических цепей

- •1.2 Основные законы и соотношения в цепях постоянного тока

- •Методы эквивалентного преобразования схем электрических цепей с пассивными элементами

- •1.4 Характеристика методов расчета цепей постоянного тока. Методы контурных токов и узловых потенциалов

- •1.4.1 Метод контурных токов

- •1.4.2 Метод узловых потенциалов

- •1.5 Баланс активной мощности

- •2 Расчет линейных цепей синусоидального тока

- •2.1 Основные характеристики синусоидальных сигналов

- •2.2 Синусоидальные сигналы в прямоугольных координатах

- •2.3 Представление синусоидальных величин

- •2.4 Закон Ома в комплексной форме для цепей синусоидального тока

- •2.5 Комплексный метод расчета цепей синусоидального тока

- •2.6 Активная, реактивная и полная мощности

- •2.7 Резонанс в цепях синусоидального тока

- •3 Анализ и расчет нелинейных электрических и магнитных цепей

- •3.1 Основные понятия нелинейных электрических и магнитных цепей

- •3.2. Классификация нелинейных элементов

- •3.3 Статическое и дифференциальное сопротивление нэ

- •3.4. Методы расчета нелинейных электрических цепей

- •3.5 Нелинейные индуктивные и емкостные сопротивления

- •3.6 Преобразования, осуществляемые с помощью нелинейных электрических цепей

- •3.7 Основные понятия магнитной цепи

- •3.8 Расчет магнитных цепей

- •3.9 Применение к магнитным цепям методов, используемых для расчета нелинейных электрических цепей

- •4 Трехфазные электрические цепи

- •4.1 Трехфазная система

- •4. 2 Соотношение между фазными и линейными величинами

- •4.3 Приемники, включаемые в трехфазную цепь

- •4.4 Мощность трехфазной системы

- •5 Электромагнитные устройства. Основные виды электрических машин. Трансформаторы

- •5.1 Принципы преобразования электрической энергии

- •5.2 Назначение и принцип действия трансформатора

- •5.3 Классификация трансформаторов

- •Устройство трансформатора

- •5.5 Режимы работы трансформаторов

- •5.6 Потери и кпд трансформатора

- •5.7 Трёхфазные трансформаторы, автотрансформаторы и измерительные трансформаторы

- •6 Машины постоянного тока

- •6.1 Принцип действия генератора и двигателя постоянного тока

- •6.2 Устройство коллекторной машины постоянного тока

- •6.3 Причины, вызывающие искрение на коллекторе

- •6.4 Способы возбуждения машин постоянного тока

- •6.5 Основные характеристики генераторов постоянного тока

- •6.6 Механическая и рабочая характеристики

- •6.7 Двигатели постоянного тока

- •6.8 Потери и кпд машин постоянного тока

- •7 Асинхронные и синхронные машины

- •Асинхронные машины

- •7.1. Устройство асинхронных машин

- •7.2 Режимы работы асинхронной машины

- •7.3 Потери и кпд асинхронного двигателя

- •7.4 Электромагнитный момент и механическая характеристика асинхронного двигателя

- •7.5 Пуск асинхронных двигателей

- •7.6 Рабочие характеристики асинхронного двигателя

- •7.7 Регулирование частоты вращения асинхронных двигателей

- •Синхронные машины

- •7.8 Устройство синхронной машины

- •7.9 Возбуждение синхронных машин

- •7.10 Параллельная работа синхронных генераторов

- •7.11 Потери и кпд синхронных машин

- •7.12 Пуск трехфазного синхронного двигателя

- •8 Элементная база электронных устройств

- •8.1 Электронно-дырочный переход и его свойства

- •8.2 Полупроводниковые диоды

- •8.3 Биполярные транзисторы

- •8.4 Полевые транзисторы

- •8.5 Тиристоры

- •8.6 Интегральные микросхемы

- •8.7 Оптоэлектронные устройства

- •8.8 Индикаторные приборы

- •9 Источники вторичного электропитания

- •9.1 Принципы построения источников вторичного электропитания

- •9.2 Классификация ивэп

- •9.3 Выпрямители: классификация и основные параметры

- •9.4 Управляемый выпрямитель

- •9.5 Стабилизаторы напряжения и тока

- •9.6 Сглаживающие фильтры

- •10 Усилители электрических сигналов

- •Усилители. Классификация и основные характеристики

- •Принцип действия усилителя

- •Обратные связи в усилителях

- •Дифференциальный каскад

- •Операционные усилители

- •Импульсные усилители мощности

- •Автогенераторные устройства

- •11 Основы цифровой электроники. Микропроцессорные средства

- •11.1 Логические элементы

- •11.2 Запоминающие устройства – триггеры

- •11.3 Аналого-цифровые преобразователи

- •11.3.1 Виды аналого-цифровых преобразователей и их особенности

- •11.3.2 Принципы построения ацп

- •11.4 Цифро-аналоговые преобразователи

- •11.4.1 Назначение и виды цифро-аналоговых преобразователей

- •11.4.2 Принципы построения цап

- •11.5 Программируемые устройства. Микропроцессоры

- •12 Электрические измерения и приборы

- •12.1 Общие сведения. Погрешности и классы точности

- •12.2 Классификация электроизмерительных приборов

- •12.3 Электронные и цифровые измерительные приборы

- •12.4 Регистрирующие приборы и устройства

- •12.5 Измерение неэлектрических величин

- •Список рекомендуемой литературы Основная литература

- •Список дополнительной литературы

- •Татьяна Федоровна Морозова Электротехника и электроника

- •355029, Г. Ставрополь, пр.Кулакова, 2

11.2 Запоминающие устройства – триггеры

Триггер – электронное импульсное устройство с двумя устойчивыми состояниями (единичным и нулевым), в которые она может скачком переходить под воздействием внешнего сигнала.

Состояние устойчивого равновесия характеризуется тем, что после слабого внешнего воздействия устройство возвращается в исходное состояние, т. е. токи и напряжения принимают исходные значения в отличие от состояния неустойчивого равновесия, при котором слабое внешнее воздействие нарушает его. Для перехода триггера из одного устойчивого состояния в другое необходимо, чтобы входной сигнал превысил пороговое значение.

Триггеры реализуют на основе логических элементов и выпускают в виде интегральных микросхем, которые используются в вычислительной технике для организации компонентов вычислительных систем: в процессорах, регистрах, счетчиках импульсов и оперативно-запоминающих устройствах (ОЗУ).

В интервале между переключающими сигналами состояние триггера не меняется: триггер «запоминает» поступление сигналов, отражая это величиной потенциала на выходе, поэтому его используют и как элемент памяти. При лавинообразных переключениях на выходе триггера формируются прямоугольные импульсы с крутыми фронтами, что позволяет использовать триггер для формирования прямоугольных импульсов из напряжения другой формы (например, синусоидальной). Два последовательных переключений триггера на выходе формирует один импульс: триггер можно использовать и как делитель частоты переключающих сигналов с коэффициентом, равным двум.

Триггеры классифицируются по следующим признакам: способу приема информации; принципу построения и функциональным возможностям.

1. По способу приема информации различают синхронные, асинхронные и смешанные триггерные схемы.

Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего тактирующего импульса на входе синхронизации. Синхронные триггеры в свою очередь подразделяются на триггеры со статическим и динамическим управлением по входу синхронизации. Статические триггеры воспринимают информационные сигналы при подаче на вход синхронизации логической единицы или логического нуля. Динамические триггеры воспринимают информационные сигналы при изменении сигнала на входе синхронизации от «0» к «1» или от «1» к «0».

2. По структурному построению статические триггеры подразделяют на одноступенчатые (однотактные), двухступенчатые (двухтактные) и триггеры с динамическим управлением. В одноступенчатом триггере имеется одна ступень запоминания информации, в двухступенчатом – две, где информация вначале записывается в первую ступень, а затем переписывается во вторую и появляется на выходе.

3. По функциональным возможностям триггеры разделяют на следующие классы: с раздельной установкой состояния «0» и «1» (RS- триггеры); универсальные (JK- триггеры); с приемом информации по одному входу (D- триггеры, или триггеры задержки); со счетным входом (T- триггеры). Из названий триггеров можно определить количество входов. Так у D- триггера всего один вход D, а у JK – два входа J и K. Если триггер является синхронным – добавляется вход синхронизации С.

Каждый тип триггера имеет собственную таблицу истинности, в которой указывается влияние различных значений на входах триггера на его выходное состояние, которое обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1).

Входы триггеров обозначают следующим образом: S (Set, установить) – вход в RS- триггере, на который подается сигнал и устанавливает триггер в состояние «1»; R ( Reset, сброс) – вход в RS- триггере, на который подается сигнал, переводящий триггер в состояние «0»; J ( Jump, прыжок) – вход в JK- триггер; К (Kill, прибить) – вход в JK- триггере; Т (Toggles, переключить) – счетный вход в Т- триггере; С (Clock, время) вход синхронизирующего сигнала (при тактировании по фронту он обозначается стрелкой: стрелка внутрь – тактирование по переднему фронту, наружу – по заднему); D (Delay, задержка) – вход в D- триггере; Е или EN (Enable, разрешить) – дополнительный асинхронный управляющий вход для разрешения приема информации.

Входы J, K, T всегда синхронные, т. е. тактируются по синхронизирующему сигналу на входе С. В конкретном триггере имеются только некоторые из перечисленных входных линий. Входы, на которые подаются запускающие импульсы, называются установочными (или управляющими).

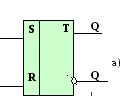

Рассмотрим принцип действия RS-триггера, который может быть реализован на основе логических элементов И-НЕ или ИЛИ-НЕ (рисунок 11.7).

S

Рисунок 11.7 – Структурная схема RS- триггера (а), схема реализации

асинхронного RS - триггера (б) на базе двух элементов 2ИЛИ-НЕ,

временная диаграмма (в) и таблица истинности (г)

В

структуре из двух таких элементов можно

обеспечить положительную обратную

связь, соединив вход одного элемента

с выходом другого. RS-триггер

имеет два выхода: прямой (![]() )

и инверсный (

)

и инверсный (![]() )

и два входа:S

– установки и R

– сброса. Такой триггер является

асинхронным RS-триггером

и применяется как самостоятельно,

а также в качестве запоминающей ячейки

в составе более сложных интегральных

триггеров.

)

и два входа:S

– установки и R

– сброса. Такой триггер является

асинхронным RS-триггером

и применяется как самостоятельно,

а также в качестве запоминающей ячейки

в составе более сложных интегральных

триггеров.

RS- триггер сохраняет свое предыдущее состояние при нулевых входах, и меняет свое выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S выходное состояние становится равным логической единице, а при подаче единицы на вход R выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, является запрещенным.

Переключающим

сигналом для рассматриваемого

триггера является логическая «1», а

также то, что вход S

(установка триггера в состояние Q=1)

должен быть связан с элементом, выход

которого принят за

![]() .

Пусть

триггер (рисунок 11.7,б) находится в

состоянии «0» (Q=0,

.

Пусть

триггер (рисунок 11.7,б) находится в

состоянии «0» (Q=0,

![]() =1),

а на входах действуют сигналыS=0,

R=0.

Для его переключения в состояние Q=1

подадим на входы комбинацию S=1,

R=0.

Тогда на выходе элемента Э2

установится

логический «0», на входах элемента Э1

будут одновременно присутствовать

логические «0», а на выходе Q

установится логическая «1» –триггер

переключается в новое состояние (Q=1,

=1),

а на входах действуют сигналыS=0,

R=0.

Для его переключения в состояние Q=1

подадим на входы комбинацию S=1,

R=0.

Тогда на выходе элемента Э2

установится

логический «0», на входах элемента Э1

будут одновременно присутствовать

логические «0», а на выходе Q

установится логическая «1» –триггер

переключается в новое состояние (Q=1,

![]() =0).

Для переключения его из этого состояния

на входы должна поступить комбинацияS=0,

R=1.

После этого на выходе Q

будет

логический «0», а на входах элемента Э2

одновременно окажутся логические «0»

и его выход примет потенциал,

соответствующий

=0).

Для переключения его из этого состояния

на входы должна поступить комбинацияS=0,

R=1.

После этого на выходе Q

будет

логический «0», а на входах элемента Э2

одновременно окажутся логические «0»

и его выход примет потенциал,

соответствующий

![]() =1,

– триггер переключается в состояниеQ=0,

=1,

– триггер переключается в состояниеQ=0,

![]() =1.

=1.

На рисунке 11.7, в приведена идеализированная временная диаграмма RS-триггера, на которой время переключения триггера принято нулю. Предполагается, что до момента t1: S=0, R=0, и триггер находится в состоянии Q=0. В момент t1 комбинация S=1, R=0 переключает триггер в состояние Q=1. При t2 на входах устанавливается сочетание S=0, R=0, при котором состояние триггера сохраняется прежним. Комбинация S=1, R=0, появляющаяся в момент t3, и комбинация S=0, R=0 в момент t4 изменений не вносят и Q=1. Только в t5 сочетание S=0, R=1 вызывает переключение триггера в состояние Q=0, а последующие изменения логической переменной на входе R состояния триггера не меняют. Следующее переключение происходит в момент t6 при поступлении на входы комбинации S=1, R=0.

На входы устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов, не обладающих одинаковой задержкой. В результате в течение некоторого времени на входах создается непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию устройства. Указанные последствия устраняются применением тактируемого триггера, который кроме информационных входов, имеет синхронизирующий вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на его синхронизирующий вход.

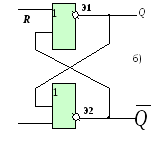

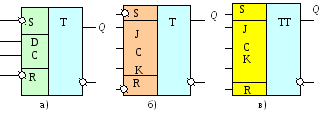

JK- триггер (рисунок 11.8, б) работает аналогично RS- триггеру, но с одним исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S, а вход K аналогичен входу R у RS- триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице, а при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK- триггер не имеет запрещенных состояний на основных входах. На практике применяются только синхронные JK- триггеры, т. е. состояния основных входов J и K учитываются только в момент тактирования, например, по переднему фронту импульса на входе синхронизации. На практике часто встречаются двухступенчатые JK-триггеры, что отражается в их условном обозначении ТТ, с прямыми или инверсными установочными входами R и S (рисунок 11.8, в). Изменение состояния триггера происходит в течение времени действия его заднего фронта.

D - триггер запоминает состояние входа и выдает его на выход (рисунок 11.8, а). D- триггеры имеют два входа: информационный D и синхронизации С. Сохранение информации в D- триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D- триггер называют также триггером с запоминанием информации или триггером- защелкой. D- триггер можно образовать из любых RS- или JK- триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

Рисунок 11.8 – Структурные схемы триггеров:

а – D-триггер; б –JK-триггер; в – двухтупенчатый JK-триггер

Т- триггер (счетный триггер) отличается тем, что он переключается с поступлением каждого импульса на тактовом входе, который в нем называется счетным. Т- триггер может строиться на базе JK-триггера, где он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической «1» т. е. объединив входы J и K. Наличие в D- триггере динамического С входа позволяет получить и на его основе Т- триггер, когда вход D соединяется с инверсным выходом, а на вход С подаются счетные импульсы. В результате триггер при каждом счетном импульсе запоминает значение Q, т. е. переключается в противоположное состояние. Т- триггер применяют в счетчиках числа импульсов, для понижения частоты в два раза, при этом на Т вход подают единицу, а на С – сигнал с частотой, которая и будет поделена.

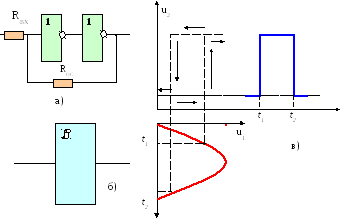

Триггер Шмита содержит два инвертора, охваченных положительной обратной связью, за счет чего состояние выхода схемы изменяется лавинообразно. На выходе инвертора потенциал с логического «0» на «1» изменяется при большей величине входного напряжения, чем с «1» на «0», поэтому схема (рисунок 11.9) обладает гистерезисом, что позволяет использовать ее в качестве формирователя прямоугольных импульсов из входных синусоидальных. Данный триггер имеет по одному входу и выходу и не обладает свойствами запоминающего элемента.

Рисунок

11.9 – Схема реализации триггера Шмитта

(а), его структурная схема (б) и временная

диаграмма (в)

Рисунок

11.9 – Схема реализации триггера Шмитта

(а), его структурная схема (б) и временная

диаграмма (в)

Логические автоматы с памятью – устройства, логические значения, на выходах которых определяются как совокупность логических значений на входах в данный момент, так и состоянием автомата по результатам его предшествующей работы. Запоминание предшествующих состояний обычно выполняется при помощи триггеров. Примерами логических автоматов с памятью являются счётчики импульсов и регистры.