- •Арифметические и логические основы вычислительной техники учебное пособие

- •Введение

- •Арифметические основы вычислительной техники Системы счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Критерии выбора системы счисления

- •Перевод чисел из одной системы счисления в другую

- •Перевод целых чисел.

- •Перевод правильных дробей.

- •Перевод чисел из системы счисления в систему счисления основания которых кратны степени 2

- •Кодирование чисел

- •Переполнение разрядной сетки

- •Модифицированные коды

- •Машинные формы представления чисел.

- •Погрешность выполнения арифметических операций

- •Округление

- •Нормализация чисел

- •Последовательное и параллельное сложение чисел

- •Сложение чисел с плавающей запятой

- •Машинные методы умножения чисел в прямых кодах

- •Ускорение операции умножения

- •Умножение с хранением переносов

- •Умножение на два разряда множителя одновременно.

- •Умножение на четыре разряда одновременно.

- •Умножение в дополнительных кодах.

- •Умножение на 2 разряда Мт в дополнительных кодах.

- •Матричные методы умножения.

- •Машинные методы деления

- •Деление чисел в прямых кодах.

- •Деление чисел в дополнительных кодах.

- •Методы ускорения деления.

- •Двоично-десятичные коды

- •Суммирование чисел с одинаковыми знаками в коде 8421.

- •Сложение чисел с разными знаками.

- •Двоично-десятичные коды с избытком 3

- •Код с избытком 6 для одного из слагаемых

- •Система счисления в остаточных классах (сок)

- •Представление отрицательных чисел в сок

- •Контроль работы цифрового автомата

- •Некоторые понятия теории кодирования

- •Обнаружение и исправление одиночных ошибок путем использования дополнительных разрядов

- •Коды Хемминга

- •Логические основы вычислительной техники Двоичные переменные и булевы функции

- •Способы задания булевых функций

- •Основные понятия алгебры логики

- •Основные законы алгебры логики

- •Формы представления функций алгебры логики

- •Системы функций алгебры логики

- •Минимизация фал

- •Метод Квайна

- •Метод Блейка - Порецкого

- •Метод минимизирующих карт Карно (Вейча)

- •Б) в) Рис. 19 Таблица истинности и карта Карно

- •Минимизация коньюнктивных нормальных форм.

- •Минимизация не полностью определенных фал

- •Кубическое задание функций алгебры логики.

- •Метод Квайна-Мак Класки

- •Алгоритм извлечения (Рота)

- •Минимизация фал методом преобразования логических выражений

- •Применение правил и законов алгебры логики к синтезу некоторых цифровых устройств Синтез одноразрядного полного комбинационного сумматора

- •Синтез одноразрядного комбинационного полусумматора

- •Синтез одноразрядного полного комбинационного сумматора на двух полусумматорах

- •Синтез одноразрядного комбинационного вычитателя

- •Объединенная схема одноразрядного комбинационного сумматора-вычитателя

- •Триггер со счетным входом как полный одноразрядный сумматор

- •Введение в теорию конечных автоматов Основные понятия теории автоматов

- •Способы задания автоматов

- •Структурный автомат

- •Память автомата

- •Канонический метод синтеза

- •Пример синтеза мпа Мили по гса

- •Синхронизация автоматов

- •Литература

- •220013, Минск, п.Бровки, 6.

Канонический метод синтеза

Синтез цифровых устройств выполняется в два этапа:

этап абстрактного синтеза;

этап структурного синтеза.

Для перехода от абстрактного автомата к его структурной схеме требуется:

1) поставить каждой букве входного алфавита Z=[z1,…,zk} совокупность двоичных сигналов из множестваX={x1,x2,…,xL}, тоесть закодировать входные символыабстрактного автомата. ЗначениеLвычисляется следующим образомL=intlog2|X| = [log2|X|], где |X| - мощность множества Х (число различных элементов множества Х);

2) поставить в соответствие каждому выходному символу из W={w1,…,wl} совокупность двоичных выходных сигналов из множестваY={y1,y2,…,yN}, тоесть закодировать выходные символыабстрактного автомата. ЗначениеNвычисляется следующим образомN=intlog2|Y| = [log2|Y|];

3) поставить в соответствие каждому состоянию абстрактного автомата А={aa,…,am} совокупность состояний элементов памятиT={1,2,…,r}, то естьзакодировать состоянияабстрактного автомата. Количество элементов памяти выбирается из условияr=intlog2|А| = [log2|А|];

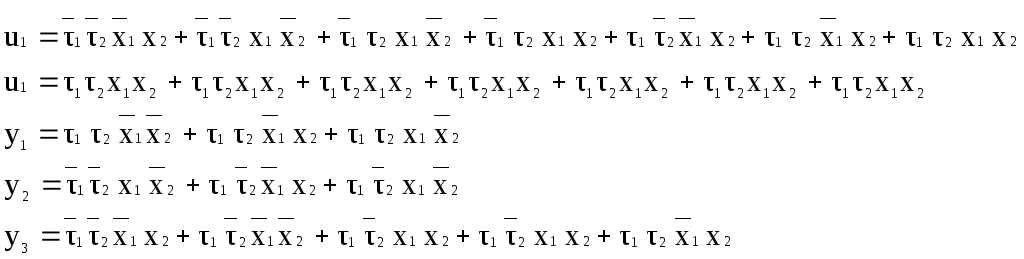

4) составить систему уравнений для функций y1,y2,…,yN,d1,d2,…,drпредназначенной для построения логической схемы комбинационной части структурной схемы.

Полученная таким образом система логических функций называется канонической.

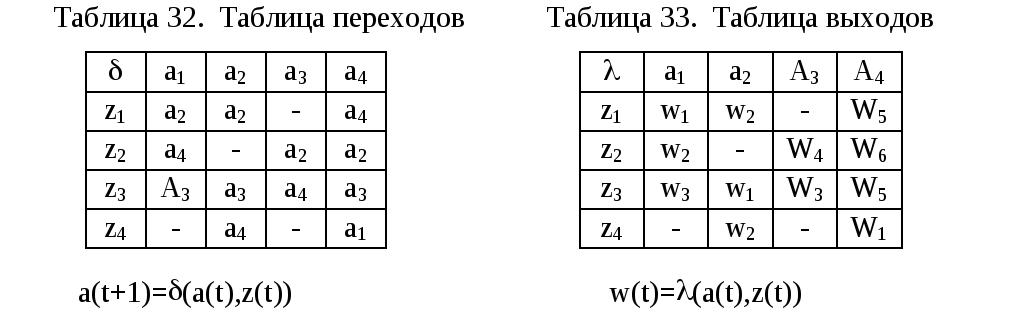

Рассмотрим пример структурного синтеза автомата Мили блок памяти которого построен на Т-триггерах. Исходные данные для выполнения синтеза структурной схемы заданы таблично (таблицы 32 и 33). Таблица истинности работы Т-триггера приведена в таблице 29.

Определяем

вначале общее количество входов, выходов

и элементов памяти автомата.

Определяем

вначале общее количество входов, выходов

и элементов памяти автомата.

L=intlog2|X| = [log2|X|]= [log24]=2;

N=intlog2|Y| = [log2|Y|]= [log24]=2;

r=intlog2|А| = [log2|А|]= [log26]=3;

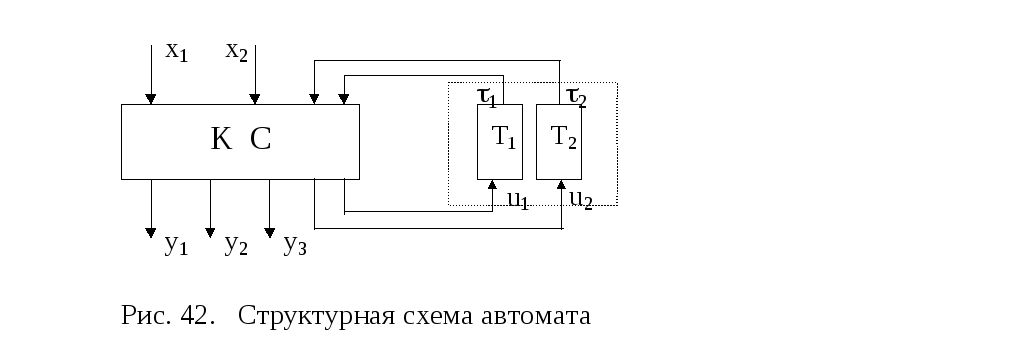

Структурная схема автомата изображена на рисунке (см. рис.42).

На

основании полученных значений построим

таблицы и выполним кодирование входных,

выходных символов и состояний исходного

автомата (таблица 34).

На

основании полученных значений построим

таблицы и выполним кодирование входных,

выходных символов и состояний исходного

автомата (таблица 34).

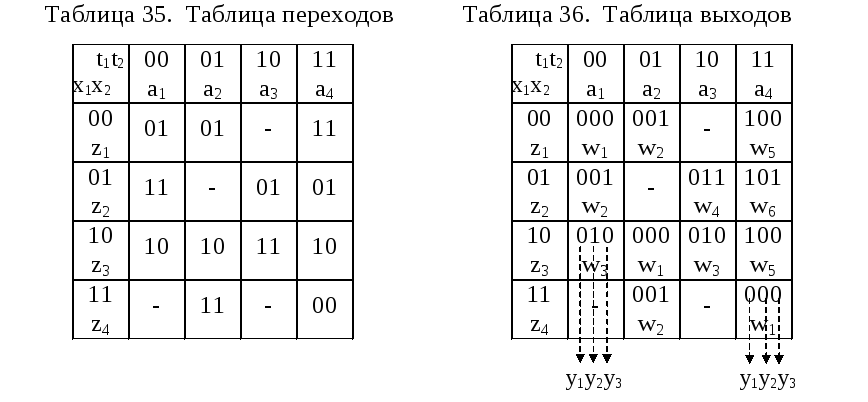

На основании кодирования строим таблицы переходов и выходов структурного автомата (таблицы 35 и 36). Они получаются путем занесения соответствующих значений из таблицы 34 в исходные таблицы 32 и 33.

![]()

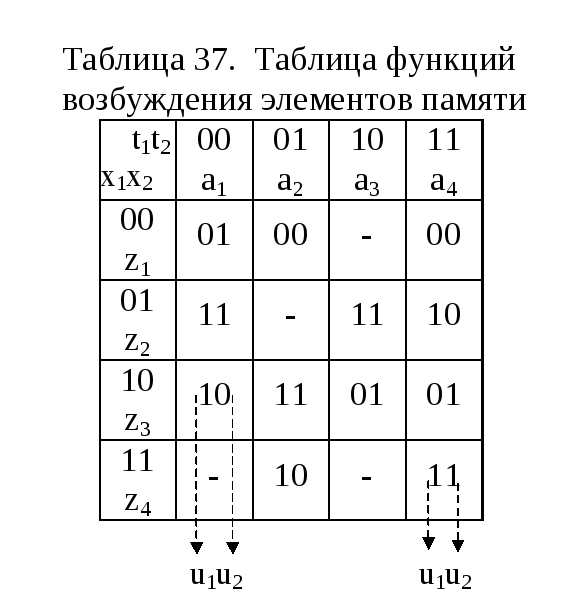

Используя таблицу переходов Т-триггера (табл. 29) построим таблицу 37 - функций возбуждения элементов памяти по таблице 35.

Если r-й триггер на некотором переходе переключается из состояния 0 в состояние 1, или наоборот, тоui=1, в противном случае (то есть еслиr-й триггер не переключается)ui=0. Например, рассмотрим переход из состояния 10 в состояние 11 (3-й столбец 3-я строка). Первый триггер (установленный в 1) не меняет своего значения, поэтому функция возбуждения элемента памяти для негоu1=0. Второй триггер изменяет свое значение с 0 на 1, следовательноu2=1.Остальные клетки таблицы 37 заполняются аналогично. На основании таблиц 36 и 37 запишем систему логических функций для построения комбинационной схемы автомата.

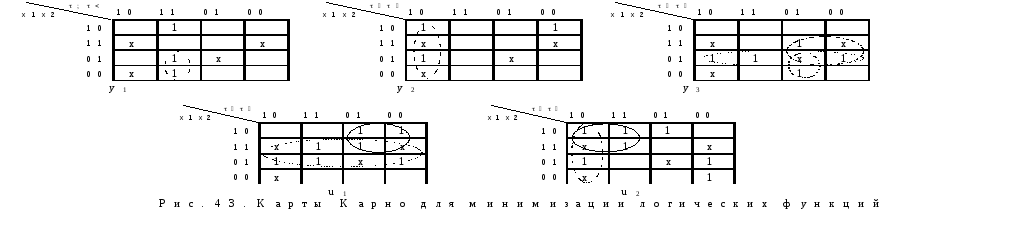

Д ля

упрощения комбинационной схемы выполним

минимизацию каждой из логических

функций. Для минимизации функций

используем метод минимизирующих карт

Карно. На рисунке 43 изображены 5 карт

Карно для минимизации каждой из пяти

логических функций

ля

упрощения комбинационной схемы выполним

минимизацию каждой из логических

функций. Для минимизации функций

используем метод минимизирующих карт

Карно. На рисунке 43 изображены 5 карт

Карно для минимизации каждой из пяти

логических функций

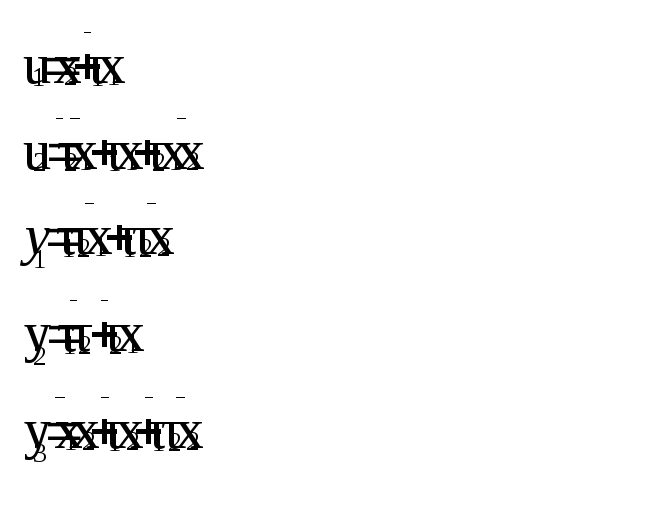

По результатам минимизации запишем

систему минимальных функций.

По результатам минимизации запишем

систему минимальных функций.

На

рис. 36. изображена логическая схема,

построенная для полученной системы

булевых функций. При построении схемы

использованы элементы ”И” и ”ИЛИ”.

На

рис. 36. изображена логическая схема,

построенная для полученной системы

булевых функций. При построении схемы

использованы элементы ”И” и ”ИЛИ”.