- •Цифровые эвм

- •§1.2 Структуры типичных микроЭвм

- •§1.3 Архитектура микро- и мини – эвм

- •§1.4 Архитектура эвм

- •§1.5 Ортогональность архитектуры микропроцессоров.

- •§2. Микропрограммные устройства управления §2.1 Структура микропрограммных устройств

- •§2.2 Способы записи микропрограмм

- •1) Гса должна содержать одну начальную, одну конечную вершину и конечное множество операторных и условных вершин;

- •2) Каждый выход гса соединяется только с одним входом;

- •3) Входы и выходы различных вершин соединяются дугами, направленными от выхода к входу;

- •4) Для любой вершины гса существует, по крайней мере, один путь из этой вершины к конечной вершине, проходящей через операторные и условные вершины в направлении соединяющих их дуг;

- •§2.3 Микропрограммный принцип управления операциями

- •1) Определение формата операционной части мк;

- •2) Синтез формата адресной части мк;

- •3) Синтез структурной схемы автомата;

- •4) Построение карты программирования пзу или плм.

- •§2.4 Синтез мпа с использованием “жёсткой” логики

- •2. Прибавить к содержимому сумматора первое частичное произведение.

- •3. К содержимому сумматора прибавить сдвинутое на разряд вправо второе частичное произведение.

- •4. Далее аналогично прибавить третье, четвертое и последующие частичные произведения.

- •§2.5 Выбор схемы операционного устройства

- •1) Два регистра (регистр множимого rg2 и регистр множителя rg1);

- •2) Сумматор (5м);

- •3) Счетчик (ст) для подсчета числа суммирований. На рис. 2.9 показаны обозначения этих узлов на схемах.

- •§3. Запоминающие устройства §3.1 Запоминающие устройства и их назначение

- •§3.2Классификация и основные характеристики полупроводниковых зу

- •§3.3 Статические озу

- •§3.4 Динамические озу

- •§3.5 Память на пзс

- •§3.7 Функциональные схемы озу

- •§3.8 Функциональные схемы пзу и ппзу

- •§3.9 Организация многокристальной памяти

- •§3.10 Программирование пзу

- •§3.11 Программируемые логические матрицы

- •§4. Процессоры и микропроцессоры §4.1Классификация микропроцессоров

- •§5.Сравнение архитектур микропроцессоров

- •§5.1 Архитектуры микропроцессоров.

- •§5.2 Ортогональность архитектуры микропроцессоров.

- •§5.3 Основные принципы построения устройств обработки цифровой информации

- •Существует два основных типа управляющих автоматов:

- •1) Управляющий автомат с жесткой логикой.

- •2) Управляющий автомат с хранимой в памяти логикой.

- •§5.4 Принципы организации арифметико – логических устройств.

- •§5.5 Классификация алу

- •1) Для чисел с фиксированной запятой;

- •2) Для чисел с плавающей запятой;

- •3) Для десятичных чисел.

- •§5.6 Структура и формат команд. Кодирование команд.

- •1) Команды арифметических операций для чисел с фиксированной и плавающей запятой;

- •§6.Проектирование микро - эвм

- •§6.1.Функциональные блоки и организация управления в микро - эвм §6.1.1Общие сведения

- •§6.1.2. Структура операционного устройства

- •§6.1.3. Структура устройства управления

- •1. Безусловный переход из адреса Ai по адресу Aj определенному одним из способов адресации (рис. 6.7,а).

- •Однокристальные эвм §7.Описание микроконтроллеров 8051, 8052 и 80c51 §7.1 Вступление

- •§7.2Специальные функциональные регистры

- •§7.3 Структура и работа портов

- •§7.3.1 Конфигурации ввода-вывода

- •§7.3.2 Запись в порт

- •§7.3.3 Загрузка и согласование портов.

- •§7.3.4 Особенность чтения-модификации-записи

- •§7.4.Доступ к внешней памяти

- •§7.5 Таймер/счетчик

- •Таймер 0 и Таймер 1

- •Режим 0 (mode 0)

- •М1 м0 Режим

- •§7.5 Последовательный интерфейс

- •§7.5.1 Многопроцессорные связи

- •§7.5.2 Управляющий регистр последовательного порта

- •§7.5.4 Скорость приема/передачи

- •§7.5.5Использование таймера 1 для задания скорости приема/передачи

- •Дополнительные сведения о режиме 0

- •Дополнительные сведения о режиме 1

- •Дополнительные сведения о режимах 2 и 3

- •Прерывания

- •§7.6 Структура уровней приоритета

- •Перехват прерываний

- •Внешние прерывания

- •Время отклика

- •Одношаговые операции

- •Версии микросхем с сппзу

- •Две схемы блокировки программной памяти

- •Защита пзу

- •Внутричиповые осцилляторы

- •Осцилляторах mcs-51

- •Внутренняя синхронизация

- •§8.1.Введение

- •§8.2. Обзор характеристик

- •Отличия pic16c84 от pic16c5x

- •Mаркировка при заказе

- •Разводка ножек

- •Прямая адресация.

- •Проблемы с таймером

- •Регистр статуса

- •Программные флаги статуса

- •Аппаратные флаги статуса

- •Организация встроенного пзу

- •Pc и адресация пзу

- •Стек и возвраты из подпрограмм

- •Данные в eeprom

- •Управление eeprom

- •Организация прерываний

- •Регистр запросов и масок

- •Внешнее прерывание

- •Прерывание от rtcc

- •Прерывание от порта rb

- •Прерывание от eeprom

- •Обзор регистров/портов

- •2) Прочитать порт в. Это завершит состояние сравнения.

- •Проблемы с портами

- •Обзор команд и обозначения

- •Условия сброса

- •Алгоритм сброса при вал. Питания

- •Watch Dog таймер

- •Типы генераторов.

- •Генератор на кварцах

- •Rc генератор.

- •Внешнее возбуждение. Регистр option

- •Подключения делителя частоты

- •1. Movlw b`xx0x0xxx` ;выбрать внутреннюю синхронизацию и новое

- •Конфигурационное слово

- •01 Xt генератор

- •10 Hs генератор

- •11 Rc генератор

- •Индивидуальная метка

- •Защита программ от считывания

- •1) Запрограммируйте и проверьте работу исправного кристалла.

- •2) Установите защиту кода программы и считайте содержимое программной памяти в файл-эталон.

- •3) Проверяйте любой защищенный кристалл путем сравнения его программной памяти с содержимым этого эталона.

- •Режим пониженного энергопотребления.

- •1. Внешний сброс - импульс низкого уровня на ножке /mclr.

- •2. Сброс при срабатывании wdt(если он разрешен)

- •3. Прерывания. (Прерывание с ножки int, прерывание при изменении порта b, прерывание при завершении записи данных eeprom).

- •Максимальные значения электрических параметров

- •1. Полная рассеиваемая мощность не должна превышать 800 мВт для каждого корпуса. Рассеиваемая мощность вычисляется по следующей формуле:

- •Скоростные характеристики:

- •§8.3. Что такое pic ?....

- •Hабор регистров pic

- •Регистр косвенной адресации ind0

- •Регистры общего назначения

- •Сторожевой таймер wdt

- •Тактовый геhератор

- •Xt кварцевый резонатор

- •От теории - к практике...

- •Initb equ b'00000000' ; ; Рабочая секция ; ; начало исполняемого кода

- •Пример программы

- •Ассемблироваhие

- •Программироваhие

- •Набор команд pic

- •Incf scratch,0 ;увеличить scratch на 1

- •Iorwf dataport,1 ;установить биты в поpте b по маске w

- •Iorlw 09h ;установить 0-й и 3-й биты Светодиоды покажут 00011001.

- •Xorlw b'11111111' ;пpоинвеpтиpовать w Светодиоды покажут 11011111.

- •Comf scratch,0 ;инвеpтиpовать scratch Светодиоды покажут 10101010.

- •Специальные команды

- •§9.Введение вAdsp §9.1. Обзор

- •§9.2. Функциональные устройства

- •§9.3. Интерфейс системы и памяти

- •§9.4. Набор команд

- •§9.5. Рабочие характеристики цифровых сигнальных процессоров

- •§9.6. Базовая архитектура

- •§9.7. Вычислительные устройства

- •§9.8. Генераторы адреса и программный автомат

- •§9.9. Шины

- •§9.10. Другие устройства на кристалле

- •§9.11. Последовательные порты

- •§9.12. Таймер

- •§9.13. Порт интерфейса хост-машины (adsp-2111, adsp-2171, adsp-21msp5x)

- •§9.14. Порты прямого доступа к памяти (adsp-2181)

- •§9.15. Аналоговый интерфейс

- •§9.16. Система программно – аппаратных средств отладки процессоров семействаAdsp - 2100

- •§9.17. Генераторы адреса и программный автомат

- •§10Вычислительные устройства §10.1. Обзор

- •Последовательности двоичных символов

- •Беззнаковый формат

- •Знаковые числа в дополнительном коде

- •§10.2. Арифметико – логическое устройство (алу)

- •Блок-схема алу

- •Стандартные функции

- •Регистры ввода/вывода алу

- •Возможность операций с повышенной точностью

- •Режим насыщения алу

- •Режим фиксации переполнения алу

- •Деление

- •§10.3. Умножитель – накопитель (умножитель)

- •Арифметические операции умножителя

- •Арифметические операции устройства сдвига

- •Операции умножителя-накопителя

- •X*y Умножение операндов х и y

- •Форматы ввода данных

- •Регистры ввода/вывода умножителя-накопителя

- •§10.4. Устройство циклического сдвига

- •Денормализация

- •Нормализация

- •§11. Управление программой

- •§11.1. Обзор

- •§11.2. Программный автомат

- •§11.3 Команды управления программой

- •§11.4. Контроллер прерываний

- •§11.5. Условные команды

- •§12. Дополнительное аппаратное обеспечение §12.1. Обзор

- •§12.2. Начальная загрузка через хост – машину с использованием процедур запроса и предоставления шины

- •1) Для перезапуска процессора семейства adsp-2100 pb8 устанавливается низким.

- •§12.4. Сопряжение последовательного порта с цап

- •§12.5. Сопряжение последовательного порта с ацп

- •§12.6. Сопряжение последовательного порта с другим последовательным портом

- •§12.7. Сопряжение микрокомпьютера 80с51 с портом интерфейса хост – машины

- •§12.8. Обзор

- •§13. Программное обеспечение §13.1. Процесс отладки системы

- •§14. Система команд мп типа к580ик80

- •§14.1 Способы адресации мп

- •§14.2 Команды мп

- •§14.3 Пояснения к некоторым командам

- •§15. Архитектура микропроцессора z-80

- •§15.1 Назначение выводов

- •§15.2 Логическая организацияZ80

- •Устройство управления.

- •Регистры пользователя (основные регистры).

- •Регистровая пара hl.

- •Набор альтернативных регистров.

- •Арифметико-логическое устройство (алу).

- •§15.3 Система команд микропроцессора z – 80. Команды и данные.

- •3. Двухбайтовый адрес (addv).

- •4. Однобайтовая константа смещения.

- •Группа команд

- •Группа 1. Команда «нет операции»

- •Группа 2. Команды загрузки регистра константами.

- •Группа 4.Команды загрузки регистров из памяти.

- •Группа 5.Команды записи в память содержимого регистра или константы.

- •Группа 6.Команды сложения.

- •Группа 7.Команды вычитания.

- •Группа 8.Команды сравнения.

- •Подгруппа b. Команда or.

- •Подгруппа c. Команда xor.

- •Группа 11. Команда стека.

- •2.Адрес addr затем записывается в счетчик команд, и выполняется программа.

- •3.По команде ret осуществляется возврат из программы.

- •§16.Микросхема 80130

- •§17.Микросхема 80186

- •§18.Микросхема 80286

- •Verr — Проверить доступ по считыванию

- •Verw — Проверить доступ по записи

- •Определение состояния цикла шины процессора 80286

- •§19.Микропрцессоры серииiX86 фирмы intel Выбор в программе на Ассемблере типа процессора

- •§19.1. Процессоры 80186 и 80188

- •Новые инструкции

- •Инструкции pusha и popa

- •Инструкции enter и leave

- •Инструкция bound

- •Инструкции ins и outs

- •Расширенные версии инструкций процессора 8086

- •Imul si,10 это просто сокращенная форма инструкции:

- •§19.2. Процессор 80286

- •§19.3. Процессор 80386

- •Новые типы сегментов

- •Новые регистры

- •Новые сегментные регистры

- •Новые режимы адресации

- •Процессор 80386, новые инструкции

- •Проверка битов

- •Просмотр битов

- •Преобразование данных типа dword или qword

- •Сдвиг нескольких слов

- •Условная установка битов

- •Загрузка регистров ss, fs и gs

- •Расширенные инструкции

- •Специальные версии инструкции mov

- •Новые версии инструкций loop и jcxz

- •Новые версии строковых инструкций

- •Инструкция iretd

- •Инструкции pushfd и popfd

- •Инструкции pushad и popad

- •Новые версии инструкции imul

- •Imul ebp,ecx,100000000h а следующая инструкция умножает ecx на ebx, записывая результат в edx:eax:

- •Технический обзор Новое поколение процессоров фирмы intel

- •Pentium процессор. Технические нововведения.

- •Архитектура Pentium процессора

- •Суперскалярная архитектура.

- •Блок предсказания правильного адреса перехода.

- •Высокопроизводительный блок вычислений с плавающей запятой.

- •Расширенная 64-битовая шина данных.

- •Средства разделения памяти на страницы.

- •Определение ошибок и функциональная избыточность.

- •Управление производительностью.

- •§22.Введение в команды mmx.

- •§22.1. Регистры

- •§22.2. Префиксы

- •§22.3.Распаровка (paring).

- •§22.4. Типы данных

- •§22.5. Краткое описание команд

- •§23.Логическая структура микропроцессорной системы на основе комплекта бис секционного микропроцессора §23.1. Комплект бис секционного микропроцессора.

- •§23.2. Бис микропрограммного управления на основе программируемой логической матрицы (плм).

- •§23.3. Комплект бис для построения электронной системы.

- •§24. Обзор секционируемых мпк бис §24.1. Микропроцессорный комплект серии кр1802

- •§24.1.1. Восьмиразрядная микропроцессорная секция (мс) кр1802вс1.

- •§24.1.2. Двухадресная память общего назначения кр1802ир1.

- •§24.1.3. Шестнадцатиразрядный арифметический расширитель кр1802вр1.

- •§24.1.4. Схема обмена информацией (ои) кр1802вв1.

- •§24.1.5. Бис интерфейса (бис и) кр1802вв2.

- •§24.1.6. Сумматор (см) к1802им1.

- •§24.1.7. Км1802врз—умножитель двух 8-разрядных чисел.

- •§24.1.8. Км1802вр4—умножитель двух 12-разрядных чисел.

- •§24.1.9. Км1802вр5—умножитель двух 16-разрядных чисел.

- •§24.2. Микропроцессорный комплект серии к1804

- •§24.2.1. Центральные процессорные элементы к1804вс1 и к1804вс2

- •§24.3. Микропроцессорный комплект серии к587 §24.3.1. Арифметическое устройство к587ик2.

- •§24.3.2. Управляющая память к587рп1.

- •§24.3.3. Устройство обмена информации к587ик1.

- •§24.3.4. Арифметический расширитель к587икз.

- •§24.3.5. Архитектурные особенности построения управляющей микро-эвм на базе мпк серии к587

§12.4. Сопряжение последовательного порта с цап

Любой процесс цифровой обработки сигнала в конце концов должен заканчиваться выводом информации в аналоговой форме.

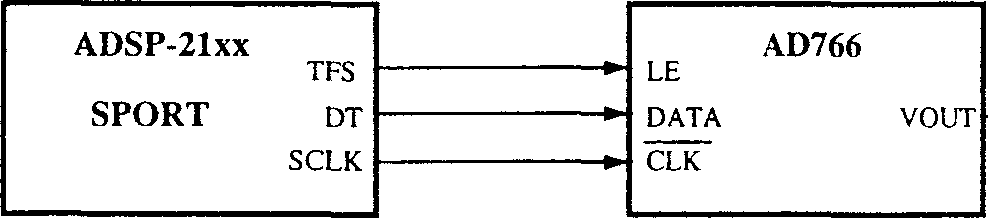

Последовательный порт процессоров семейства ADSP-2100 может непосредственно посылать данные на ЦАП (цифро-аналоговый преобразователь) для их последующего преобразования в аналоговый сигнал.

ЦАП фирмы Analog Devices AD766 не требует никаких дополнительных логических устройств для сопряжения с последовательным портом. AD766 полу чает слова данных длиной 16 бит начиная с самого старшего бита и преобразует их в аналоговый сигнал. Цифровой интерфейс этого преобразователя состоит из трех входов: DATA - вход последовательных данных; CLK для сигнала синхронизации данных в ЦАП (активен по низкому уровню, так как данные синхронизируются по заднему фронту) и LE (разрешение фиксации), который фиксирует каждое 16-разрядное слово данных в преобразующей части ЦАП.

Соединение последовательного порта с AD766 показано на рис. 12.3. В данной конфигурации процессор внутренне генерирует последовательные тактовые синхроимпульсы SCLK и подает их на ЦАП. Данные последовательно выводятся через вывод DT процессора на вход DATA ЦАП. На вход ЦАП LE подается сигнал кадровой синхронизации передачи TFS.

Рис. 12.3 Сопряжение последовательного порта с ЦАП AD766

В цикле тактового генератора после передачи самого младшего (шестнадцатого) бита слова на вход LE должен быть подан низкий уровень, чтобы 16-разрядное слово было зафиксировано в ЦАП. Для обеспечения временного согласования этого процесса сигнал TFS задается неинвертируемым для альтернативного режима кадровой синхронизации; этот сигнал имеет высокий уровень во время передачи первого бита и низкий уровень после передачи последнего бита. Таким образом, слово фиксируется в AD766 по заднему фронту этого сигнала. Единственным ограничением является то, что последовательный порт не может передавать данные беспрерывно; между последним битом одного слова и первым битом следующего слова должен быть перерыв, необходимый для понижения уровня сигнала TFS.

Регистр управления SPORTO: Ox3FF6 Регистр управления SPORT I: Ox3FF2

Рис. 12.4 Установки регистра управления для сопряжения последовательного порта с АЦП AD7872

На рис. 12.5 показана конфигурация регистров управления последовательного порта для рассматриваемого примера.

Регистр управления SPORTO: Ox3FF6 Регистр управления SPORT1: Ox3FF2

Рис. 12.5 Установки регистров управления для сопряжения последовательного порта с ЦАП

§12.5. Сопряжение последовательного порта с ацп

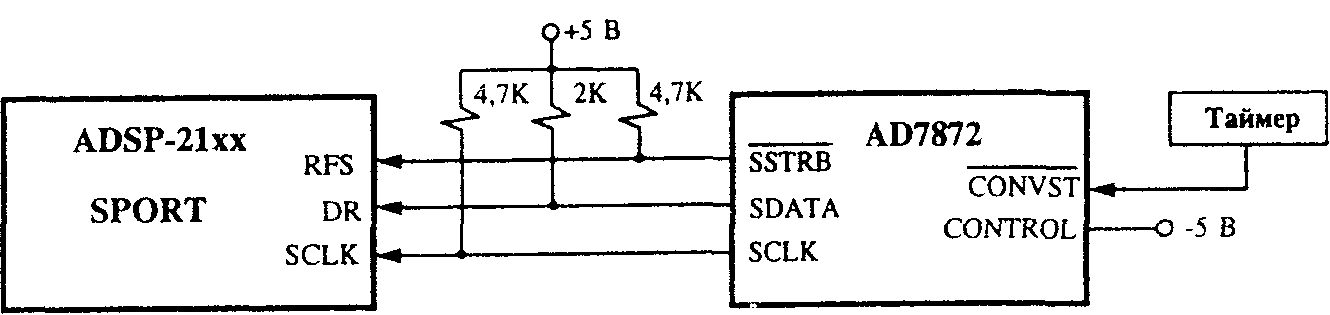

АЦП (аналого-цифровой преобразователь) преобразует аналоговый сигнал в цифровые выборки, пригодные для обработки цифровым сигнальным процессором. Процессоры семейства ADSP-2100 могут непосредственно получать данные с АЦП через последовательный порт.

АЦП фирмы Analog Devices AD7872 не требует никаких дополнительных логических устройств для сопряжения с последовательным портом. AD7872 преобразует аналоговый сигнал в 14-разрядные выборки. Каждая выборка дополняется двумя самыми старшими битами равными нулю для формирования 16-разрядных слов. AD7872 выводит слово последовательно, начиная с самого старшего бита. Цифровой интерфейс этого АЦП состоит из трех выводов: SDATA - вывод последовательных данных; SCLK - для синхронизации данных при их выводе и SSTRB (последовательный строб), который осуществляет кадровую синхронизацию каждого последовательно передаваемого слова.

С оединение

последовательного порта сAD7872

показано на рис. 12.6. Таймер регулирует

выборки с постоянной частотой посредством

входного сигнала CONVST

. Неиспользуемый последовательный порт

или вывод флага процессора семейства

ADSP-2100 могут быть запрограммированы для

генерирования сигнала CONVST

вместо таймера. AD7872 внутренне генерирует

последовательные тактовые синхроимпульсы

SCLK и подает их на процессор. При

удерживаемом на входе

CONTROL напряжении -5В сигнал SCLK

является непрерывным и генерируется

даже после вывода данных.

оединение

последовательного порта сAD7872

показано на рис. 12.6. Таймер регулирует

выборки с постоянной частотой посредством

входного сигнала CONVST

. Неиспользуемый последовательный порт

или вывод флага процессора семейства

ADSP-2100 могут быть запрограммированы для

генерирования сигнала CONVST

вместо таймера. AD7872 внутренне генерирует

последовательные тактовые синхроимпульсы

SCLK и подает их на процессор. При

удерживаемом на входе

CONTROL напряжении -5В сигнал SCLK

является непрерывным и генерируется

даже после вывода данных.

Рис. 12.6 Сопряжение последовательного порта с АЦП AD7872

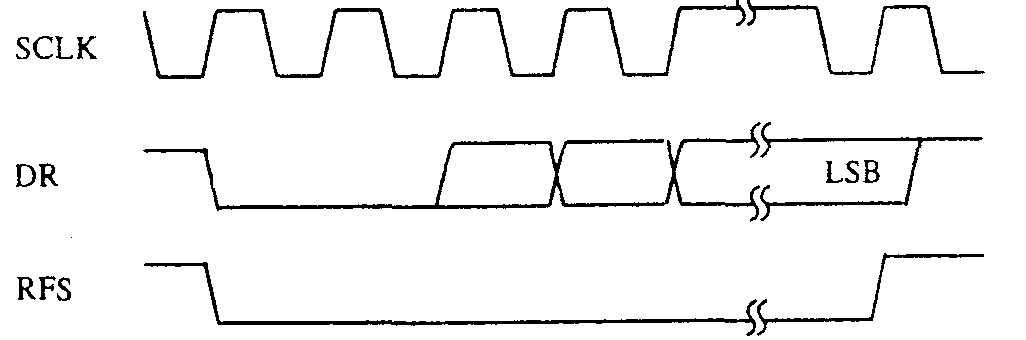

Д анные

последовательно выводятся через выход

SDATA АЦП на вход процессора

DR. Сигнал SSTRB используется как

входной сигнал кадровой синхронизации

приема. Сигнал SSTRB устанавливается в 0

во время передачи первого бита на

процессор. Временные характеристики

передачи данных показаны на рис.12.7.

анные

последовательно выводятся через выход

SDATA АЦП на вход процессора

DR. Сигнал SSTRB используется как

входной сигнал кадровой синхронизации

приема. Сигнал SSTRB устанавливается в 0

во время передачи первого бита на

процессор. Временные характеристики

передачи данных показаны на рис.12.7.

, MSB(O) О

Рис. 12.7 Временные характеристики передачи с AD7872 на последовательный порт

Сигнал кадровой синхронизации приема настраивается при инициализации как генерируемый внешне с инвертированной логикой (активным по низкому уровню) для альтернативного режима кадровой синхронизации. Последовательный порт также должен быть запрограммирован для работы с внешне генерируемыми тактовыми синхроимпульсами и словами данных длиной 16 бит. На рис. 12.4 показана конфигурация регистра управления последовательным портом, необходимая для его использования при сопряжении с данным АЦП.