- •Цифровые эвм

- •§1.2 Структуры типичных микроЭвм

- •§1.3 Архитектура микро- и мини – эвм

- •§1.4 Архитектура эвм

- •§1.5 Ортогональность архитектуры микропроцессоров.

- •§2. Микропрограммные устройства управления §2.1 Структура микропрограммных устройств

- •§2.2 Способы записи микропрограмм

- •1) Гса должна содержать одну начальную, одну конечную вершину и конечное множество операторных и условных вершин;

- •2) Каждый выход гса соединяется только с одним входом;

- •3) Входы и выходы различных вершин соединяются дугами, направленными от выхода к входу;

- •4) Для любой вершины гса существует, по крайней мере, один путь из этой вершины к конечной вершине, проходящей через операторные и условные вершины в направлении соединяющих их дуг;

- •§2.3 Микропрограммный принцип управления операциями

- •1) Определение формата операционной части мк;

- •2) Синтез формата адресной части мк;

- •3) Синтез структурной схемы автомата;

- •4) Построение карты программирования пзу или плм.

- •§2.4 Синтез мпа с использованием “жёсткой” логики

- •2. Прибавить к содержимому сумматора первое частичное произведение.

- •3. К содержимому сумматора прибавить сдвинутое на разряд вправо второе частичное произведение.

- •4. Далее аналогично прибавить третье, четвертое и последующие частичные произведения.

- •§2.5 Выбор схемы операционного устройства

- •1) Два регистра (регистр множимого rg2 и регистр множителя rg1);

- •2) Сумматор (5м);

- •3) Счетчик (ст) для подсчета числа суммирований. На рис. 2.9 показаны обозначения этих узлов на схемах.

- •§3. Запоминающие устройства §3.1 Запоминающие устройства и их назначение

- •§3.2Классификация и основные характеристики полупроводниковых зу

- •§3.3 Статические озу

- •§3.4 Динамические озу

- •§3.5 Память на пзс

- •§3.7 Функциональные схемы озу

- •§3.8 Функциональные схемы пзу и ппзу

- •§3.9 Организация многокристальной памяти

- •§3.10 Программирование пзу

- •§3.11 Программируемые логические матрицы

- •§4. Процессоры и микропроцессоры §4.1Классификация микропроцессоров

- •§5.Сравнение архитектур микропроцессоров

- •§5.1 Архитектуры микропроцессоров.

- •§5.2 Ортогональность архитектуры микропроцессоров.

- •§5.3 Основные принципы построения устройств обработки цифровой информации

- •Существует два основных типа управляющих автоматов:

- •1) Управляющий автомат с жесткой логикой.

- •2) Управляющий автомат с хранимой в памяти логикой.

- •§5.4 Принципы организации арифметико – логических устройств.

- •§5.5 Классификация алу

- •1) Для чисел с фиксированной запятой;

- •2) Для чисел с плавающей запятой;

- •3) Для десятичных чисел.

- •§5.6 Структура и формат команд. Кодирование команд.

- •1) Команды арифметических операций для чисел с фиксированной и плавающей запятой;

- •§6.Проектирование микро - эвм

- •§6.1.Функциональные блоки и организация управления в микро - эвм §6.1.1Общие сведения

- •§6.1.2. Структура операционного устройства

- •§6.1.3. Структура устройства управления

- •1. Безусловный переход из адреса Ai по адресу Aj определенному одним из способов адресации (рис. 6.7,а).

- •Однокристальные эвм §7.Описание микроконтроллеров 8051, 8052 и 80c51 §7.1 Вступление

- •§7.2Специальные функциональные регистры

- •§7.3 Структура и работа портов

- •§7.3.1 Конфигурации ввода-вывода

- •§7.3.2 Запись в порт

- •§7.3.3 Загрузка и согласование портов.

- •§7.3.4 Особенность чтения-модификации-записи

- •§7.4.Доступ к внешней памяти

- •§7.5 Таймер/счетчик

- •Таймер 0 и Таймер 1

- •Режим 0 (mode 0)

- •М1 м0 Режим

- •§7.5 Последовательный интерфейс

- •§7.5.1 Многопроцессорные связи

- •§7.5.2 Управляющий регистр последовательного порта

- •§7.5.4 Скорость приема/передачи

- •§7.5.5Использование таймера 1 для задания скорости приема/передачи

- •Дополнительные сведения о режиме 0

- •Дополнительные сведения о режиме 1

- •Дополнительные сведения о режимах 2 и 3

- •Прерывания

- •§7.6 Структура уровней приоритета

- •Перехват прерываний

- •Внешние прерывания

- •Время отклика

- •Одношаговые операции

- •Версии микросхем с сппзу

- •Две схемы блокировки программной памяти

- •Защита пзу

- •Внутричиповые осцилляторы

- •Осцилляторах mcs-51

- •Внутренняя синхронизация

- •§8.1.Введение

- •§8.2. Обзор характеристик

- •Отличия pic16c84 от pic16c5x

- •Mаркировка при заказе

- •Разводка ножек

- •Прямая адресация.

- •Проблемы с таймером

- •Регистр статуса

- •Программные флаги статуса

- •Аппаратные флаги статуса

- •Организация встроенного пзу

- •Pc и адресация пзу

- •Стек и возвраты из подпрограмм

- •Данные в eeprom

- •Управление eeprom

- •Организация прерываний

- •Регистр запросов и масок

- •Внешнее прерывание

- •Прерывание от rtcc

- •Прерывание от порта rb

- •Прерывание от eeprom

- •Обзор регистров/портов

- •2) Прочитать порт в. Это завершит состояние сравнения.

- •Проблемы с портами

- •Обзор команд и обозначения

- •Условия сброса

- •Алгоритм сброса при вал. Питания

- •Watch Dog таймер

- •Типы генераторов.

- •Генератор на кварцах

- •Rc генератор.

- •Внешнее возбуждение. Регистр option

- •Подключения делителя частоты

- •1. Movlw b`xx0x0xxx` ;выбрать внутреннюю синхронизацию и новое

- •Конфигурационное слово

- •01 Xt генератор

- •10 Hs генератор

- •11 Rc генератор

- •Индивидуальная метка

- •Защита программ от считывания

- •1) Запрограммируйте и проверьте работу исправного кристалла.

- •2) Установите защиту кода программы и считайте содержимое программной памяти в файл-эталон.

- •3) Проверяйте любой защищенный кристалл путем сравнения его программной памяти с содержимым этого эталона.

- •Режим пониженного энергопотребления.

- •1. Внешний сброс - импульс низкого уровня на ножке /mclr.

- •2. Сброс при срабатывании wdt(если он разрешен)

- •3. Прерывания. (Прерывание с ножки int, прерывание при изменении порта b, прерывание при завершении записи данных eeprom).

- •Максимальные значения электрических параметров

- •1. Полная рассеиваемая мощность не должна превышать 800 мВт для каждого корпуса. Рассеиваемая мощность вычисляется по следующей формуле:

- •Скоростные характеристики:

- •§8.3. Что такое pic ?....

- •Hабор регистров pic

- •Регистр косвенной адресации ind0

- •Регистры общего назначения

- •Сторожевой таймер wdt

- •Тактовый геhератор

- •Xt кварцевый резонатор

- •От теории - к практике...

- •Initb equ b'00000000' ; ; Рабочая секция ; ; начало исполняемого кода

- •Пример программы

- •Ассемблироваhие

- •Программироваhие

- •Набор команд pic

- •Incf scratch,0 ;увеличить scratch на 1

- •Iorwf dataport,1 ;установить биты в поpте b по маске w

- •Iorlw 09h ;установить 0-й и 3-й биты Светодиоды покажут 00011001.

- •Xorlw b'11111111' ;пpоинвеpтиpовать w Светодиоды покажут 11011111.

- •Comf scratch,0 ;инвеpтиpовать scratch Светодиоды покажут 10101010.

- •Специальные команды

- •§9.Введение вAdsp §9.1. Обзор

- •§9.2. Функциональные устройства

- •§9.3. Интерфейс системы и памяти

- •§9.4. Набор команд

- •§9.5. Рабочие характеристики цифровых сигнальных процессоров

- •§9.6. Базовая архитектура

- •§9.7. Вычислительные устройства

- •§9.8. Генераторы адреса и программный автомат

- •§9.9. Шины

- •§9.10. Другие устройства на кристалле

- •§9.11. Последовательные порты

- •§9.12. Таймер

- •§9.13. Порт интерфейса хост-машины (adsp-2111, adsp-2171, adsp-21msp5x)

- •§9.14. Порты прямого доступа к памяти (adsp-2181)

- •§9.15. Аналоговый интерфейс

- •§9.16. Система программно – аппаратных средств отладки процессоров семействаAdsp - 2100

- •§9.17. Генераторы адреса и программный автомат

- •§10Вычислительные устройства §10.1. Обзор

- •Последовательности двоичных символов

- •Беззнаковый формат

- •Знаковые числа в дополнительном коде

- •§10.2. Арифметико – логическое устройство (алу)

- •Блок-схема алу

- •Стандартные функции

- •Регистры ввода/вывода алу

- •Возможность операций с повышенной точностью

- •Режим насыщения алу

- •Режим фиксации переполнения алу

- •Деление

- •§10.3. Умножитель – накопитель (умножитель)

- •Арифметические операции умножителя

- •Арифметические операции устройства сдвига

- •Операции умножителя-накопителя

- •X*y Умножение операндов х и y

- •Форматы ввода данных

- •Регистры ввода/вывода умножителя-накопителя

- •§10.4. Устройство циклического сдвига

- •Денормализация

- •Нормализация

- •§11. Управление программой

- •§11.1. Обзор

- •§11.2. Программный автомат

- •§11.3 Команды управления программой

- •§11.4. Контроллер прерываний

- •§11.5. Условные команды

- •§12. Дополнительное аппаратное обеспечение §12.1. Обзор

- •§12.2. Начальная загрузка через хост – машину с использованием процедур запроса и предоставления шины

- •1) Для перезапуска процессора семейства adsp-2100 pb8 устанавливается низким.

- •§12.4. Сопряжение последовательного порта с цап

- •§12.5. Сопряжение последовательного порта с ацп

- •§12.6. Сопряжение последовательного порта с другим последовательным портом

- •§12.7. Сопряжение микрокомпьютера 80с51 с портом интерфейса хост – машины

- •§12.8. Обзор

- •§13. Программное обеспечение §13.1. Процесс отладки системы

- •§14. Система команд мп типа к580ик80

- •§14.1 Способы адресации мп

- •§14.2 Команды мп

- •§14.3 Пояснения к некоторым командам

- •§15. Архитектура микропроцессора z-80

- •§15.1 Назначение выводов

- •§15.2 Логическая организацияZ80

- •Устройство управления.

- •Регистры пользователя (основные регистры).

- •Регистровая пара hl.

- •Набор альтернативных регистров.

- •Арифметико-логическое устройство (алу).

- •§15.3 Система команд микропроцессора z – 80. Команды и данные.

- •3. Двухбайтовый адрес (addv).

- •4. Однобайтовая константа смещения.

- •Группа команд

- •Группа 1. Команда «нет операции»

- •Группа 2. Команды загрузки регистра константами.

- •Группа 4.Команды загрузки регистров из памяти.

- •Группа 5.Команды записи в память содержимого регистра или константы.

- •Группа 6.Команды сложения.

- •Группа 7.Команды вычитания.

- •Группа 8.Команды сравнения.

- •Подгруппа b. Команда or.

- •Подгруппа c. Команда xor.

- •Группа 11. Команда стека.

- •2.Адрес addr затем записывается в счетчик команд, и выполняется программа.

- •3.По команде ret осуществляется возврат из программы.

- •§16.Микросхема 80130

- •§17.Микросхема 80186

- •§18.Микросхема 80286

- •Verr — Проверить доступ по считыванию

- •Verw — Проверить доступ по записи

- •Определение состояния цикла шины процессора 80286

- •§19.Микропрцессоры серииiX86 фирмы intel Выбор в программе на Ассемблере типа процессора

- •§19.1. Процессоры 80186 и 80188

- •Новые инструкции

- •Инструкции pusha и popa

- •Инструкции enter и leave

- •Инструкция bound

- •Инструкции ins и outs

- •Расширенные версии инструкций процессора 8086

- •Imul si,10 это просто сокращенная форма инструкции:

- •§19.2. Процессор 80286

- •§19.3. Процессор 80386

- •Новые типы сегментов

- •Новые регистры

- •Новые сегментные регистры

- •Новые режимы адресации

- •Процессор 80386, новые инструкции

- •Проверка битов

- •Просмотр битов

- •Преобразование данных типа dword или qword

- •Сдвиг нескольких слов

- •Условная установка битов

- •Загрузка регистров ss, fs и gs

- •Расширенные инструкции

- •Специальные версии инструкции mov

- •Новые версии инструкций loop и jcxz

- •Новые версии строковых инструкций

- •Инструкция iretd

- •Инструкции pushfd и popfd

- •Инструкции pushad и popad

- •Новые версии инструкции imul

- •Imul ebp,ecx,100000000h а следующая инструкция умножает ecx на ebx, записывая результат в edx:eax:

- •Технический обзор Новое поколение процессоров фирмы intel

- •Pentium процессор. Технические нововведения.

- •Архитектура Pentium процессора

- •Суперскалярная архитектура.

- •Блок предсказания правильного адреса перехода.

- •Высокопроизводительный блок вычислений с плавающей запятой.

- •Расширенная 64-битовая шина данных.

- •Средства разделения памяти на страницы.

- •Определение ошибок и функциональная избыточность.

- •Управление производительностью.

- •§22.Введение в команды mmx.

- •§22.1. Регистры

- •§22.2. Префиксы

- •§22.3.Распаровка (paring).

- •§22.4. Типы данных

- •§22.5. Краткое описание команд

- •§23.Логическая структура микропроцессорной системы на основе комплекта бис секционного микропроцессора §23.1. Комплект бис секционного микропроцессора.

- •§23.2. Бис микропрограммного управления на основе программируемой логической матрицы (плм).

- •§23.3. Комплект бис для построения электронной системы.

- •§24. Обзор секционируемых мпк бис §24.1. Микропроцессорный комплект серии кр1802

- •§24.1.1. Восьмиразрядная микропроцессорная секция (мс) кр1802вс1.

- •§24.1.2. Двухадресная память общего назначения кр1802ир1.

- •§24.1.3. Шестнадцатиразрядный арифметический расширитель кр1802вр1.

- •§24.1.4. Схема обмена информацией (ои) кр1802вв1.

- •§24.1.5. Бис интерфейса (бис и) кр1802вв2.

- •§24.1.6. Сумматор (см) к1802им1.

- •§24.1.7. Км1802врз—умножитель двух 8-разрядных чисел.

- •§24.1.8. Км1802вр4—умножитель двух 12-разрядных чисел.

- •§24.1.9. Км1802вр5—умножитель двух 16-разрядных чисел.

- •§24.2. Микропроцессорный комплект серии к1804

- •§24.2.1. Центральные процессорные элементы к1804вс1 и к1804вс2

- •§24.3. Микропроцессорный комплект серии к587 §24.3.1. Арифметическое устройство к587ик2.

- •§24.3.2. Управляющая память к587рп1.

- •§24.3.3. Устройство обмена информации к587ик1.

- •§24.3.4. Арифметический расширитель к587икз.

- •§24.3.5. Архитектурные особенности построения управляющей микро-эвм на базе мпк серии к587

§7.3.2 Запись в порт

При выполнении инструкций, которые изменяют значение регистра порта, новое значение появляется в регистре во время S6P2 (step 6 phase 2) финального цикла инструкции. Реально, регистры портов отображают выходные буферы только во время фазы 1 любого такта. (во время фазы 2 выходные буферы содержат значение, которое было в них во время фазы 1). Следовательно, новое значение появится в регистре только со следующей фазой 1, которая будет с наступлением S1P1 следующего машинного цикла .

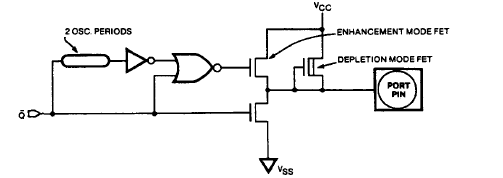

Если новое значение требует перевода типа 0-в-1, в портах 1, 2 и 3 подключается дополнительная нагрузка во время S1P1 и S1P2 цикла, в котором идет передача. Это необходимо для увеличения скорости передачи. Дополнительный нагрузка может дать ток в 100 раз больший, чем обычная. Следует помнить, что в роли внутренних нагрузок выступают полевые транзисторы, а не линейные резисторы. Классификация нагрузки приведена на рис. 7.5.

В HMOS версии микросхем 8051 постоянной частью нагрузки является обедненный полевой транзистор у которого затвор соединен с истоком. Этот транзистор позволяет контакту давать ток в 0.25мА при его заземлении. В то же время там находится и обогащенный полевой транзистор, который открывается во время S1 всякий раз при переходе бита порта 0-в-1. Если в это время контакт порта закорочен на землю, этот дополнительный транзистор позволяет контакту давать дополнительные 30мА.

а)

Конфигурация

HMOS.

Транзистор, работающий в обогащенном

режиме включается на 2 периода осциллятора

после перехода

0-в-1 на

Q#.

а)

Конфигурация

HMOS.

Транзистор, работающий в обогащенном

режиме включается на 2 периода осциллятора

после перехода

0-в-1 на

Q#.

б)

Конфигурация CHMOS. Транзистор

Р1 открывается на 2 периода осциллятора

после

перехода

0-в-1 на

Q#. В это же время P1 открывает через

инвертор и Р3 для фиксации 1. Р2 также

открыт.

б)

Конфигурация CHMOS. Транзистор

Р1 открывается на 2 периода осциллятора

после

перехода

0-в-1 на

Q#. В это же время P1 открывает через

инвертор и Р3 для фиксации 1. Р2 также

открыт.

Рисунок 7.5. Внутренние нагрузочные конфигурации HMOS и CHMOS портов 1 и 3. Конфигурация порта 2 аналогичная, за исключением высокой нагрузки при выдаче 1-цы адресного бита.

В CHMOS версиях нагрузка состоит из 3-х полевых транзисторов p-типа. Следует помнить, что транзисторы с каналом n-типа открываются когда логическая «1» подается на затвор и закрывается, когда туда подается «0». У транзисторов с каналом p-типа ситуация обратная.

Транзистор P1 на рис. 7.5 открывается на 2 периода осциллятора после перехода 0-в-1 в регистре порта. Когда он открыт, через инвертор открывается и транзистор P3 (низкая нагрузка). Этот инвертор и транзисторы p-типа образуют защелку, которая удерживает «1».

Обратите внимание, что если на выходе контакта порта находится «1», проблемы на контакте от внешнего источника могут закрыть транзистор P3, что переведет контакт в холостой режим. Транзистор P2 – очень слабая нагрузка. Он будет открываться всякий раз, когда транзистор n-типа будет закрываться (как в обычной КМОП-структуре). Его назначение – восстанавливать значение «1» на контакте в случае если на контакте была «1» и она была утеряна в следствие внешней проблемы.

§7.3.3 Загрузка и согласование портов.

Выходные буфера портов 1, 2 и 3 могут управлять 4-мя LS TTL входами каждый. В HMOS версиях эти порты могут управляться обычным способом любой TTL или nМОП схемой. И HMOS и CHMOS контакты могут управляться открыто-коллекторными и открыто-стоковыми выходами, но при этом переход 0-в-1 не будет быстрым. В HMOS-устройстве, если контакт управляется открыто-коллекторным выходом, переход 0-в-1 будет управляться относительно слабым обедненным режимом транзисторов (рис.7.5 “a”). В CHMOS устройстве, «0» на входе закрывает транзистор P3, оставляя только очень слабую нагрузку P2 для управления переходом.

В режиме внешней шины, выходные буферы порта 0 могут управлять 8-мью LS TTL входами каждый. Как и контакты порта, они требуют внешней нагрузки для управления входом.