- •Цифровые эвм

- •§1.2 Структуры типичных микроЭвм

- •§1.3 Архитектура микро- и мини – эвм

- •§1.4 Архитектура эвм

- •§1.5 Ортогональность архитектуры микропроцессоров.

- •§2. Микропрограммные устройства управления §2.1 Структура микропрограммных устройств

- •§2.2 Способы записи микропрограмм

- •1) Гса должна содержать одну начальную, одну конечную вершину и конечное множество операторных и условных вершин;

- •2) Каждый выход гса соединяется только с одним входом;

- •3) Входы и выходы различных вершин соединяются дугами, направленными от выхода к входу;

- •4) Для любой вершины гса существует, по крайней мере, один путь из этой вершины к конечной вершине, проходящей через операторные и условные вершины в направлении соединяющих их дуг;

- •§2.3 Микропрограммный принцип управления операциями

- •1) Определение формата операционной части мк;

- •2) Синтез формата адресной части мк;

- •3) Синтез структурной схемы автомата;

- •4) Построение карты программирования пзу или плм.

- •§2.4 Синтез мпа с использованием “жёсткой” логики

- •2. Прибавить к содержимому сумматора первое частичное произведение.

- •3. К содержимому сумматора прибавить сдвинутое на разряд вправо второе частичное произведение.

- •4. Далее аналогично прибавить третье, четвертое и последующие частичные произведения.

- •§2.5 Выбор схемы операционного устройства

- •1) Два регистра (регистр множимого rg2 и регистр множителя rg1);

- •2) Сумматор (5м);

- •3) Счетчик (ст) для подсчета числа суммирований. На рис. 2.9 показаны обозначения этих узлов на схемах.

- •§3. Запоминающие устройства §3.1 Запоминающие устройства и их назначение

- •§3.2Классификация и основные характеристики полупроводниковых зу

- •§3.3 Статические озу

- •§3.4 Динамические озу

- •§3.5 Память на пзс

- •§3.7 Функциональные схемы озу

- •§3.8 Функциональные схемы пзу и ппзу

- •§3.9 Организация многокристальной памяти

- •§3.10 Программирование пзу

- •§3.11 Программируемые логические матрицы

- •§4. Процессоры и микропроцессоры §4.1Классификация микропроцессоров

- •§5.Сравнение архитектур микропроцессоров

- •§5.1 Архитектуры микропроцессоров.

- •§5.2 Ортогональность архитектуры микропроцессоров.

- •§5.3 Основные принципы построения устройств обработки цифровой информации

- •Существует два основных типа управляющих автоматов:

- •1) Управляющий автомат с жесткой логикой.

- •2) Управляющий автомат с хранимой в памяти логикой.

- •§5.4 Принципы организации арифметико – логических устройств.

- •§5.5 Классификация алу

- •1) Для чисел с фиксированной запятой;

- •2) Для чисел с плавающей запятой;

- •3) Для десятичных чисел.

- •§5.6 Структура и формат команд. Кодирование команд.

- •1) Команды арифметических операций для чисел с фиксированной и плавающей запятой;

- •§6.Проектирование микро - эвм

- •§6.1.Функциональные блоки и организация управления в микро - эвм §6.1.1Общие сведения

- •§6.1.2. Структура операционного устройства

- •§6.1.3. Структура устройства управления

- •1. Безусловный переход из адреса Ai по адресу Aj определенному одним из способов адресации (рис. 6.7,а).

- •Однокристальные эвм §7.Описание микроконтроллеров 8051, 8052 и 80c51 §7.1 Вступление

- •§7.2Специальные функциональные регистры

- •§7.3 Структура и работа портов

- •§7.3.1 Конфигурации ввода-вывода

- •§7.3.2 Запись в порт

- •§7.3.3 Загрузка и согласование портов.

- •§7.3.4 Особенность чтения-модификации-записи

- •§7.4.Доступ к внешней памяти

- •§7.5 Таймер/счетчик

- •Таймер 0 и Таймер 1

- •Режим 0 (mode 0)

- •М1 м0 Режим

- •§7.5 Последовательный интерфейс

- •§7.5.1 Многопроцессорные связи

- •§7.5.2 Управляющий регистр последовательного порта

- •§7.5.4 Скорость приема/передачи

- •§7.5.5Использование таймера 1 для задания скорости приема/передачи

- •Дополнительные сведения о режиме 0

- •Дополнительные сведения о режиме 1

- •Дополнительные сведения о режимах 2 и 3

- •Прерывания

- •§7.6 Структура уровней приоритета

- •Перехват прерываний

- •Внешние прерывания

- •Время отклика

- •Одношаговые операции

- •Версии микросхем с сппзу

- •Две схемы блокировки программной памяти

- •Защита пзу

- •Внутричиповые осцилляторы

- •Осцилляторах mcs-51

- •Внутренняя синхронизация

- •§8.1.Введение

- •§8.2. Обзор характеристик

- •Отличия pic16c84 от pic16c5x

- •Mаркировка при заказе

- •Разводка ножек

- •Прямая адресация.

- •Проблемы с таймером

- •Регистр статуса

- •Программные флаги статуса

- •Аппаратные флаги статуса

- •Организация встроенного пзу

- •Pc и адресация пзу

- •Стек и возвраты из подпрограмм

- •Данные в eeprom

- •Управление eeprom

- •Организация прерываний

- •Регистр запросов и масок

- •Внешнее прерывание

- •Прерывание от rtcc

- •Прерывание от порта rb

- •Прерывание от eeprom

- •Обзор регистров/портов

- •2) Прочитать порт в. Это завершит состояние сравнения.

- •Проблемы с портами

- •Обзор команд и обозначения

- •Условия сброса

- •Алгоритм сброса при вал. Питания

- •Watch Dog таймер

- •Типы генераторов.

- •Генератор на кварцах

- •Rc генератор.

- •Внешнее возбуждение. Регистр option

- •Подключения делителя частоты

- •1. Movlw b`xx0x0xxx` ;выбрать внутреннюю синхронизацию и новое

- •Конфигурационное слово

- •01 Xt генератор

- •10 Hs генератор

- •11 Rc генератор

- •Индивидуальная метка

- •Защита программ от считывания

- •1) Запрограммируйте и проверьте работу исправного кристалла.

- •2) Установите защиту кода программы и считайте содержимое программной памяти в файл-эталон.

- •3) Проверяйте любой защищенный кристалл путем сравнения его программной памяти с содержимым этого эталона.

- •Режим пониженного энергопотребления.

- •1. Внешний сброс - импульс низкого уровня на ножке /mclr.

- •2. Сброс при срабатывании wdt(если он разрешен)

- •3. Прерывания. (Прерывание с ножки int, прерывание при изменении порта b, прерывание при завершении записи данных eeprom).

- •Максимальные значения электрических параметров

- •1. Полная рассеиваемая мощность не должна превышать 800 мВт для каждого корпуса. Рассеиваемая мощность вычисляется по следующей формуле:

- •Скоростные характеристики:

- •§8.3. Что такое pic ?....

- •Hабор регистров pic

- •Регистр косвенной адресации ind0

- •Регистры общего назначения

- •Сторожевой таймер wdt

- •Тактовый геhератор

- •Xt кварцевый резонатор

- •От теории - к практике...

- •Initb equ b'00000000' ; ; Рабочая секция ; ; начало исполняемого кода

- •Пример программы

- •Ассемблироваhие

- •Программироваhие

- •Набор команд pic

- •Incf scratch,0 ;увеличить scratch на 1

- •Iorwf dataport,1 ;установить биты в поpте b по маске w

- •Iorlw 09h ;установить 0-й и 3-й биты Светодиоды покажут 00011001.

- •Xorlw b'11111111' ;пpоинвеpтиpовать w Светодиоды покажут 11011111.

- •Comf scratch,0 ;инвеpтиpовать scratch Светодиоды покажут 10101010.

- •Специальные команды

- •§9.Введение вAdsp §9.1. Обзор

- •§9.2. Функциональные устройства

- •§9.3. Интерфейс системы и памяти

- •§9.4. Набор команд

- •§9.5. Рабочие характеристики цифровых сигнальных процессоров

- •§9.6. Базовая архитектура

- •§9.7. Вычислительные устройства

- •§9.8. Генераторы адреса и программный автомат

- •§9.9. Шины

- •§9.10. Другие устройства на кристалле

- •§9.11. Последовательные порты

- •§9.12. Таймер

- •§9.13. Порт интерфейса хост-машины (adsp-2111, adsp-2171, adsp-21msp5x)

- •§9.14. Порты прямого доступа к памяти (adsp-2181)

- •§9.15. Аналоговый интерфейс

- •§9.16. Система программно – аппаратных средств отладки процессоров семействаAdsp - 2100

- •§9.17. Генераторы адреса и программный автомат

- •§10Вычислительные устройства §10.1. Обзор

- •Последовательности двоичных символов

- •Беззнаковый формат

- •Знаковые числа в дополнительном коде

- •§10.2. Арифметико – логическое устройство (алу)

- •Блок-схема алу

- •Стандартные функции

- •Регистры ввода/вывода алу

- •Возможность операций с повышенной точностью

- •Режим насыщения алу

- •Режим фиксации переполнения алу

- •Деление

- •§10.3. Умножитель – накопитель (умножитель)

- •Арифметические операции умножителя

- •Арифметические операции устройства сдвига

- •Операции умножителя-накопителя

- •X*y Умножение операндов х и y

- •Форматы ввода данных

- •Регистры ввода/вывода умножителя-накопителя

- •§10.4. Устройство циклического сдвига

- •Денормализация

- •Нормализация

- •§11. Управление программой

- •§11.1. Обзор

- •§11.2. Программный автомат

- •§11.3 Команды управления программой

- •§11.4. Контроллер прерываний

- •§11.5. Условные команды

- •§12. Дополнительное аппаратное обеспечение §12.1. Обзор

- •§12.2. Начальная загрузка через хост – машину с использованием процедур запроса и предоставления шины

- •1) Для перезапуска процессора семейства adsp-2100 pb8 устанавливается низким.

- •§12.4. Сопряжение последовательного порта с цап

- •§12.5. Сопряжение последовательного порта с ацп

- •§12.6. Сопряжение последовательного порта с другим последовательным портом

- •§12.7. Сопряжение микрокомпьютера 80с51 с портом интерфейса хост – машины

- •§12.8. Обзор

- •§13. Программное обеспечение §13.1. Процесс отладки системы

- •§14. Система команд мп типа к580ик80

- •§14.1 Способы адресации мп

- •§14.2 Команды мп

- •§14.3 Пояснения к некоторым командам

- •§15. Архитектура микропроцессора z-80

- •§15.1 Назначение выводов

- •§15.2 Логическая организацияZ80

- •Устройство управления.

- •Регистры пользователя (основные регистры).

- •Регистровая пара hl.

- •Набор альтернативных регистров.

- •Арифметико-логическое устройство (алу).

- •§15.3 Система команд микропроцессора z – 80. Команды и данные.

- •3. Двухбайтовый адрес (addv).

- •4. Однобайтовая константа смещения.

- •Группа команд

- •Группа 1. Команда «нет операции»

- •Группа 2. Команды загрузки регистра константами.

- •Группа 4.Команды загрузки регистров из памяти.

- •Группа 5.Команды записи в память содержимого регистра или константы.

- •Группа 6.Команды сложения.

- •Группа 7.Команды вычитания.

- •Группа 8.Команды сравнения.

- •Подгруппа b. Команда or.

- •Подгруппа c. Команда xor.

- •Группа 11. Команда стека.

- •2.Адрес addr затем записывается в счетчик команд, и выполняется программа.

- •3.По команде ret осуществляется возврат из программы.

- •§16.Микросхема 80130

- •§17.Микросхема 80186

- •§18.Микросхема 80286

- •Verr — Проверить доступ по считыванию

- •Verw — Проверить доступ по записи

- •Определение состояния цикла шины процессора 80286

- •§19.Микропрцессоры серииiX86 фирмы intel Выбор в программе на Ассемблере типа процессора

- •§19.1. Процессоры 80186 и 80188

- •Новые инструкции

- •Инструкции pusha и popa

- •Инструкции enter и leave

- •Инструкция bound

- •Инструкции ins и outs

- •Расширенные версии инструкций процессора 8086

- •Imul si,10 это просто сокращенная форма инструкции:

- •§19.2. Процессор 80286

- •§19.3. Процессор 80386

- •Новые типы сегментов

- •Новые регистры

- •Новые сегментные регистры

- •Новые режимы адресации

- •Процессор 80386, новые инструкции

- •Проверка битов

- •Просмотр битов

- •Преобразование данных типа dword или qword

- •Сдвиг нескольких слов

- •Условная установка битов

- •Загрузка регистров ss, fs и gs

- •Расширенные инструкции

- •Специальные версии инструкции mov

- •Новые версии инструкций loop и jcxz

- •Новые версии строковых инструкций

- •Инструкция iretd

- •Инструкции pushfd и popfd

- •Инструкции pushad и popad

- •Новые версии инструкции imul

- •Imul ebp,ecx,100000000h а следующая инструкция умножает ecx на ebx, записывая результат в edx:eax:

- •Технический обзор Новое поколение процессоров фирмы intel

- •Pentium процессор. Технические нововведения.

- •Архитектура Pentium процессора

- •Суперскалярная архитектура.

- •Блок предсказания правильного адреса перехода.

- •Высокопроизводительный блок вычислений с плавающей запятой.

- •Расширенная 64-битовая шина данных.

- •Средства разделения памяти на страницы.

- •Определение ошибок и функциональная избыточность.

- •Управление производительностью.

- •§22.Введение в команды mmx.

- •§22.1. Регистры

- •§22.2. Префиксы

- •§22.3.Распаровка (paring).

- •§22.4. Типы данных

- •§22.5. Краткое описание команд

- •§23.Логическая структура микропроцессорной системы на основе комплекта бис секционного микропроцессора §23.1. Комплект бис секционного микропроцессора.

- •§23.2. Бис микропрограммного управления на основе программируемой логической матрицы (плм).

- •§23.3. Комплект бис для построения электронной системы.

- •§24. Обзор секционируемых мпк бис §24.1. Микропроцессорный комплект серии кр1802

- •§24.1.1. Восьмиразрядная микропроцессорная секция (мс) кр1802вс1.

- •§24.1.2. Двухадресная память общего назначения кр1802ир1.

- •§24.1.3. Шестнадцатиразрядный арифметический расширитель кр1802вр1.

- •§24.1.4. Схема обмена информацией (ои) кр1802вв1.

- •§24.1.5. Бис интерфейса (бис и) кр1802вв2.

- •§24.1.6. Сумматор (см) к1802им1.

- •§24.1.7. Км1802врз—умножитель двух 8-разрядных чисел.

- •§24.1.8. Км1802вр4—умножитель двух 12-разрядных чисел.

- •§24.1.9. Км1802вр5—умножитель двух 16-разрядных чисел.

- •§24.2. Микропроцессорный комплект серии к1804

- •§24.2.1. Центральные процессорные элементы к1804вс1 и к1804вс2

- •§24.3. Микропроцессорный комплект серии к587 §24.3.1. Арифметическое устройство к587ик2.

- •§24.3.2. Управляющая память к587рп1.

- •§24.3.3. Устройство обмена информации к587ик1.

- •§24.3.4. Арифметический расширитель к587икз.

- •§24.3.5. Архитектурные особенности построения управляющей микро-эвм на базе мпк серии к587

§5.5 Классификация алу

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В настоящее время АЛУ этого типа нигде не применяются. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

1) Для чисел с фиксированной запятой;

2) Для чисел с плавающей запятой;

3) Для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей запятой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

§5.6 Структура и формат команд. Кодирование команд.

Все возможные преобразования дискретной информации могут быть сведены к четырем основным видам:

1) передача информации в пространстве;

2) хранение информации;

3) логические операции;

4) арифметические операции.

ЭВМ, являющаяся универсальным преобразователем дискретной информации, выполняет все указанные виды преобразований.

Обработка информации в ЭВМ осуществляется автоматически путем программного управления. Программа представляет собой алгоритм обработки информации, записанный в виде последовательности команд, которые должны быть выполнены машиной для получения решения задачи.

Команда представляет собой код, определяющий операцию вычислительной машины и данные, участвующие в операции. Команда содержит также в явной или неявной форме информацию об адресе, по которому помещается результат операции, и об адресе следующей команды.

Процесс выполнения программы состоит из отдельных машинных операций. В данном случае под операцией понимается преобразование информации, выполняемое машиной под воздействием одной команды. Содержанием машинной операции могут быть запоминание в памяти, передача, арифметическое или логическое преобразование машинных слов, а также некоторые вспомогательные процедуры.

По характеру выполняемых операций различают следующие основные группы команд:

1) Команды арифметических операций для чисел с фиксированной и плавающей запятой;

2) команды десятичной арифметики;

3) команды логических операций;

4) команды передачи кодов;

5) команды ввода-вывода;

6) команды передачи управления;

7) команды задания режима работы машины.

В команде, как правило, содержатся не сами операнды, а информация об адресах ячеек памяти или регистрах, в которых они находятся.

Код команды можно представить состоящим из нескольких частей или полей, имеющих определенное функциональное назначение при кодировании командной информации. Команда в общем случае состоит из операционной и адресной частей. В свою очередь, эти части могут состоять из нескольких полей.

Операционная часть содержит код операции, который задает вид операции. Адресная часть команды содержит информацию об адресах операндов и результата операции, а в некоторых случаях информацию об адресе следующей команды.

Структура команды определяется составом, назначением и расположением полей в команде. Форматом команды называют ее структуру с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием числа бит в определенных полях.

Архитектуры микропроцессоров. При создании микропроцессоров используются все виды архитектуры, созданные за время их развития: регистровая, стековая, ориентированная на оперативную память.

Регистровая архитектура микропроцессора (архитектура типа «регистр — регистр») определяет наличие достаточно большого регистрового файла внутри БИС микропроцессора. Этот файл образует поле памяти с произвольной записью и выборкой информации. Микропроцессоры с регистровой архитектурой имеют высокую эффективность решения научно-технических задач, поскольку высокая скорость работы СОЗУ позволяет эффективно использовать скоростные возможности арифметическо-логического блока. Однако при переходе к решению задач управления эффективность таких микропроцессоров падает, так как при переключениях программ необходимо разгружать и загружать регистры СОЗУ.

Стековая архитектура микропроцессора дает возможность создать поле памяти с упорядоченной последовательностью записи и выборки информации. Эта архитектура эффективна для организации работы с подпрограммами, что необходимо для решения сложных задач управления, или при работе с языками высокого уровня. Хранение адресов возврата позволяет организовать в стеке эффективную обработку последовательностей вложенных подпрограмм. Однако стек на кристалле микропроцессора с малой информационной емкостью быстро переполняется, а стек большой емкости требует значительных ресурсов. Реализация стека в ОЗУ решает эти проблемы.

Архитектура микропроцессора, ориентированная на оперативную память (архитектура типа «память — память»), обеспечивает высокую скорость работы и большую информационную емкость рабочих регистров и стека при их организации в ОЗУ. Эта архитектура отнесена к типу «память — память», поскольку в МП с такой архитектурой все обрабатываемые числа после операции в микропроцессоре вновь возвращаются в память, а не хранятся в рабочих регистрах.

При оценке быстродействия ЭВМ необходимо учитывать физическую реализацию как элементов, так и связей между ними. Высокая скорость срабатывания логических элементов интегральных схем не всегда может обеспечить высокую скорость работы ЭВМ, поскольку большие значения индуктивно-емкостных параметров связей на печатных платах не позволяют передавать высокоскоростные сигналы без искажения. Применение БИС существенно уменьшило размеры ЭВМ, снизило паразитные параметры связей. Поэтому стало возможным физически отделить регистровый блок регистров и стек от арифметическо-логического блока и обеспечить при этом их высокоскоростную совместную работу. При создании ЭВМ в одном кристалле регистровые СОЗУ и ОЗУ имеют практически одни и те же параметры. Повышение скорости работы ОЗУ позволяет удалить регистровый файл и стек из кристалла микропроцессора и использовать освободившиеся ресурсы для развития системы команд, средств прерывания, многоразрядной обработки. Организация рабочих регистров и стека в ОЗУ приводит к уменьшению скорости передачи информации, однако при этом повышается общая эффективность такого решения за счет большой информационной емкости полей регистровой и стековой памяти, а также развития систем команд и прерываний.

Архитектура микропроцессора, ориентированная на оперативную память, обеспечивает экономию площади кристалла микропроцессора. В этом случае на кристалле размещается только регистр-указатель начального файла регистров. Адресация остальных регистров осуществляется указанием в команде кода смещения. Доступ к рабочим регистрам в этом случае замедляется, поскольку приходится совершать сопряженное с затратами времени кольцевое«путешествие» из процессора во внекристальную память, где размещаются рабочие регистры.

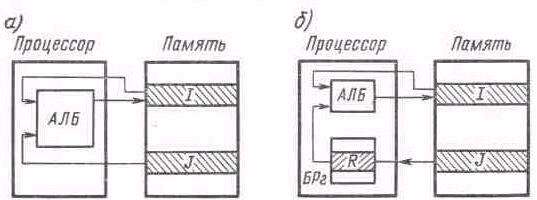

Рис. 5.4. Иллюстрированные схемы выполнения операций в микропроцессорах с архитектурой, ориентированной на оперативную память (а) и регистровой (б)

Однако контекстное переключение в микропроцессоре с такой архитектурой происходит быстро, поскольку при прерывании необходимо только изменить значение содержимого регистра-указателя рабочей области.

Другая отличительная особенность архитектуры микропроцессора, ориентированная на оперативную память,— двухадресный формат команд. В этих микропроцессорах нет специального накапливающего регистра, выполняющего функции подразумеваемой ячейки результата для всех двухоперандных команд.

Рассмотрим выполнение операции сложения содержимого двух ячеек памяти с номерами /и/по команде «Сложить //» (рис. 5.4, а). Поскольку в архитектуре типа «память — память» любая ячейка памяти может содержать либо исходный операнд, либо операнд-результат, эта операция выполняется по одной команде. В то же время в процессорах с одноадресной регистровой архитектурой для достижения той же самой цели приходится использовать две команды: команду пересылки операнда / во внутренний регистр, команду / сложения содержимого регистра с содержимым ячейки памяти / и пересылки результата в ячейку / (рис. 5.4, б).

В первом случае для компиляторов высокоуровневых языков существенно упрощается задача присвоения значений переменным и благодаря этому получаются более короткие модули объектных программ.

В отличие от микропроцессоров с архитектурой, ориентированной на оперативную память, в микропроцессорах с регистровой архитектурой рабочие области регистров размещаются в логических частях процессоров. Однако малая плотность логических схем по сравнению с плотностью схем памяти ограничивает возможность регистровой архитектуры. В свою очередь, микропроцессоры с архитектурой, ориентированной на память, обеспечивают быстрое подключение к рабочим областям, когда необходимо заменять контексты. Смена контекстов осуществляется изменением векторов трех регистров — счетчика команд, регистра состояния и указателя рабочей области. Достоинство этой архитектуры в отношении смены контекстов связано с выполнением только одной команды для передачи полного вектора контекста.

Микропроцессоры с регистровой архитектурой требуют больших и довольно медленных последовательностей команд или дополнительных логических схем для передачи данных от каждого из регистров к памяти, организованной вне БИС микропроцессора.

Использование возможностей быстрой смены контекстов и фактически неограниченной рабочей области в микропроцессорах с архитектурой, ориентированной на оперативную память, позволяет контроллерам легко находить применение в 16-разрядных системах. Особенно это относится к системам, работающим в реальном масштабе времени.

При разработке системы обработки данных, ориентированных на использование в системах управления, важное значение для определения характеристик системы, ее габаритов и стоимости имеет выбор архитектуры процессора. Поэтому в настоящее время наиболее распространенными архитектурами программируемых контроллеров, которые лежат в основе таких систем, являются архитектуры, ориентированные на память.

Еще одной статьей затрат, где видно различие между рассматриваемыми архитектурами, являются дополнительные логические схемы, требуемые для осуществления таких важных операций, как обработка многократных прерываний. Объем дополнительных логических схем возрастает по мере роста числа операций по смене контекстов. Но еще больше объем дополнительной логики возрастает для архитектур, ориентированных на регистры, за счет повышения их емкости. В результате существенно снижается быстродействие процессора.

К достоинствам архитектуры микропроцессора, ориентированной на оперативную память, относится возможность развития системы, позволяющая снизить время разработки программного обеспечения. Под развитием понимается способность систем внедрять в виде функциональных модулей программные, программно-аппаратурные и даже аппаратурные средства, которые можно использовать в системе по мере совершенствования аппаратурных средств и накопления опыта.

Распределенные системы управления часто требуют полуавтономных контроллеров, которые должны вписываться в определенные иерархические структуры. При этом архитектура микропроцессора, ориентированная на память, обеспечивает естественный и эффективный интерфейс между контроллерами, расположенными на одном иерархическом уровне, и процессами управления, расположенными на более высоком иерархическом уровне, а структура связей между контроллерами может быть обеспечена за счет развитых информационных магистралей.