- •Contents

- •Preface

- •About This Guide

- •Finding Information in This Guide

- •Other Sources of Information

- •Related Manuals

- •Customer Education Services

- •Syntax Conventions

- •Understanding How the SDF Annotator Works

- •$sdf_annotate System Task Syntax

- •Examples: Calling the SDF Annotator

- •Using the Configuration File

- •Timing Keywords

- •INTERCONNECT_MIPD Keyword

- •MTM Keyword

- •SCALE_FACTORS Keyword

- •SCALE_TYPE Keyword

- •TURNOFF_DELAY Keyword

- •MODULE Keyword

- •MAP_INNER Keyword

- •Using the SDF File

- •Understanding the SDF File

- •SDF File Conventions

- •Using Characters

- •OVI Standard SDF Keywords

- •SDF Keywords for Verilog-XL

- •SDF Keywords for Verifault-XL

- •SDF Version 1.* Constructs

- •SDF Version 2.* Constructs

- •SDF Version 3.* Constructs

- •SDF File Keyword Constructs

- •DELAYFILE Keyword

- •CELL Keyword and Constructs

- •DELAY Keyword and Constructs

- •ABSOLUTE Keyword

- •INCREMENT Keyword

- •PATHPULSE Keyword

- •PATHPULSEPERCENT Keyword

- •TIMINGCHECK Keyword and Constructs

- •TIMINGENV Keyword and Constructs

- •SDF File Examples

- •Example 1

- •Example 2

- •Example 3

- •+sdf_cputime

- •+sdf_error_info

- •+sdf_ign_timing_edge

- •+sdf_nocheck_ celltype

- •+sdf_no_errors

- •+sdf_nomsrc_int

- •+sdf_no_warnings

- •+sdf_split_two_timing_check +sdf_splitvlog_splitsuh +sdf_splitvlog_splitrecrem

- •+sdf_verbose

- •Additional Plus Options that Control the SDF Annotator

- •Improving SDF Annotator Performance and Memory Use

- •Removing Module Mapping

- •Disabling Multisource Interconnect Timing Resolution

- •Using Pre-scaled Delays

- •Synchronizing Time Scales

- •Synchronizing Precision

- •Processing Without Verbose Annotation

- •Using (INSTANCE *)

- •Grouping Redundant Constructs

- •Removing Zero-Delay MIPDs, MITDs, and SITDs

- •Working with Verilog-XL SDF Annotator Restrictions

- •Reverting to Original Timing Limitation

- •PATHPULSE Limitation for Interconnect Delays

- •COND Keyword Matching Condition Restriction

- •TIMESCALE Keyword Restriction in SDF File Header

- •Multiple Delay Data Limitations

- •Error Messages

- •Warning Messages

- •Overview

- •Valid Interconnect Combinations

- •Invalid Interconnect Combinations

- •Index

SDF Annotator Guide

SDF Annotator Error and Warning Messages

Error Messages

Error Message |

Reason |

Condition cannot be matched for IOPATH, skipping annotation

Could not annotate INTERCONNECT to cell driver port-name due to lack of driver in module

The condition specified in (COND c (IOPATH)) construct cannot be matched to any SDPD condition in the given instance.

An INTERCONNECT is annotated to an output source port that has no drivers in the cell.

Could not find path input- |

You specified a path that does not exist in the IOPATH |

path-name to output- |

construct. |

path-name in instance |

|

instance-name |

|

Failed to find HOLD |

You specified a timing check that does not exist in a HOLD |

timingcheck |

construct. |

Failed to find PERIOD |

You specified a timing check that does not exist in a |

timingcheck |

PERIOD construct. |

Failed to find RECOVERY |

You specified a timing check that does not exist in a |

timingcheck |

RECOVERY construct. |

Failed to find SETUP |

You specified a timing check that does not exist in a SETUP |

timingcheck |

construct. |

Failed to find SETUPHOLD |

You specified a timing check that does not exist in a |

timingcheck |

SETUPHOLD construct. |

Failed to find SKEW |

You specified a timing check that does not exist in a SKEW |

timingcheck |

construct. |

Failed to find WIDTH |

You specified a timing check that does not exist in a WIDTH |

timingcheck |

construct. |

INSTANCE * specified with no |

There is no corresponding CELLTYPE to a CELL that |

CELLTYPE |

contains the (INSTANCE *) construct. |

Output port port-name |

You specified an output port in a PORT construct. |

encountered in PORT |

|

January 2001 |

99 |

Product Version 3.2 |

SDF Annotator Guide

SDF Annotator Error and Warning Messages

Type of INSTANCE instance-name (instance-type) does not match CELLTYPE celltype

The cell type in the CELLTYPE construct that does not match the type of the cell in the INSTANCE construct.

Unable to annotate NETDELAY |

A NETDELAY is annotated to an output source port that |

net-name due to lack of |

has no drivers in the cell. |

driver |

|

Unable to find cells of |

There are no instances of the type specified in the |

CELLTYPE cell-type |

corresponding CELLTYPE entry when the (INSTANCE *) |

|

construct is specified. |

Unable to find PATHPULSE path input-port-name to output- port-name in instance instance-name

Unable to find input port port-name

You specified a path that does not exist in the PATHPULSE,

GLOBALPATHPULSE, or PATHPULSEPERCENT construct.

You specified an input port that does not exist in the instance of an IOPATH, PATHPULSE, GLOBALPATHPULSE, or PATHPULSEPERCENT construct.

Unable to find instance |

You specified the name of an instance that does not exist |

instance-name |

in the INSTANCE construct. |

Unable to find net net-name |

You specified a net that does not exist in the instance of a |

|

NETDELAY construct. |

Unable to find output port |

You specified an output port that does not exist in the |

port-name |

instance of an IOPATH, PATHPULSE, |

|

GLOBALPATHPULSE, or PATHPULSEPERCENT construct. |

Unable to find port port- |

You specified a port that does not exist in the instance of a |

name |

DEVICE or PORT construct. |

|

|

Warning Messages |

|

|

|

Warning Message |

Reason |

Annotating INTERCONNECT |

The SDF Annotator attempted to annotate an |

to cell driver |

INTERCONNECT delay onto the cell that is driving the |

|

source port. |

January 2001 |

100 |

Product Version 3.2 |

SDF Annotator Guide

SDF Annotator Error and Warning Messages

Annotating NETDELAY to cell |

The SDF Annotator attempted to annotate a NETDELAY |

driver |

onto the cell that is driving the net. |

Illegal limit specified, setting to |

You specified a negative limit for a SETUPHOLD or |

0 |

RECOVERY construct and did not specify +neg_tchk on |

|

the command line. This message occurs also when the |

|

sum of the two limits to a SETUPHOLD or RECOVERY |

|

construct was less than 0. |

Timescale not specified in SDF file, defaulting to 1ns

You did not specify a TIMESCALE construct in the header section of the SDF file.

January 2001 |

101 |

Product Version 3.2 |

SDF Annotator Guide

B

Valid and Invalid Interconnect

Combinations

This appendix describes the following:

■Overview on page 102

■Valid Interconnect Combinations on page 102

■Invalid Interconnect Combinations on page 115

Overview

This appendix lists the valid combinations of source and destination ports and the manner in which the SDF Annotator performs the action for each valid combination. When annotating interconnect delays, only certain combinations of ports are allowed by the SDF Annotator. In addition, certain combinations of ports may be handled in different manners.

The following sections describe the valid and invalid interconnect combinations.

Valid Interconnect Combinations

The following table shows the valid interconnect combinations.

Source Port |

Destination Port |

Fanout |

Drivers |

Schematic |

|

|

|

|

|

Output (lower) |

Input (lower) |

Yes |

Single |

Figure B-1 |

|

|

|

|

|

Output (lower) |

Input (lower) |

Yes |

Multiple |

Figure B-2 |

|

|

|

|

|

Output (lower) |

Input (lower) |

No |

Any number |

Figure B-3 |

|

|

|

|

|

Output (lower) |

Inout (lower) |

Yes |

Single |

Figure B-4 |

|

|

|

|

|

Output (lower) |

Inout (lower) |

No |

Multiple |

Figure B-5 |

January 2001 |

102 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Source Port |

Destination Port |

Fanout |

Drivers |

Schematic |

|

|

|

|

|

Output (lower) |

Inout (lower) |

No |

Any number |

Figure B-6 |

|

|

|

|

|

Output (lower) |

Inout (same) |

No |

Any number |

Figure B-7 |

|

|

|

|

|

Output (lower) |

Output (same) |

No |

Any number |

Figure B-8 |

|

|

|

|

|

Inout (lower) |

Input (lower) |

Yes |

Single |

Figure B-9 |

|

|

|

|

|

Inout (lower) |

Input (lower) |

Yes |

Multiple |

Figure B-10 |

|

|

|

|

|

Inout (lower) |

Input (lower) |

No |

Any number |

Figure B-11 |

|

|

|

|

|

Inout (lower) |

Inout (lower) |

Yes |

Single |

Figure B-12 |

|

|

|

|

|

Inout (lower) |

Inout (lower) |

Yes |

Multiple |

Figure B-13 |

|

|

|

|

|

Inout (lower) |

Inout (lower) |

No |

Any number |

Figure B-14 |

|

|

|

|

|

Inout (lower) |

Inout (same) |

No |

Any number |

Figure B-15 |

|

|

|

|

|

Inout (lower) |

Output (same) |

No |

Any number |

Figure B-16 |

|

|

|

|

|

Input (same) |

Input (lower) |

Yes |

Single or none |

Figure B-17 |

|

|

|

|

|

Input (same) |

Input (lower) |

Yes |

Multiple |

Figure B-18 |

|

|

|

|

|

Input (same) |

Inout (lower) |

Yes |

Single or none |

Figure B-19 |

|

|

|

|

|

Input (same) |

Inout (lower) |

Yes |

Multiple |

Figure B-20 |

|

|

|

|

|

Inout (same) |

Input (lower) |

Yes |

Single or none |

Figure B-21 |

|

|

|

|

|

Inout (same) |

Input (lower) |

Yes |

Multiple |

Figure B-22 |

|

|

|

|

|

Inout (same) |

Inout (lower) |

Yes |

Single or none |

Figure B-23 |

|

|

|

|

|

Inout (same) |

Inout (lower) |

Yes |

Multiple |

Figure B-24 |

|

|

|

|

|

January 2001 |

103 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

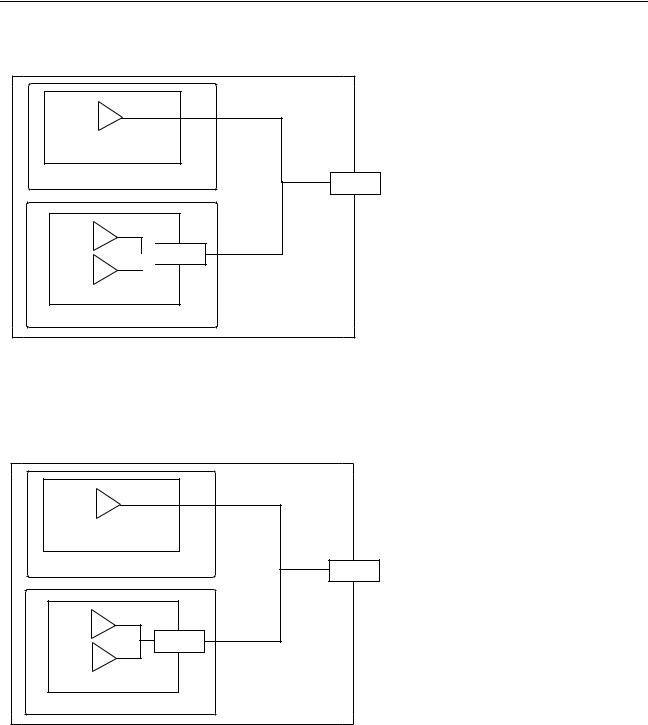

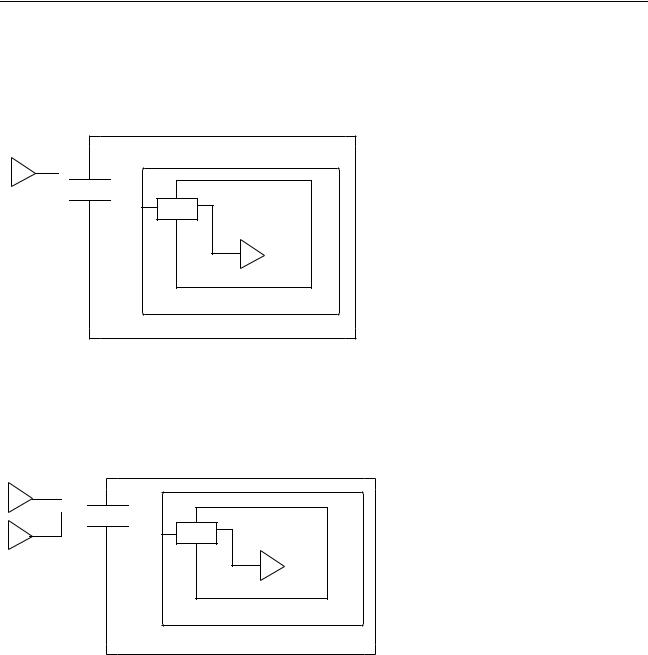

Figure B-1 Output (lower) -> Input (lower) with XL Fanout; Single Driver

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

Hierarchical Level |

|

|

|

|

Hierarchical Level |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||

Optional Hierarchical Levels |

Optional Hierarchical Levels |

||||||||||||

|

|

|

|

|

|

|

|

|

INSTANCE Cell |

|

|||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A MIPD is placed on the destination port. However, if you specify the +transport_int_delays plus option, then SITD is placed on the net.

Figure B-2 Output (lower) -> Input (lower) with XL Fanout; Multiple Drivers

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Input |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Optional Hierarchical Levels |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

||||||||||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

INSTANCE Cell |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A MIPD is placed on the destination port unless you specify the

+multisource_int_delays or +transport_int_delays plus option. If you specify the

+multisource_int_delays plus option and all destination loads are accelerated, then a

MITD is placed on the net and the delay is annotated from all sources in the source module to the destination. If you specify the +transport_int_delays plus option, a SITD is placed on the destination port.

January 2001 |

104 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

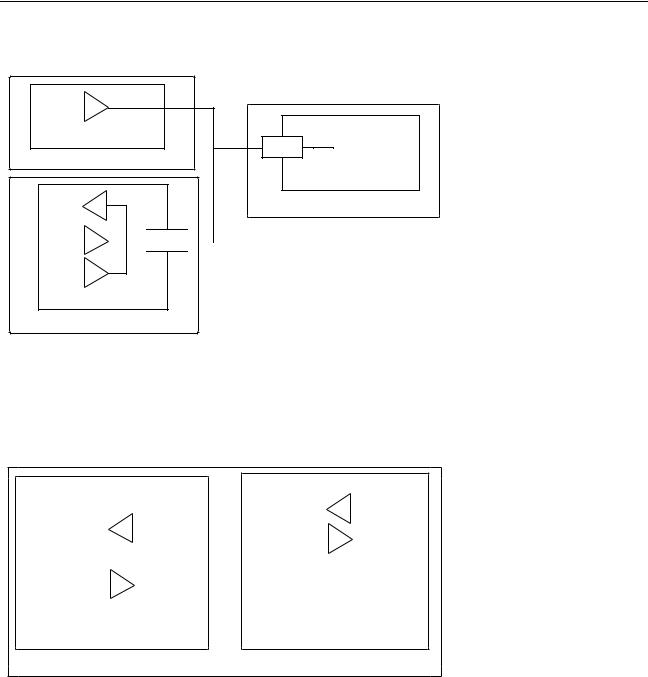

Figure B-3 Output (lower) -> Input (lower); Any Number of Drivers

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Optional Hierarchical Levels |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

Hierarchical Level |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

||||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

|

|

INSTANCE Cell |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

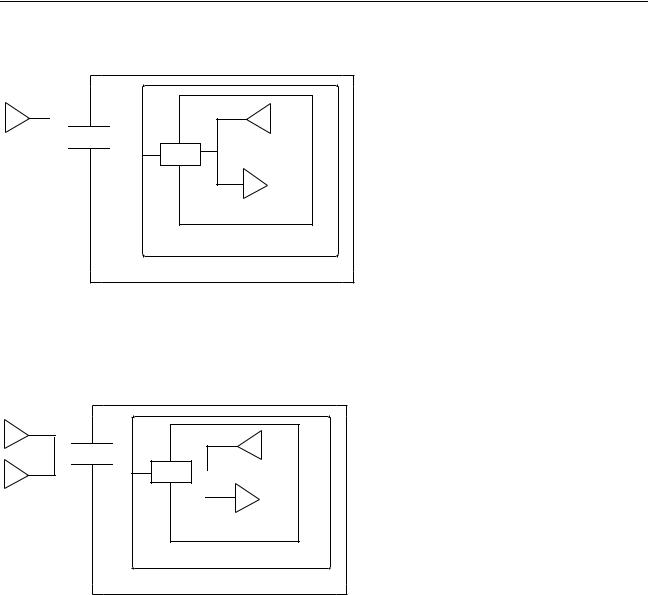

Figure B-4 Output (lower) -> Inout (lower) with XL Fanout; Single Driver

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inout |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

|

|

|

Hierarchical Level |

|

|

|

||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|||||||

|

Hierarchical Level |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

Optional Hierarchical Levels |

Optional Hierarchical Levels |

||||||||||||

|

|

|

|

|

|

|

|

|

INSTANCE Cell |

|

|||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A MIPD is placed on the destination port. However, if you specify the

+transport_int_delays plus option, then SITD is placed on the net.

January 2001 |

105 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

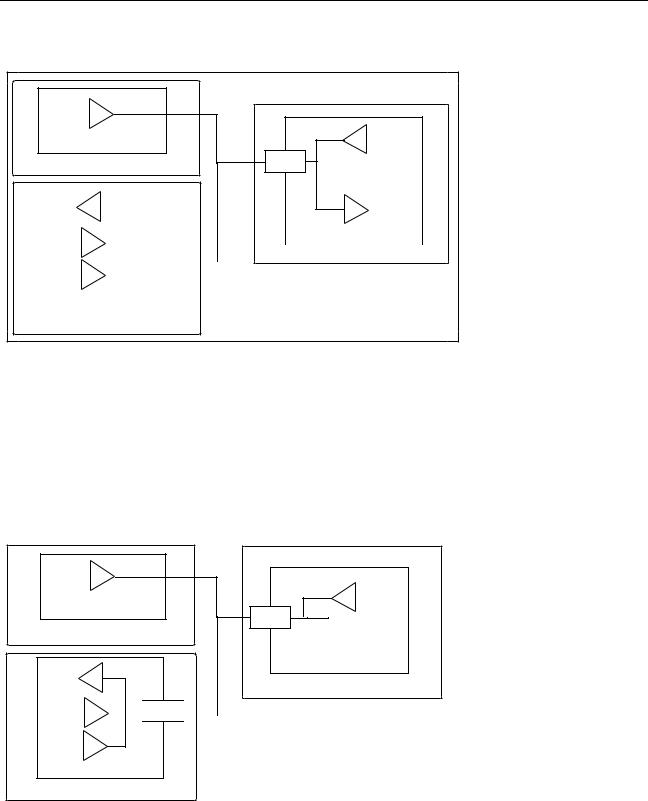

Figure B-5 Output (lower) -> Inout (lower); Multiple Drivers

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|||||||||

|

Inout |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|||||||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||||||

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

INSTANCE Cell |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A MIPD is placed on the destination port unless you specify the

+multisource_int_delays or +transport_int_delays plus option. If you specify the

+multisource_int_delays plus option and all destination loads are accelerated, then a MITD is placed on the net and the delay is annotated from all sources in the source module to the destination. If you specify the +transport_int_delays plus option, a SITD is placed on the destination port.

Figure B-6 Output (lower) -> Inout (lower); Any Number of Drivers

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

|

|

|

|

||||||||

|

Inout |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|||||||

|

|

|

|

|

|

Output |

|

|||||||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

|

INSTANCE Cell |

||||||||||

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

January 2001 |

106 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Figure B-7 Output (lower) -> Inout (same); Any Number of Drivers

Hierarchical Level |

|

Optional Hierarchical Levels |

Inout |

|

Output

Output

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

Figure B-8 Output (lower) -> Output (same); Any Number of Drivers

Hierarchical Level |

|

Optional Hierarchical Levels |

Output |

|

Output |

|

Hierarchical Level |

|

Optional Hierarchical Levels |

INSTANCE Cell |

|

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

January 2001 |

107 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

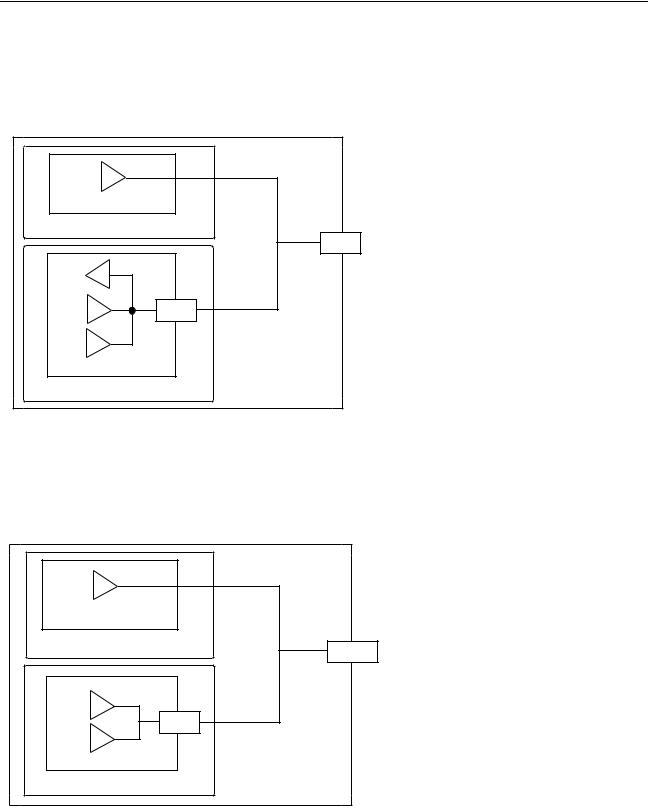

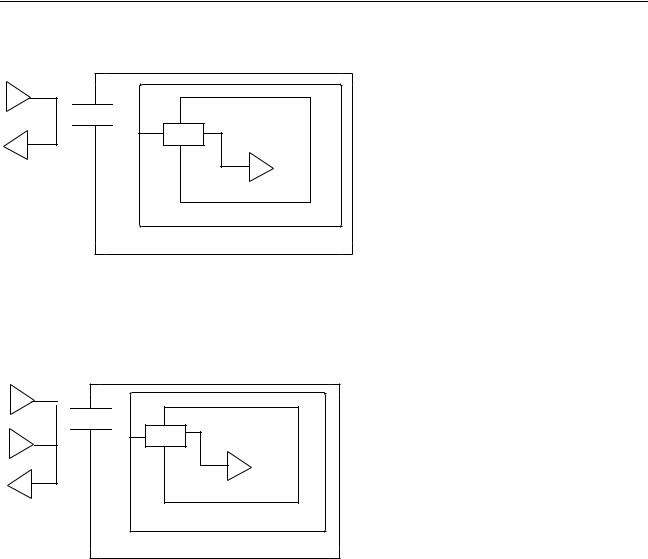

Figure B-9 Inout (lower) -> Input (lower) with XL Fanout; Single Driver

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inout |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

Hierarchical Level |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

Optional Hierarchical Levels |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

INSTANCE Cell |

||

A MIPD is placed on the destination port. However, if you specify the

+transport_int_delays plus option, then SITD is placed on the net.

Figure B-10 Inout (lower) -> Input (lower) with XL Fanout; Multiple Drivers

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Input |

|

|

|

|

Optional Hierarchical Levels |

|

|

|

|

|||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inout |

|

Optional Hierarchical Levels |

|||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|||||

Optional Hierarchical Levels |

|

|

INSTANCE Cell |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A MIPD is placed on the destination port unless you specify the

+multisource_int_delays or +transport_int_delays plus option. If you specify the

+multisource_int_delays plus option and all destination loads are accelerated, then a MITD is placed on the net and the delay is annotated from all sources in the source module to the destination. If you specify the +transport_int_delays plus option, a SITD is placed on the destination port.

January 2001 |

108 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Figure B-11 Inout (lower) -> Input (lower); Any Number of Drivers

Hierarchical Level

Input

Optional Hierarchical Levels

Hierarchical Level

Optional Hierarchical Levels

Inout

Inout

Hierarchical Level

Optional Hierarchical Levels

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

Figure B-12 Inout (lower) -> Inout (lower) with XL Fanout; Single Driver

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inout |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inout |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

Hierarchical Level |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

Optional Hierarchical Levels |

||||||||||||

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the +transport_int_delays plus option, then SITD is placed on the net.

January 2001 |

109 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Figure B-13 Inout (lower) -> Inout (lower) with XL Fanout; Multiple Drivers

Hierarchical Level |

|

Optional Hierarchical Levels |

Inout |

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

||

|

|

|

|

|

Inout |

|

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hierarchical Level |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

Optional Hierarchical Levels |

|

INSTANCE Cell |

||||||||

|

|

|

|

|

|

|

|

|

||

A MIPD is placed on the destination port unless you specify the

+multisource_int_delays or +transport_int_delays plus option. If you specify the

+multisource_int_delays plus option and all destination loads are accelerated, then a MITD is placed on the net and the delay is annotated from all sources in the source module to the destination. If you specify the +transport_int_delays plus option, a SITD is placed on the destination port.

Figure B-14 Inout (lower) -> Inout (lower); Any Number of Drivers

Hierarchical Level

Inout

Optional Hierarchical Levels

Hierarchical Level

Optional Hierarchical Levels

Inout

Inout

Hierarchical Level

Optional Hierarchical Levels

January 2001 |

110 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

Figure B-15 Inout (lower) -> Inout (same); Any Number of Drivers

Hierarchical Level

Optional Hierarchical Levels

Inout

Inout |

|

Hierarchical Level |

|

Optional Hierarchical Levels |

INSTANCE Cell |

|

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

Figure B-16 Inout (lower) -> Output (same); Any Number of Drivers

Hierarchical Level

Optional Hierarchical Levels

Output

Inout |

|

Hierarchical Level |

|

Optional Hierarchical Levels |

INSTANCE Cell |

|

January 2001 |

111 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

The delay is annotated onto the cell output corresponding to the source port, which is either a path delay driving the port or all gates driving the port.

Figure B-17 Input (same) -> Input (lower) with XL Fanout; Single or No Driver

Input

Input

Input

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the +transport_int_delays plus option, then SITD is placed on the net.

Figure B-18 Input (same) -> Input (lower) with XL Fanout; Multiple Drivers

Input

Input

Input

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the +multisource_int_delays plus option a MITD is placed on the destination port.

January 2001 |

112 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Figure B-19 Input (same) -> Inout (lower) with XL Fanout; Single or No Drivers

Input

Input

Inout

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the +transport_int_delays plus option, then SITD is placed on the net.

Figure B-20 Input (same) -> Inout (lower) with XL Fanout; Multiple Drivers

Input

Input

Inout

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the

+multisource_int_delays plus option a MITD is placed on the destination port.

January 2001 |

113 |

Product Version 3.2 |

SDF Annotator Guide

Valid and Invalid Interconnect Combinations

Figure B-21 Inout (same) -> Input (lower) with XL Fanout; Single or No Driver

Inout

Inout

Input

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the +transport_int_delays plus option, then SITD is placed on the net.

Figure B-22 Inout (same) -> Input (lower) with XL Fanout; Multiple Drivers

Inout

Inout

Input

Hierarchical Level

Optional Hierarchical Levels

INSTANCE Cell

A MIPD is placed on the destination port. However, if you specify the

+multisource_int_delays plus option a MITD is placed on the destination port.

January 2001 |

114 |

Product Version 3.2 |