Broadband Packet Switching Technologies

.pdf

SWITCH ARCHITECTURE CLASSIFICATION |

25 |

SDS switches are classified based on the number of available paths between any inputroutput pair. In single-path switches, only one path exists for any inputroutput pair, while in multiple-path switches there is more than one. The former has simpler routing control than the latter, but the latter has higher fault tolerance.

2.2.2.1 Single-Path Switches Single path switches are classified into crossbar-based switches, fully interconnected switches, and banyan-based switches w10x.

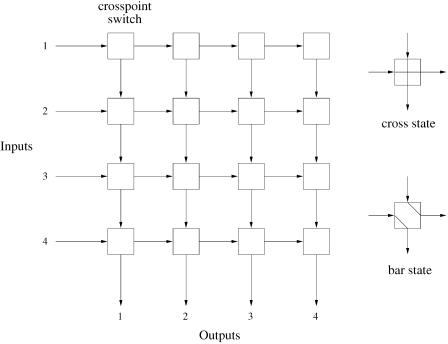

(a) Crossbar Switches A crossbar switch is schematically shown in Figure 2.8 for N s 4, where horizontal lines represent the inputs to the switch, and vertical lines represent the outputs. Basically, an N N crossbar switch consists of a square array of N 2 individually operated crosspoints, one corresponding to each input output pair. Each crosspoint has two possible states: cross Ždefault. and bar. A connection between input port i and output port j is established by setting the Ži, j.th crosspoint switch to the bar state while letting other crosspoints along the connection remain the cross state. The bar state of a crosspoint can be triggered individually by each incoming

Fig. 2.8 A 4 4 crossbar switch.

26 BASICS OF PACKET SWITCHING

cell when its destination matches with the output address. No global information about other cells and their destinations is required. This property is called the self-routing property; by it the control complexity is significantly reduced in the switching fabric, as the control function is distributed among all crosspoints.

Crossbar switches have three attractive properties: they are internally nonblocking, simple in architecture, and modular. However, they are complex in terms of the number of the crosspoints, which grows as N 2. The arbitration that is to choose a winner for every output in each time slot can also become a system bottleneck as the switch size increases.

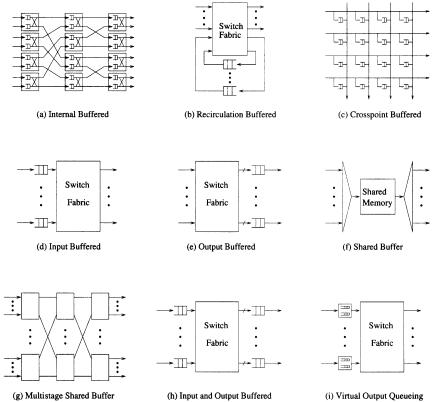

There are three possible locations for the buffers in a crossbar switch: Ža. at the crosspoints in the switch fabric, Žb. at the inputs of the switch, and Žc. at the inputs and outputs of the switch. Each one has its advantages and disadvantages.

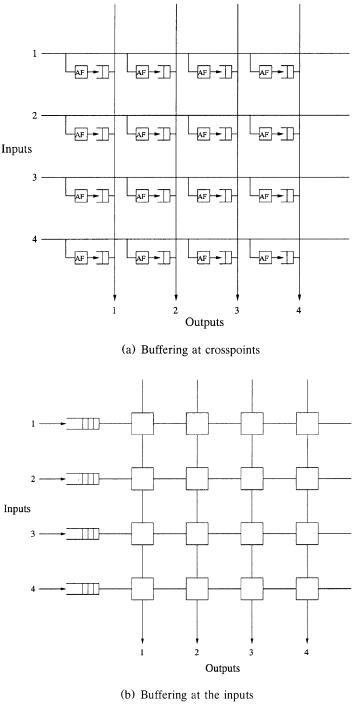

Figure 2.9Ža. depicts the strategy of buffering cells at the crosspoints. The bus matrix switch ŽBMX. proposed by Fujitsu is an example of this type of switch w11x. There is an AF and a buffer at each crosspoint. The AF accepts the cells destined for the corresponding output port and stores them in the buffer. Cells waiting in the buffers on the same column are arbitrated to the output port with one cell per slot. The switch is work-conserving, and does not suffer the throughput limitation incurred with input buffering. In a sense, it is similar to achieving output queuing, with the difference that the queue for each output is distributed over N buffers. As there is no sharing among the N buffers, the total memory required for a given loss rate is greater than that required for output queuing Že.g., in the shared-medium case.. As the buffer memory typically requires much more real estate in a chip than crosspoint logic, including the crosspoint buffers in the chip would severely limit the number of crosspoints in the chip.

Figure 2.9Žb. depicts the input queuing approach. Separating the buffers from the crosspoints is desirable from the viewpoint of layout and circuit compactness. A cell arriving at an input first enters the buffer, waiting its turn to be switched over the fabric. With distributed contention resolution, conflicts are resolved individually at crosspoints. When a cell reaches a crosspoint that has already been set by an earlier cell, or it loses contention to another contending cell, a blocking signal is generated and sent to the input port. This is to block the transmission of the cell and to keep the cell in the input buffer for later tries. With centralized contention resolution, alternatively, an arbiter is used for each output port to resolve contention, and only one cell destined for an output is allowed to be forwarded to the switch fabric.

The third approach combines the advantages of input buffering and output buffering. The detail is described in Section 2.2.3.

(b) Fully Interconnected Switches In a fully interconnected switch, the complete connectivity between inputs and outputs is usually accomplished by

SWITCH ARCHITECTURE CLASSIFICATION |

27 |

Fig. 2.9 Different buffering strategies for a crossbar switch.

28 BASICS OF PACKET SWITCHING

Fig. 2.10 A fully interconnected switch.

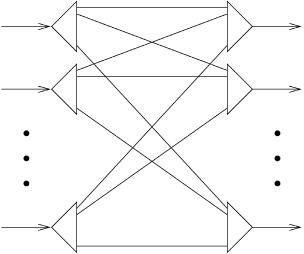

means of N separate broadcast buses from every input port to all output ports, as shown in Figure 2.10. N separate buffers are required in such a switch, one at each output port. However, if each of these N output buffers in the fully interconnected switch is partitioned and dedicated to each input line, yielding N 2 dedicated buffers, it becomes topologically identical with the crosspoint-buffered switch, and thus provides exactly the same performance and implementation complexity.

The fully interconnected switch operates in a similar manner to the shared-medium switch. A cell from any input port is broadcast to every output port. Thus, cells from several input ports can be simultaneously transmitted to the same output port. Therefore, cell filters and dedicated buffers, one for each output port, are required to filter out the misdelivered cells and to temporarily store the properly destined cells.

However, the fully interconnected switch is different from the sharedmedium switch in that the speedup overhead requirement caused by sequential transmission over the shared medium is replaced by the space overhead requirement of the N 2 separate broadcast buses. This is considered a disadvantage of the switch type. The advantages of the fully interconnected switch lie in its simple and nonblocking structure, similar to the crossbar-based switch. The knockout switch is an example of this type of switch w15x.

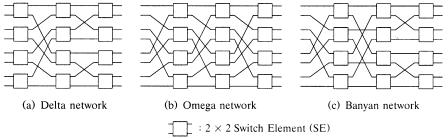

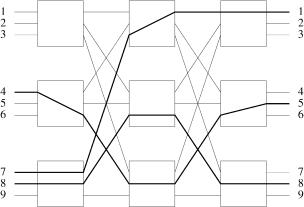

(c) Banyan-Based Switches Banyan-based switches are a family of selfrouting switches constructed from 2 2 switching elements with a single path between any input output pair. As shown in Figure 2.11, there are

SWITCH ARCHITECTURE CLASSIFICATION |

29 |

Fig. 2.11 Three different topologies of banyan-based switches.

three isomorphic topologies delta, omega, and banyan networks belonging to the banyan-based family. All of them offer equivalent performance and are discussed in detail in Chapter 5.

The banyan-based switch provides several advantages: First, it has a complexity of paths and switching elements of order N log N, which makes it much more suitable than the crossbar-based and the fully interconnected switch, whose complexity is of order N 2 , for the construction of large switches. Self-routing is also an attractive feature in that no control mechanism is needed for routing cells. Routing information is contained within each cell, and it is used while the cell is routed along the path. Parallel structure of the switch provides a benefit in that several cells on different paths can be processed simultaneously. Due to their modular and recursive structure, large-scale switches can be built by using elementary switching elements without modifying their structures. This can be appropriately realized by VLSI implementation.

The main drawback of the banyan-based switch is that it is an internally blocking switch. Its performance degrades rapidly as the size of the switch increases. The performance may be improved if M M Ž M 2. switching elements are employed instead of 2 2 switching elements. This leads to the class of delta-based switches.

The delta-based switch is a family of self-routing switches constructed from M M switching elements with a single path between any input and output port. While the performance of the delta-based switch can be significantly better than that of the banyan-based switch, it is still a blocking switch. The performance of the switch is reduced due to internal contention. This can be improved by increasing the speed of internal links within the switch with respect to that of input and output ports or by introducing buffers into the switching elements.

2.2.2.2 Multiple-Path Switches Multiple-path switches are classified as augmented banyan switches, Clos switches, multiplane switches, and recircula- tion switches, as shown in Figure 2.12.

30 BASICS OF PACKET SWITCHING

Fig. 2.12 Multiple-path space-division switches.

(a) Augmented Banyan Switches In a regular N N banyan switch, cells pass through log N stages of switching elements before reaching their destinations. The augmented banyan switch, as illustrated in Figure 2.12Ža., has more stages than the regular banyan switch. In the regular banyan switch, once a cell is deflected to an incorrect link and thus deviates from a predetermined unique path, the cell is not guaranteed to reach its requested output. Here, in the augmented banyan switch, deflected cells are provided more chances to be routed to their destinations again by using later augmented stages. When the deflected cells do not reach their destinations after the last stage, they are discarded.

The advantage of the augmented banyan switch is that by adding augmented stages, the cell loss rate is reduced. The performance of the switch is improved. The disadvantage of this switch type is its complicated routing scheme. Cells are examined at every augmented stage to determine whether they have arrived at their requested output ports. If so, they are sent to the output interface module. Otherwise, they are routed to the next stage and will be examined again. Another disadvantage is that the number of augmented stages needs to be sufficiently large. Adding each augmented stage to the switch causes increased hardware complexity. The tandem banyan switch w14x and dual shuffle exchange switch w9x are examples of the augmented banyan switches.

(b) Three-Stage Clos Switches The structure of three-stage Clos switches, as shown in Figure 2.12Žb., consists of three stages of switch modules. At the

SWITCH ARCHITECTURE CLASSIFICATION |

31 |

Fig. 2.13 Example of internal blocking in a three-stage Clos switch.

first stage, N input lines are broken up into r groups of n lines. Each group of lines goes into each first-stage switch module. There are m outputs in the first-stage switch module; each connects to all m middle-stage switch modules. Similarly, each middle-stage switch module has t outputs, so that it connects to all t third-stage switch modules. At the third stage, N output lines are provided as t groups of s lines.

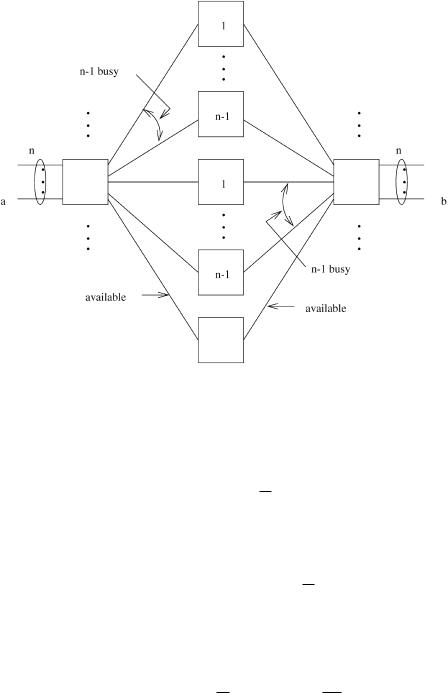

A consideration with the three-stage Clos switch is that it may be blocking. It should be clear that a crossbar-based switch is nonblocking; that is, a path is always available to connect an idle input port to an idle output port. This is not always true for the three-stage Clos switch. Figure 2.13 shows a three-stage Clos switch with N s 9, n s 3, and m s 3. The bold lines indicate paths that are already in use. It is shown that input port 9 cannot be connected to either output port 4 or 6, even though both of these output lines are available.

By increasing the value of m Žthe number of outputs from each first-stage switch module or the number of middle-stage switch modules., the probability of blocking is reduced. To find the value of m needed for a nonblocking three-stage switch, let us refer to Figure 2.14.

We wish to establish a path from input port a to output port b. The worst situation for blocking occurs if all of the remaining n y 1 input lines and

n y 1 |

output lines are busy and are connected to different |

middle-stage |

switch |

modules. Thus a total of Žn y 1. q Žn y 1. s 2 n y 2 middle-stage |

|

switch modules are unavailable for creating a path from a to b. However, if one more middle-stage switch module exists, an appropriate link must be available for the connection. Thus, a three-stage Clos switch will be nonblocking if

m G Ž2 n y 2. q 1 s 2 n y 1.

32 BASICS OF PACKET SWITCHING

Fig. 2.14 Nonblocking condition for a three-stage Clos switch.

The total number Nx of crosspoints in a three-stage Clos switch when it is symmetric Žthat is, when t s r and s s n. is

Nx s 2 Nm q m ž Nn /2 .

Substituting m s 2 n y 1 into Nx , we obtain

Nx s 2 NŽ2 n y 1. q Ž2 n y 1. ž Nn /2 .

for a nonblocking switch. For a large switch size, n is large. We can approximate

Nx , 2 NŽ2 n. q 2 n ž Nn /2 s 4 Nn q 2 ž Nn2 /.

SWITCH ARCHITECTURE CLASSIFICATION |

33 |

To optimize the number of crosspoints, differentiate Nx with respect to

n and set the result equal to 0. The result will be n f Ž Nr2. 1 . Substituting

2

into Nx ,

|

|

3 |

3 |

Nx s 4'2 N2 |

s OŽ N2 . . |

||

The three-stage Clos switch provides an advantage in that it reduces the hardware complexity from OŽ N 2 . in the case of the crossbar-based switch to

OŽ N 3 ., and the switch can be designed to be nonblocking. Furthermore, it

2

also provides more reliability since there is more than one possible path through the switch to connect from any input port to any output port. The main disadvantage of this switch type is that some fast and intelligent mechanism is needed to rearrange the connections in every cell time slot according to arrival cells so that internal blocking can be avoided. This will be the bottleneck when the switch size becomes large. In practice, it is difficult to avoid internal blocking although the switch itself is nonblocking. Once contention on the internal links occurs, the throughput is reduced. This can be improved by increasing the number of internal links between switch modules so that there are more paths for routing cells. Increasing the bandwidth of internal links is also helpful in that instead of having one cell for each internal link in each time slot, now more than one cell from the input module that are destined to the same third-stage module can be routed. Another way to reduce the internal blocking is routing cells in a random manner. If the center-stage switch modules have buffers, careful provision has to be made at the output ports in order to preserve cell sequencing.

(c) Multiplane Switches As shown in Figure 2.12Žc., multiplane switches refer to the switches that have multiple Žusually identical. switch planes. Multiplane switches are mainly proposed as a way to improve system throughput. By using some mechanisms to distribute the incoming traffic loading, cell collisions within the switches can be reduced. Additionally, more than one cell can be transmitted to the same output port by using each switch plane, so the output lines do not have to operate at higher speed than the input lines. Another advantage of multiplane switches is that they can be used for achieving reliability, since the loss of a whole switch plane will reduce the capacity but not the connectivity of the switches. However, cell sequencing may be disturbed unless cells belonging to the same connection are forced to use the same plane. The parallel banyan switch and the Sunshine switch w4x are examples of multiplane switches.

(d) Recirculation Switches Recirculation switches, as shown in Figure 2.12Žd., are designed to handle the output port contention problem. By recirculating the cells that did not make it to their output ports during the current time slot back to the input ports via a set of recirculation paths,

34 BASICS OF PACKET SWITCHING

the cell loss rate can be reduced. This results in system throughput improvement. The disadvantage of recirculation switches is that they require a large switch to accommodate the recirculation ports. Also, recirculation may cause out-of-sequence errors. Some mechanisms are needed to preserve the cell sequencing among the cells in the same connection. The best-known recirculation switches are the Starlite switch w6x and the Sunshine switch w4x.

2.2.3 Buffering Strategies

In this subsection, we classify ATM switches according to their buffering strategies. Each type of switch is described, and its advantages and disadvantages are discussed.

2.2.3.1 Internally Buffered Switches Internally buffered switches are those that employ buffers within switch elements ŽSEs.. An example of this switch type is the buffered banyan switch, as shown in Figure 2.15Ža.. These

Fig. 2.15 Buffering strategies for ATM switches.