- •Г.И.Загарий, н.О.Ковзель, в.С.Коновалов, в.И.Моисеенко, в.И.Поддубняк, а.И.Стасюк

- •Часть 2. Характеристики микроконтроллеров и плк

- •Рецензенты:

- •Isbn – 5–7763–0384–2

- •Isbn – 966–7561–23–2

- •Isbn – 966-7561-23-2

- •Isbn – 5–7763–0384-2

- •Содержание

- •Введение

- •Раздел 1

- •1 Микроконтроллеры фирмы Atmel

- •1.1 Микроконтроллеры серии ат89, совместимые с mcs-51™

- •1.2 Микроконтроллеры avr серии ат90 с risc-архитектурой

- •2. Микроконтроллер aDμC812 семейства MicroConverter™ фирмы analog devices

- •3 Микроконтроллеры sx18ac/sx28ac фирмы scenix

- •4 Микроконтроллеры фирмы motorola

- •5 Микроконтроллеры семейства z8 фирмы zilog

- •6 Микроконтроллеры фирмы holtek

- •7 Рiс – микроконтроллеры фирмы microchip

- •7.1 Микроконтроллер pic16f84

- •7.1.1 Архитектура микроконтроллера pic16f84

- •7.1.2 Типы корпусов и исполнения

- •7.1.3 Назначение выводов

- •7.1.4 Регистры pic16f84

- •7.1.5 Прямая и косвенная адресация регистров

- •7.1.6 Модуль таймера/счетчика

- •7.1.7 Предварительный делитель

- •7.1.8 Регистр слова состоянияStatus

- •7.1.8.1 Программные флаги регистра слова состояния

- •7.1.8.2 Аппаратные флаги состояния

- •7.1.9 Регистр option

- •7.1.11 Организация встроенного пзу

- •7.1.12 Программный счетчик и адресация пзу

- •7.1.13 Стек и возвраты из подпрограмм

- •7.1.14 Данные в eeprom

- •7.1.15 Управление eeprom Управляющие регистры для eeprom

- •Регистры eecon1 и eecon2

- •7.1.16 Организация прерываний

- •Внешнее прерывание

- •Прерывание от переполнения счетчика/таймера

- •Прерывание от порта rb

- •Прерывание от eeprom

- •7.1.17 Регистры (порты) ввода/вывода

- •7.1.18 Использование портов ввода/вывода ra и rb Организация двунаправленных портов

- •Последовательное обращение к портам ввода/вывода

- •7.1.19 Специальные функции

- •Сторожевой таймер wdt

- •Тактовый генератор

- •Таймер сброса dtr

- •Биты конфигурации

- •Защита программы от считывания

- •Режим пониженного энергопотребления

- •7.2 Обзор команд и обозначения

- •7.2.1 Описание команд

- •7.3Технология разработки и отладки рабочих программ для омк рiс16/17

- •7.3.1 Правила записи программ на языке Ассемблера

- •Операция

- •Операнд

- •Директивы Ассемблера

- •7.3.2 Структура рабочей программы

- •7.3.3 Преобразование исходного текста рабочей программы в объектный модуль

- •7.4 Интегрированная среда разработки рабочих программ mplab для омк pic

- •7.4.1 Назначение и основные функциональные возможности mplab

- •7.4.2 Краткая характеристика основных программ Редактор mplab

- •Ассемблер mpasm

- •Компилятор mplab-c

- •Программный симулятор-отладчик mplab-sim

- •7.4.3 Главное окно средыMplab Главное меню mplab

- •МенюFile

- •МенюProject

- •МенюEdit

- •МенюDebug (отладка)

- •Меню picstart plus (меню программирования)

- •МенюOptions (параметры)

- •МенюTools

- •7.4.4 Инструментальная панельMplab

- •7.4.5 Строка состояния mplab

- •7.5 Пример разработки программы с использованием mplab

- •7.5.1 Постановка задачи и разработка алгоритма ее решения

- •7.5.2 Написание исходного текста программы

- •Раздел 2

- •8. Характеристики программируемых логических контроллеров

- •8.1. Контроллеры семейства модикон

- •8.1.1. Контроллер tsx 07 Nano

- •Варианты конфигураций

- •Импульсные выходы

- •Программное обеспечение

- •Контрольные вопросы:

- •8.1.2. Контроллер tsx Momentum Общая характеристика

- •Концепция построения

- •Архитектура tsx Momentum

- •Подключение tsx Momentum к сети Modbus Plus

- •Коммуникационный адаптер для сети Interbus

- •Коммуникационный адаптер для сети Profibus dp

- •Коммуникационный адаптер для сети fipio

- •Коммуникационный адаптер для сети Ethernet I/o

- •Базовые модули ввода – вывода

- •Заключение

- •Контрольные вопросы

- •8.1.3. Микроконтроллер tsx 37 Micro Общая характеристика

- •Базовое исполнение tsx 37-10

- •Дисплейный блок

- •Базовое исполнение tsx 37-21 и tsx 37-22

- •Источники питания

- •Коммуникационные возможности

- •Заключение

- •Контрольные вопросы

- •8.2. КонтроллерыTsxQuantum Общая характеристика

- •Источники питания

- •Модули ввода-вывода

- •Модули интерфейса Quantum

- •Заключение

- •Контрольные вопросы

- •8.3. Контроллеры Siemens

- •8.3.1. КонтроллерSimaticS7-200

- •Центральные процессоры

- •Входы и выходы контроллеров s7-200

- •Коммуникационный модуль

- •8.3.2.Контроллер Simatic s7-300

- •Центральные процессоры

- •Сигнальные модули

- •Функциональные модули

- •Коммуникационные модули

- •Заключение

- •Контрольные вопросы

- •8.3.3. Контроллер Simatic s7-400

- •Центральные процессоры

- •Модули ввода-вывода

- •Функциональные модули

- •Коммуникационные процессоры

- •Блоки питания

- •Заключение

- •Контрольные вопросы

- •Раздел 3

- •9. Разработка микропроцессорных систем железнодорожной автоматики

- •9.1. Постановка задачи

- •9.2. Характеристика входных и выходных сигналов.

- •9.3. Разработка структуры системы

- •9.4. Конфигурация цепей ввода-вывода

- •9.5. Определение необходимого количества модулей ввода-вывода

- •9.6.Принципиальные и монтажные схемы

- •Индивидуальные задания

- •10. Примеры практической реализации микропроцессорных систем

- •10.1.Микропроцессорная диспетчерская централизация

- •Объекты контроля

- •Объекты управления

- •10.2.Микропроцессорный маршрутный набор электрической централизации

- •10.2.1 Постановка задачи

- •10.2.2 Общая структура системы управления.

- •10.2.3 Расчет количества входных и выходных сигналов.

- •Расчет потребного количества выходов

- •Управление стрелкой

- •Перечень объектов контроля

- •Расчет потребного количества входов

- •Выбор конфигурации программируемого логического контроллера

- •Разработка структуры информационного взаимодействия компонентов системы

- •Программируемые контроллеры для систем управления.

- •Часть 2. Характеристики микроконтроллеров и плк

- •61052, Харьков, ул. Красноармейская, 7, тел. 24-22-98.

- •61052, Харків, вул. Червоноармійська, 7, тел. 24-22-98.

7.1.8.2 Аппаратные флаги состояния

Аппаратные биты

статуса

![]() (Time Out) и

(Time Out) и

![]() (Power Down).

(Power Down).

По состоянию битов

регистра статуса "![]() "

и "

"

и "![]() "

можно определить, чем был вызван "Сброс":

"

можно определить, чем был вызван "Сброс":

включением питания;

срабатыванием сторожевого таймера (WDT);

выходом из режима пониженного энергопотребления (Sleep) в результате срабатывания сторожевого таймера;

по внешнему сигналу

![]() .

.

На состояние этих битов оказывают влияние следующие события:

|

Событие |

|

|

Примечание |

|

Включение питания |

1 |

1 |

|

|

WDT timeout |

0 |

Х |

Не

воздействует на бит

|

|

команда Sleep |

1 |

0 |

|

|

команда CLRWDT |

1 |

1 |

|

Примечание:

Событие WDT timeout происходит независимо

от состояния бита

![]() .

.

Ниже показаны

состояния битов

![]() и

и

![]() после сброса

после сброса

|

|

|

Сброс был вызван событием |

|

0 |

0 |

Выход из SLEEP по завершению задержки Watchdog |

|

0 |

1 |

Завершение задержки Watchdog (Не режим SLEEP) |

|

X |

0 |

Выход

из SLEEP по внешнему сигналу

|

|

1 |

1 |

Включение питания |

|

X |

X |

0

– Импульс на входе

|

Примечание:

Биты

![]() и

и

![]() сохраняют текущее состояние до тех пор,

пока не произойдет одно из перечисленных

событий. 0–Импульс низкого уровня на

входе кристалла

сохраняют текущее состояние до тех пор,

пока не произойдет одно из перечисленных

событий. 0–Импульс низкого уровня на

входе кристалла

![]() не изменяет состояние битов

не изменяет состояние битов

![]() и

и

![]() .

.

7.1.9 Регистр option

Регистр OPTION доступен для записи и чтения, содержит биты упраления различными процессами. После сброса биты регистра OPTION установлены в состояние 1.

REGISTER OPTION(ADDRESS 81h)

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

Бит 7 –

![]() используется для отключения (

используется для отключения (![]() = 1) и включения (

= 1) и включения (![]() = 0) нагрузки входов портаB.

= 0) нагрузки входов портаB.

Бит 6 – INTEDG – устанавливает прерывание по нарастающему (INTEDG = 1) либо спадающему (INTEDG = 0) фронту сигнала.

Использование бит 5 – 0 описано в разделах 7.1.6, 7.1.7.

7.1.11 Организация встроенного пзу

Программный счетчик в PIC16F84 имеет ширину 13 бит и способен адресовать 8Кх14бит объема программной памяти. Однако, физически на кристалле имеется только 1Кх14 памяти (адреса 0000h-03FFh). Обращение к адресам выше 3FFh фактически есть адресация в тот же первый килобайт. Вектор сброса находится по адресу 0000h, вектор прерывания находится по адресу 0004h.

EEPROM PIC16F84 рассчитан

на ограниченное число циклов

стирания/записи. Чтобы записать в

программную память, кристалл должен

быть переведен в специальный режим при

котором на вывод

![]() подается напряжение программирования

Vprg, а питание Vdd должно находиться в

пределах 4.5 В ... 5.5В. PIC16F84 непригоден для

применений, в которых часто модифицируется

программа. Запись в программную память

осуществляется побитно, последовательно

с использованием только двух выводов

микросхемы.

подается напряжение программирования

Vprg, а питание Vdd должно находиться в

пределах 4.5 В ... 5.5В. PIC16F84 непригоден для

применений, в которых часто модифицируется

программа. Запись в программную память

осуществляется побитно, последовательно

с использованием только двух выводов

микросхемы.

7.1.12 Программный счетчик и адресация пзу

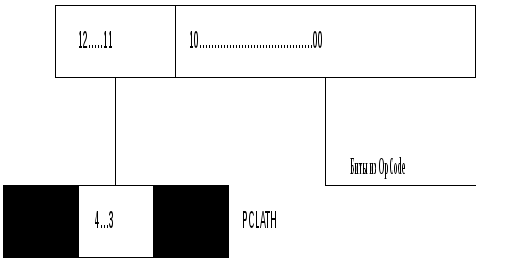

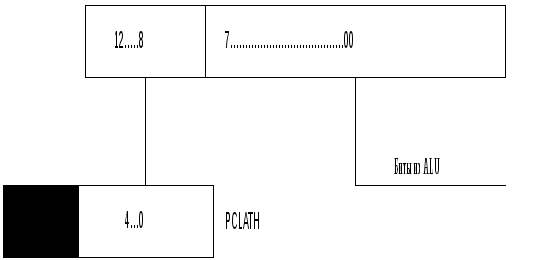

PC (f2) – программный счетчик (счетчик команд). Ширина программного счетчика – 13 бит. Младший байт программного счетчика (PCL) доступен для чтения и записи и находится в регистре 02h. Старший байт программного счетчика (PCH) не может быть прямым образом прочитан или записан. Старший байт программного счетчика может быть записан через регистр PCLATH, адрес которого 0Ah. В зависимости от того, загружается ли в программный счетчик новое значение во время выполнения команд CALL, GOTO или в младший байт программного счетчика (PCL) производится запись, – старшие биты программного счетчика загружаются из PCLATH разными способами так, как показано на рис. 7.8 и рис. 7.9.

Рис. 7.8. Формирование программного счетчика для команд GOTO, CALL

Рис. 7.9. Формирование программного счетчика для команд, у которых результат помещается в f2