- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

262 |

||

|

|

Выход (код) |

|

Uвх |

|

|

|

К |

ГИ |

Регистр |

ЦАП |

Рис. 19.7. Функциональная схема АЦП поразрядного уравновешивания |

|||

U цап

U вх

0 1 0 0 1

t

Рис. 19.8. Временная диаграмма работы АЦП поразрядного уравновешивания

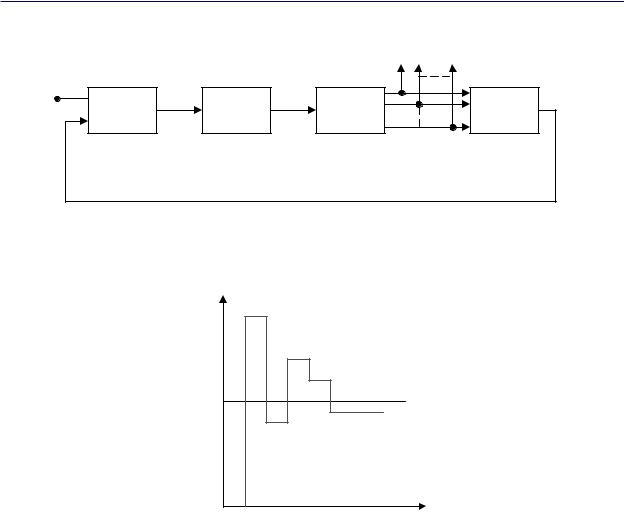

На рис. 19.7 приведена функциональная схема АЦП поразрядного уравновешивания.

Поступающие на вход регистра импульсы последовательно переводят разряды регистра в состояние “1” начиная со старшего, при этом остальные разряды находятся в состоянии “0”. Если старший разряд находится в состоянии “1” ЦАП вырабатывает соответствующее напряжение, которое сравнивается с входным.

Если Uцап>Uвх, то по команде компаратора старший разряд регистра сбросится в “0”. Если Uцап<Uвх , то в старшем разряде останется “1”. Затем “1” появляется в следующем разряде по старшенству и снова производится сравнение. Цикл повторяется пока не произойдет сравнение в младшем разряде. Генератор останавливается и на выходе регистра появляется выходной двоичный сигнал, соответствующий входному аналоговому сигналу

(рис. 19.8).

19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

На рис. 19.9 представлена функциональная схема системы ввода-вывода аналоговой информации в компьютер. Система в минимальной конфигурации должна содержать генератор импульсов синхронизации, схему дешифрации адреса, блок АЦП, блок ЦАП и несколько внутренних регистров. Генератор вырабатывает сигнал синхронизации определен-

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

263 |

ной частоты, необходимый для функционирования системы и синхронизации всех происходящих в системе операций. В состав генератора может входить делитель частоты, осуществляющий ее деление в необходимое число раз.

Схема дешифрации адреса служит для декодирования адресных сигналов общей шины компьютера и выработки сигналов выбора внутренних регистров системы ввода-вывода, к которым центральный процессор ЦП компьютера обращается в данный момент. Блок АЦП производит преобразование аналогового сигнала в цифровой эквивалент и в многоканальных системах содержит мультиплексор входного канала. Кроме того, в состав блока входит устройство выборки-хранения, осуществляющее отключение АЦП от аналогового входа во время выполнения преобразования. Блок ЦАП производит преобразование цифрового сигнала в аналоговый эквивалент. Внутренние регистры системы осуществляют функции интерфейса с компьютером, т.е. формируют необходимые в системе сигналы управления, а также хранят преобразованную и передаваемую информацию. Рассмотрим детально принципы построения и программирования каждого из входящих в состав системы ввода-выво- да устройств.

Рис. 19.9 Функциональная схема системы ввода-вывода

Генератор сигнала синхронизации

Генератор сигнала синхронизации, входящий в состав системы ввода-вывода, позволяет сделать ее универсальной. Система ввода-вывода может быть использована в любом компьютере, независимо от его собственной рабочей частоты.

Существует большое количество всевозможных схем цифровых генераторов сигналов синхронизации, которые могут быть найдены в литературных источниках. На рис. 19.10 приведена схема простого генератора, стабилизируемого кварцевым резонатором, включающая также простой делитель частоты на четырехразрядном двоичном счетчике. Схема генератора позволяет устойчиво получать частоты от 30 кГц до 1 мГц. Выбор частоты определяется кварцевым резонатором и номиналами резисторов и конденсаторов. Делитель по-

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

264 |

зволяет разделить исходную частоту на 2, 4, 8 и 16. Необходимый коэффициент деления выбирается установкой соответствующей перемычки на выходе делителя. При необходимости получения других коэффициентов деления, они могут быть реализованы последовательным включением необходимого числа счетчиков, либо применением программируемых делителей частоты.

Схема дешифратора адреса

Система ввода-вывода представляет собой нестандартное внешнее устройство компьютера. Оно содержит определенное количество внутренних регистров с соответствующими адресами в адресном пространстве компьютера. Обращаясь по этим адресам, центральный процессор компьютера осуществляет программное управление системой ввода-вывода.

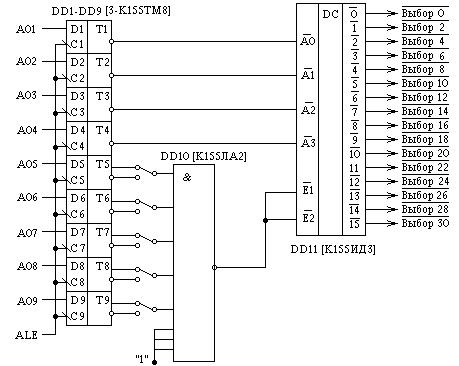

При обращении к внешнему устройству процессор устанавливает на двадцати адресных линиях общей шины А00 - А19 его адрес и сигнал синхронизации адреса ALE на соответствующей управляющей линии. Схема дешифратора адреса должна иметь возможность воспринимать этот адрес, дешифрировать его и формировать сигналы выбора соответствующих внутренних регистров системы ввода-вывода. На рис. 19.11 представлена одна из возможных схем дешифратора адреса, позволяющая формировать 16 сигналов выбора внутренних регистров. Она содержит регистр хранения адреса и собственно дешифратор. Выставленный на адресных линиях адрес записывается по сигналу ALE в регистр хранения адреса, образованный триггерами Т1 - Т9. При адресации системы ввода-вывода не используется нулевая линии адреса А00, т.к. в системе предполагается обмен информацией с компьютером целыми словами (16 бит). В качестве базового адреса системы ввода-вывода может использоваться любой свободный адрес в диапазоне адресов 000h - 3FFh (0 - 1023) адресного пространства компьютера, отведенных для внешних устройств.

Рис. 19.10. Схема генератора и делителя частоты

Вообще говоря, в IBM-совместимых компьютерах для внешних устройств отводится диапазон адресов 0000h - FFFFh (0 - 65535), но все более старшие чем 3FFh адреса в компьютерах стандартной конфигурации, как правило, не используются. Поэтому при адресации системы ввода-вывода также не используются разряды А10 - А19, т.к. обращения по более старшим чем 3FFh адресам внешних устройств в компьютерах стандартной конфигурации не происходит. При обращении по адресу любого внешнего устройства на линиях А10 - А19 устанавливается логический ноль. Следует также отметить, что в IBM компьютерах для выполнения операций обмена данными между ЦП и внешним устройством используются

два специальных управляющих сигнала IOR (чтение из внешнего устройства) и IOW (запись во внешнее устройство), которые отличны от аналогичных управляющих сигналов для обмена данными с памятью, что исключает любую нежелательную интерференцию между внешними устройствами и памятью.

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

265 |

Рис. 19.11. Схема дешифратора адреса.

Для установки базового адреса в схеме имеются переключатели. Если все переключатели установлены в верхнем положении, то элемент 8И-НЕ сработает (выдаст на выходе логический ноль) при установке на шине адреса любого из 16 адресов 3F0h - 3FFh (поскольку адресные линии А01 - А04 не подсоединены к элементу 8И-НЕ). Первый из этих адресов называется базовым и имеет индекс 0. Остальные адреса системы ввода-вывода имеют ин-

дексы 2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24, 26, 28, 30. Эти 16 имеющихся в адресов могут использоваться для обращения по крайней мере к 16 регистрам системы ввода-вывода.

Собственно дешифратор адреса преобразует четырехразрядный двоичный код А01 - А04 на входе в сигнал логического нуля на одном из 16 выходов, который и является сигналом выбора (адресации одного из 16 внутренних регистров системы ввода-вывода).

Блок АЦП

Блок АЦП содержит внутренние регистры, мультиплексор аналоговых входов, устройство выборки-хранения, собственно АЦП (рис. 19.12). К числу внутренних регистров блока кроме регистра данных АЦП отнесем также регистры управления и состояния (рис. 19.9), т.к. это необходимо для объяснения работы схемы.

В рассматриваемом достаточно общем варианте блок АЦП содержит три внутренних регистра. Перечислим их.

1) Регистр управления. Расположен по адресу: Базовый адрес + 0. Регистр доступен при записи и содержит четыре разряда, реализованные на триггерах Т1 - Т4 (DD2 - DD5). Входы регистра соединены с разрядами D00 - D03 шины данных компьютера. Биты D00 - D01 определяют в двоичном коде адрес одного из четырех каналов, которые возможно опрашивать в системе. Если D00=0, D01=0, то опрашивается нулевой канал, и т.д. В случае большего наличного числа опрашиваемых каналов число необходимых для выбора опрашиваемого канала разрядов регистра управления пропорционально увеличивается. Бит D02 определяет дифференциальный или недифференциальный ввод сигнала по выбранному каналу опроса (D02=1 - дифференциальный, D02=0 - недифференциальный). Бит D03 служит для управления режимом работы устройства выборки-хранения. Регистр управления выби-

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

266 |

рается сигналом «Выбор 0», формируемым схемой дешифратора адреса при обращении по базовому адресу системы ввода-вывода. Запись информации в регистр осуществляется при

совместном действии сигналов «Выбор 0» и IOW (запись во внешнее устройство).

2)Регистр данных АЦП расположен внутри микросхемы АЦП по адресу: Базовый адрес +

0.Он доступен при чтении и содержит двенадцать разрядов D00-D11 данных цифрового эквивалента аналогового сигнала. Регистр обладает тремя состояниями, что позволяет осуществлять связь системы ввода-вывода с компьютерной шиной. Регистр данных выбирается сигналом «Выбор 0», формируемым схемой дешифратора адреса при обращении по базовому адресу системы ввода-вывода. Чтение данных из регистра осуществляется совместным действием сигна-

лов «Выбор 0» и IOR (чтение данных из внешнего устройства).

3) Регистр состояния доступен только для чтения и расположен по адресу: Базовый адрес + 2. Регистр содержит только один разряд, устанавливаемый сигналом DR готовности данных после завершения цикла преобразования АЦП. Регистр состояния выбирается сигналом «Выбор 2», формируемым схемой дешифратора адреса при обращении по адресу «Базовый адрес + 2» системы ввода-вывода и читается совместным действием сигналов

«Выбор 2» и IOR .

Мультиплексор аналоговых сигналов осуществляет подключение ко входу АЦП канала, номер которого определяется двоичным кодом, записанным в разряды D00 - D01 регистра управления. Реализуется мультиплексор каналов на аналоговых ключах S0 - S4 (например, микросхема К590КН3), управляемых двоичным кодом. Кроме того, мультиплексор также реализует дифференциальный и недифференциальный ввод сигнала в АЦП. Режим ввода определяется разрядом D02 регистра управления и реализуется на аналоговых ключах S4, S5 (например, микросхема К590КН2). Кроме аналоговых ключей в состав мультиплексора входит операционный усилитель ОУ1, осуществляющий необходимое согласование и усиление сигнала. Четырехвходовый мультиплексор взят в схеме в качестве примера. Мультиплексор на большее число входов может быть построен аналогично. Характеристики выпускаемых отечественной промышленностью аналоговых ключей приводятся в справочнике.

Устройство выборки-хранения, состоящее в простейшем случае из аналогового ключа S6, конденсатора С и повторителя напряжения ОУ2, может работать в двух режимах - выборки и хранения. Пока триггер Т4 регистра управления сброшен (находится в нулевом состоянии), ключ S6 замкнут, а УВХ находится в режиме выборки и отслеживает поступающий на его вход аналоговый сигнал. После установки Т4 в единичное состояние S6 размыкается, а УВХ переходит в режим хранения. При этом вход АЦП отключается от аналогового входа, что предотвращает влияние быстрых изменений во входном сигнале на результаты преобразования. При этом АЦП осуществляет преобразование сигнала, который запомнил конденсатор УВХ перед размыканием ключа S6. Более детальная информация по схемотехнике и характеристикам УВХ представлена в справочниках.

АЦП осуществляет непосредственное преобразование аналогового сигнала в цифровой эквивалент. Отечественная и зарубежная промышленность выпускают большое разнообразие микросхем АЦП, отличающихся по принципу действия, исполнению и характеристикам, но имеющих подобное управление. Не привязываясь к конкретному АЦП, охарактеризуем некоторый абстрактный АЦП, имеющий исполнение и управления, присущие большинству АЦП. На вход AI АЦП подается преобразуемый сигнал с УВХ. На вход С подается сигнал синхронизации с генератора (рис. 19.10). Подача импульса логической единицы на вход ST начинает преобразование. Появление сигнала логической единицы на выходе DR указывает, что преобразование завершено, и цифровой эквивалент преобразуемого сигнала записан во внутренний регистр данных АЦП. Подача логической единицы на вход DE выводит выходы внутреннего регистра данных АЦП из высокоимпедансного состояния, что позволяет считать выходной код в шину данных компьютера. АЦП также содержит вход B/

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

267 |

U, позволяющий выбрать биполярный или однополярный ввод аналогового сигнала в АЦП. Предположим, что базовый адрес системы ввода-вывода 3F0h. Предположим, что мы хотим ввести в компьютер сигнал, подсоединенный к нулевому дифференциальному каналу мультиплексора. Чтобы сформировать требуемое подключение канала ко входу, необходимо по заданному адресу регистра управления (Базовый адрес + 0) сначала записать двоичное число «100». Запись числа по заданному адресу осуществляется программно. При этом процессор выставляет на адресных линиях адрес регистра управления «11 1111 0000», который по сигналу ALE записывается в регистр адреса (рис. 19.11). Схема дешифратора адреса формирует сигнал «Выбор 0». Сигнал записи данных во внешнее устройство сопровождается

установкой на микропроцессорной шине отрицательного сигнала IOW . Сигнал IOW совместно с сигналом «Выбор 0» осуществляет запись в регистр управления (рис. 4.5) выставленного на линиях D0 - D2 шины данных компьютера двоичного числа «100». При этом выбирается дифференциальное подключение нулевого канала ко входу АЦП (S0 - замкнут, S4 - замкнут, S5 - разомкнут). УВХ находится в режиме выборки входного сигнала (S6 - замкнут, т.к. при записи «100» в Т4 записался «0»). Затем следует по тому же адресу записать двоичное число «1100», что при неизменности подключения приведет к переводу УВХ в режим хранения (S6 - разомкнут). Установка триггера Т4 регистра управления в единичное состояние приведет к запуску ждущего одновибратора DD8, который сформирует на своем выходе положительный импульс определенной длительности, необходимой для запуска АЦП. АЦП начинает преобразование, по окончании которого на выходе DR устанавливается единичный сигнал, который сбрасывает триггер Т4 и устанавливает триггер Т5 регистра состояний. В результате УВХ опять отслеживает входной сигнал по тому же каналу, а АЦП готов к новому преобразованию. Кроме того единичный сигнал триггера Т5 сигнализирует, что результаты преобразования могут быть считаны в компьютер. Управляющая работой системы ввода-вывода программа периодически обращается по адресу «Базовый адрес + 2».

Рис. 19.12. Схема блока АЦП

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

268 |

Если при чтении по этому адресу на четвертой линии шины адреса D04 будет прочитана единица, то компьютер получает подтверждение того, что АЦП выполнил преобразование и данные могут быть считаны. После этого процессор осуществляет операцию чтения данных из внутреннего регистра АЦП, которая сопровождается формированием сигнала «Вы-

бор 0» и сигнала IOR . При этом данные из внутреннего регистра АЦП пересылаются в процессор компьютера, а также производится обнуление триггера Т5 регистра состояния. Следующий цикл преобразования и чтения данных осуществляется аналогично.

Следует отметить, что при работе системы ввода-вывода возможно использовать режим прерываний, который может быть достигнут путем формирования сигнала требования прерываний в системе к компьютеру. На схеме рис. 19.12 режим требования прерываний формируется с выхода триггера Т5 регистра состояний, который через переключатель S7 соединен с линией требования прерываний IRQ3 общей шины компьютера. Режим прерываний позволяет процессору компьютера не находиться в режиме ожидания во время выполнения преобразования АЦП, а выполнять другие задачи (расчеты).

Рассмотренная схема блока АЦП может быть существенно упрощена, т.к. существуют АЦП, содержащие УВХ и мультиплексор в одном корпусе.

Ниже представлена подпрограмма на языке Ассемблер, позволяющая запускать АЦП и читать его регистр данных.

CONTRDAT = 03F0h |

; Определяем регистр |

|

; управления/данных АЦП |

ADCRD = 03F2h |

; Определяем регистр состояния АЦП |

BIT2 = 100B |

; Определяем константы, необходимые |

BIT3 = 1000B |

; для запуска АЦП |

Val DW ? |

; Определяем переменную Val, которой |

;будет передаваться преобразованное

;значение из регистра данных АЦП

;Выбор дифференциального подключения нулевого канала

;мультиплексора

mov |

dx, |

CONTRDAT |

; Выбираем регистр CONTRDAT АЦП |

|

mov |

ax, |

BIT2 |

|

; Выбираем число 100B |

out |

dx, |

ax |

|

; и записываем его в регистр CONTRDAT |

; Перевод УВХ в режим хранения и запуск АЦП |

||||

mov |

dx, |

CONTRDAT |

; Выбираем регистр CONTRDAT АЦП |

|

sub |

ax, |

ax |

|

; Обнуляем регистр ax |

or |

ax, |

BIT2 |

|

; Записываем в регистр ax |

or |

ax, |

BIT3 |

|

; число 1100B |

out |

dx, |

ax |

|

; и записываем его в регистр CONTRDAT |

; Ожидание конца преобразования АЦП |

||||

L: |

mov |

dx, |

ADCRD |

; Выбор регистра состояния |

|

in |

ax, |

dx |

; Чтение текущего состояния ADCRD |

|

and |

ax, |

010h |

; Если текущее состояние единичное, то |

|

cmp |

ax, |

010h |

; идти к метке L |

|

je |

L |

|

; В противном случае преобразование АЦП |

;закончено и можно читать данные из АЦП

;Чтение данных из регистра данных АЦП

mov |

dx, |

CONTRDAT |

; Выбираем регистр CONTRDAT |

in |

ax, |

dx |

; Читаем данные из АЦП |

mov |

Val, |

ax |

; Присваиваем значение преобразованной |

|

|

|

; величины переменной Val |

Глава 19. Автоматические устройства ввода-вывода аналоговой информации в ЭВМ |

269 |

Блок ЦАП

В состав блока ЦАП входит регистр данных ЦАП с адресом «Базовый адрес +4» и собственно ЦАП (рис. 19.13). При выводе данных из компьютера в ЦАП управляющая работой системы ввода-вывода программа воздействует на процессор, который выставляет на адресных линиях адрес «11 1111 0100». При этом схемой дешифратора адреса формируется сигнал «Выбор 4». По выбранному адресу производится запись выводимого числа, которое записывается во внутренний регистр ЦАП. ЦАП преобразует записанное число в аналоговый ток, который с помощью операционных усилителей преобразуется в аналоговое напряжение. Фиксированное напряжение сохраняется на выходе ЦАП до момента записи во внутренний регистр ЦАП нового числа. В блоке ЦАП предусмотрена возможность вывода биполярного (БП) или униполярного (УП) напряжения.

Рис. 19.13. Схема блока ЦАП

Ниже представлена подпрограмма на языке Ассемблер записи преобразуемой величины в ЦАП.

DACDAT = 03F4h |

; Определяем регистр состояния ЦАП |

Val DW ? |

; Определяем переменную Val, которая |

;содержит преобразуемое значение

;Запись числа в регистр данных ЦАП

mov |

dx, |

DACDAT |

; Выбираем регистр данных ЦАП |

mov |

ax, |

Val |

; Заносим выводимую переменную в ax |

out |

dx, |

ax |

; и записываем ее в регистр данных ЦАП |

Таким образом, мы кратко рассмотрели принципы построения и программирования универсальной системы ввода-вывода аналоговой информации в ЭВМ и из нее, позволяющей создавать компьютерные информационно - измерительные системы, а также цифровые системы управления разнообразными объектами или процессами. Система ввода-вы- вода может быть реализована в виде универсальной платы стандартного подключения, размещаемой в одном из свободных слотов внутри корпуса компьютера и связанной с компьютером через общую шину. Универсальность системы и платы ввода-вывода заключается в том, что она может размещаться в любом IBM-PC -coвместимом компьютере и использоваться для любых задач цифрового управления или сбора и обработки информации, для которых достаточны реализованные в системе разрядность и быстродействие ввода-вывода информации. Существенным преимуществом данной концепции является возможность использования как языка ассемблера, так и языков высокого уровня для программирования и отладки программ, реализующих цифровые алгоритмы управления объектами или процессами, и программ управления системой ввода-вывода. Компьютер, используемый для задач управления и получения и обработки информации в течение ограниченных периодов времени, может быть использован для выполнения обычных задач расчетов, обработки текстов и т.д. в течение всего оставшегося времени.