- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

1. Понятие процессора, его обобщенная структура

Процессор - это центр. устройство вычисл. машины (ЭВМ), обеспечивающее обработку цифровой информации в соотв. с заданным алгоритмом.

При проектировании CPU опред-ся круг задач, для которых он предназначен. Команды и функции, которые встречаются часто, стремятся сделать аппаратно (аппаратно - это очень быстро), более редко встречающиеся - программно. CPU должен обладать алгоритмически полной системой команд.

![]()

x1-состояние ОУ

x2-команды, к-ые надо выполнить

ОУ - предст. собой совокуп-ть сумматоров, регистров, счетчиков,DC,MUX,Т и КЛС

УУ - формирует упр. возд. yi, разнесенное во времени (последов-ть импульсов). Каждый уi обеспеч. выполн. очередн. микрокоманды в ОУ.

Центр частью ОУ явл. АЛУ (ариф-лог устр).По способу представл. (организации) и обрат. инф-ции АЛУ делятся:

-ариф. с фикс (,);

- ариф. с плавающей (,);

-в D-кодах;

-операции индексной ариф-ки (работа с адресами);

-опер. спец. ариф-ки (сдвиги ариф., лог.);

- нормирование чисел;

-работа в спец. кодах;

Под одной элементарной микрооп. будем понимать одно из след. действий;

1)Записать к.-л числа в Рг/или обнуление

2)Сдвиг на 1 бит влево/вправо

3)Inc/Dec счетчика на 1

4)Работа с сумматором

5)Инверсия содержимого регистра

6)выполнение одной лог операции (+,*,не)

Если за один интервал времени можно произв. несколько м.опер, то такая совокупность м.опер. наз-ся микрокомандой(м.к.). Совокупность м.к., предназн. для выполн. одной команды, наз-ся м.программой(одна команда ассемблера).

Иерархия языков ВТ:

1)Принцип.эл.сх-мы (транз., диоды) (З-ны Кирхгофа,Ома; диффуры)

2)Лог схемы (“И”,”И-НЕ”,”ИЛИ”) (булева алгебра)

3)функц. узлы .процессора(Рг,Сч,См) (Язык м.прогр-я, машин. коды)

4)функц. узлы ЭВМ (Пр.,ПЗУ) (Ассемблер)

5)ЭВМ (ЯВУ)

6)Сеть ЭВМ (коллектив вычислителей) (яз || прогр, ОККАМ)

2. Многофункциональное арифметико-логическое устройство (алу)

Счетцик циклов - присут. в опер. *,/, в него записывают код, равный разр-ти операндов.

Аппаратные затраты многофукц. АЛУ позволяют:

1)Выполн. опер + - * / чисел с фикс(,)

2)Операции лог. обр-ки ( и, или, слож. по модулю 2, сравнение операндов)

3)Использ. Рг С и D для обработки порядков позвол. выполнять операции арифм. с плавающ(,).

Это все достигается только за счет различных последовательностей управл. возд-й (yi), разной микропрограммы управления.

3. Управляющие автоматы с жесткой логикой

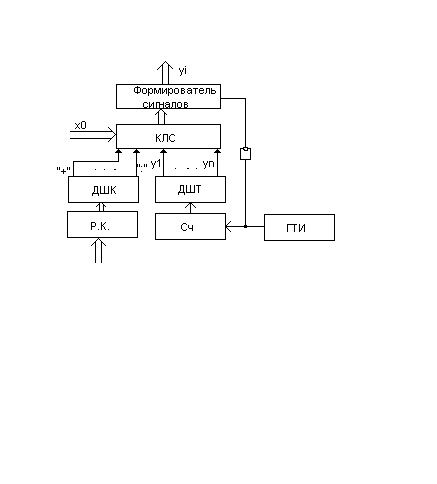

КЛС-комб.лог.схема ГТИ-генер.такт.имп ДШК-дш.команд

ДШТ-дш.тактов Р.К.-регистр ком.

Счетчик имеет коэфф пересчета = числу упр воздействий yn самой длинной ком-де,напр деление, для более коротких команд, напр + упр возд-я получаются из общего числа yn путем блокировки КЛС yi не участвующих в в выполн данной ком-ды, код ком-ды записыв в Р.К., ДШК опред тип выполн ком-ды и его выход в КЛС разрешает в КЛС прохождение только тех yi которые требуются при выполн данной ком-ды, особенность упр. авт-та с жестк лог-й все ком-ды выполн за одинаковое кол-во тактов соотв самой длинной ком-де. Если изм-ся микропрогр упр-е для выполн какой –либо одной ком-ды необходимо пересчитывать или пересинтезировать КЛС.

Условно по длительн-ти выполн все команды процессора делятся на группы (в данном случае на 2-короткие и длинные) кор=+/- лог, длинные = ком.использ.СЧ.циклов * и / итд.

Схема распр-анализир код ком и вкл Сч1 с небольшим числом упр возд yi если ком-да относится к коротким и Сч2 если ком длинная.