- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

1)Одномерный вариант.

+)Легко настраиваемая система. Каждая машина имеет доступ к памяти любой другой машины.

2)Двумерная структура

![]()

Каждая машина имеет 4 порта.

(Inmos T424) –однокрист ЭВМ

(4 порта – 2 последов и 2 паралл,

8кб ОЗУ 8кб ПЗУ на кажд крист)

Высокая надежность простота распараллеливания алгоритмов.

Университет города Пердью предложил структуру BlueChip:

ЭВМ с программируемой структурой.

![]()

Готовый набор, а конкретную структуру прожигают под конкретный алгоритм (заказ).

Новосибирская структура “Сумма” :

![]()

Минимакс:

![]()

1,2 –интерфейсы последовательные ч/з них задается как коммутация по параллельным интерфейсам 3,4. Перепрогр структура под конкр решаемые задачи.

В “Сумме” и “Минимаксе” с помощью последов интерфейсов задается коммутация по парал интерф и под каждый конкретный алгоритм система перепрограммируется.

25. Понятие прерываний, виды прерываний, контроллер прерываний

В процессе выполнения программы могут возникнуть внешние обстоятельства, требующие срочного обслуживания, или в результате выполнения команды получается неприемлемый результат (/ на 0).

Если прерывание задается аппаратно и не может быть запрещено программистом, такое прерывание называется немаскируемым. (RESET, для управ. систем - авария источника питания, прерывания по таймеру)

Маскируемые прерывания: После обслуживания внеш. события необходимо вернуться в тело осн. проги на то же самое место. Для запоминания места из содержимого РОН-а исп-ся стек. Если возникает прерывание, нужно указать на адрес, где находится подпрограмма обслуживания прерывания.

Для немаскир. прерываний эти адреса обычно фиксированы.

INT- запрос на маск. прерывание

INTA- разрешение на маск. прер-ние

ком. EI уст-ет INT=1, ком. DI: INT=0

При обслуживании запроса на прерывание ВУ, запросившее прер-е, выст-ет на ШД код команды RET.(указ. на адрес - вектор подпрограммы прер-я)

Если INTA=1 и INT=1, то пр-р заканчивает выполнение тек. ком-ы и в такте T1 след. ком-ы сбрасывает сигнал INTA=1, в ССП уст-ет бит D0=1, выставляет с-л чтения из ВУ. ВУ по D0, с-лу чтения из ВУ RDY выст-ет на ШД код к-ды RST, к-й указывает на адрес-вектор подпр-ы обработки прер-ия данного устр-ва. Пр-р в такте T2 считывает код к-ды RST с ШД, такты T3,T4 уходят на понимание и подготовку к выполнению к-ды RST, после чего реакция пр-ра на RST - это:

Обычно подпр-ма обр-ки прер-ний сохр-ет сод-мое РОН-ов и регистров признаков (в самом начале подпр-ы). В конце обр-ки прер-ний РОНы и признаки восс-ся.

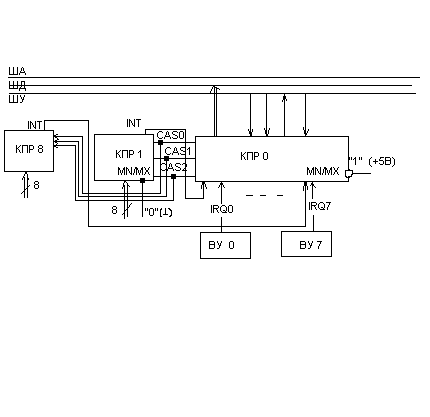

Intel 82259.

Контр прерываний (КП) предназначаен для задания адрес –векторов подпрогр обработки прерыванй от 8 до 64 (при каскадном включении контроллеров.

MN/MX-режим мин/макс включения (ведущий или ведомый)

Контроллер в процессе работы может нах-ся в одном из 3 реж:

1)Режим программирования, в этом реж-ме задается начальный адрес-вектор подпрогр обработки прерываний IRQ(0) каждое след прерывание отстоит от предыдущего на 8(16) адресов ячеек памяти. Задается вид приоритетов, разрешается или запрещается прерыв. Указ-ся что явл прерыв (полож фронт, отриц фронт, Ур 0, Ур 1). Если в системе нах-ся 1 контр то он явл ведущим и прор-ся своей группой команд если в сист-ме несколько контроллеров то ведущий котр и ведомый контр прогр по разному

Ведомый контроллер упр ведущим с помощью сигнала CAS0-CAS2, а их запрос на прерывание JNT поступает на один входов ведущего контроллера (а не на ЦП как у ведущего контр).

2)Режим обслуживания прерываний по опросу.

В режиме по опросу ЦП может периодически опрашивать регистр запросов и смотреть какие из ВУ требуют прерывания. Прогр высокого уровня сама определяет приоритеты и необх обслуживания поступивших запросов.

3)Режим обслуживания по запросу. ВУ выставляет запрос на прерыв ктр запоминв рег-ре запросов. Схема приоритетов и маскирования выбирает из всех поступивших запросов прерывания с высшим приоритетом, разрешенного для обслуживания. Это прерыв поступает в рег обрабатываемого запроса( РгОЗ). БФ формирует запрос на прерыв JNT=0 для ЦП. Если прерыв было разрешено на длинном участке прогр то ЦП преступает к обработке прерываний, устанавливая сигнал JNTE=0 (только после того как закончит выполнение команды). Получив сигнал JNTE=0 контр прерываний выставляет на ШД для ЦП код команды CALL (вызов подпрогр) после чего ЦП 2 раза дергает сигнал JNTE чтобы получить 16-разр адрес с 8 разр ШД. По 1 фронту выдается младший байт адреса подпрогр обработки прерыв , по2-му старший. В подпрогр о\обр прерыв в общем случае другие прерыв запрещены (вложенных прерыв нет) их можно разрешить специально) возвратиз подпрогр заканчивается командой RETI, которая разрешает следующее прерывание.