- •1. Понятие процессора, его обобщенная структура

- •2. Многофункциональное арифметико-логическое устройство (алу)

- •3. Управляющие автоматы с жесткой логикой

- •4.Управляющие автоматы с микропрограммным управленим (мпу)

- •5. Организация модулей пзу

- •6. Организация модулей статического озу

- •16-Ти разрядные модули памяти

- •7. Организация динамического модуля памяти (дозу)

- •8. Классификация вычислительных систем по Флинну

- •9. Машины, управляемые потоком данных (df-машины)

- •10.Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •11.Общие принципы построения risc-процессоров. Особенности Старнфордской архитектуры.

- •12. Кэш-память.

- •13. Виртуальная память.

- •14. Синхронный способ подключения ву к см

- •15. Асинхронный способ подключения ву к см

- •16. Требования к кодам команд и способы кодирования микрокоманд

- •17. Организация эвм типа ibm pc (at)

- •18. Процессор Pentium

- •19. Pentium II (Pentium Pro)

- •20. Процессор Pentium IV

- •21. Структуры вс с общей шиной, каждый с каждым, дублированная шина и кольцо

- •22. Структуры вс древовидные, «почтовый ящик» и многопортовое озу

- •23. Архитектуры вс типа Сммр, Сvмр

- •24. Архитектуры вс типа Сm, Blue Chip, минимакс и сумма

- •25. Понятие прерываний, виды прерываний, контроллер прерываний

- •26. Режим прямого доступа к памяти и контролер пдп (кпдп)

- •27. Параллельно программируемый интерфейс (ппи), подключение ву (организация м/о) с помощью ппи

- •28. Однокристальные микро-эвм (оэвм), обобщенная архитектура, основные функциональные узлы (можно на примере mcs-51 или Atmega32)

- •29. Подключение модулей дозу к см. Способы регенерации

- •30. Понятие интерфейса. Виды арбитража

4.Управляющие автоматы с микропрограммным управленим (мпу)

КОП-код операции qi-сост упр автомата (адр след МК)(КОП-const,

xi-const) ОУ- операционное устройство.

Код команды процессора записыв-ся в Рг.МК , этот код здает в Рг.Адр.МК область памяти ЗУ в ктр прошита МПрогр данной ком, соотв-но для каждого вида операций(другого кода ком-ды) в памяти МП выделяется своя область т.к. при выполн. МП в зависимости от признаков сост ОУ xi формир разл последов упр возд yi,то они так же оказыв влияние на адрес формиров-я след-го yi т.к. при неизменном коде опер и условиях xi возникает необход в формиров последов-ти yi , то в ЗУ прописыв-ся адрес следующ yi (адрес qi)которое формируется на следующ шаге (программный счетчик). Если в качестве ЗУ использ ПЗУ то процессор имеет жестко заданную сист команд (все микропроц-ры широкого прим так и работают) но в общем случае в место ПЗУ можно использ ОЗУ тогда проц-р можно перенастраивать под различные сист-мы команд (напр сделать совместными проги под Intel и Motorola (Mac)).

Достоинства: 1)Каждая ком имеет свою область памяти микропрограмм(измен одной ком не приводит к необх переделки остальн ком) 2)Для выполн каждой ком-ды выделяется столько времени сколько необх-мо (длительности выполн всех команд различны и минимальны)

5. Организация модулей пзу

Пусть требуется подкл модуль 24 kb начиная с 0 адр, состоящий из микросх 8кх8 (нужно 3 м.сх.)

![]()

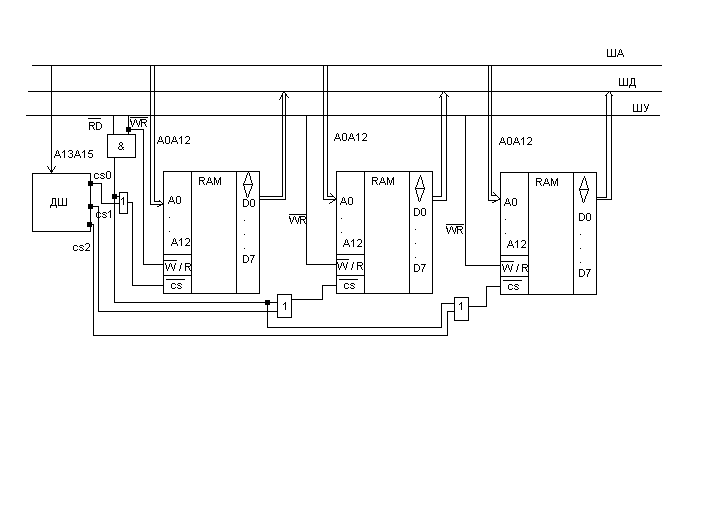

6. Организация модулей статического озу

1)Рис карту адресного простр

2)Опр область вкл каждой микросх на карте адр простр-ва . Для каждой микросх строится ДШ на опр комб ША (на ДШ поступают старш разр с ША,а младш поступ на микросх ОЗУ)

![]()

![]() 8-ми разрядные

модули памяти

8-ми разрядные

модули памяти

16-Ти разрядные модули памяти

ВНЕ- выборка старшего байта.

|

ВНЕ |

А0 |

|

0 |

0 |

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

16-разр слово

старший байт

младший байт

нет обр-я

При обращении к 16 разр ШД в ШУ присутсвует сигнал ВНЕ, ктр в комбина-ции с Ао обеспеч-ивает обр-е к 16 разр слову отдельно млад или отдельно старш байту.Счетчик комнд после обрпо адресу автом увел на два (слова располагаются по четным адр т.е. Ао=0).

7. Организация динамического модуля памяти (дозу)

В ДОЗУ одна ячейка памяти строится на одном полевом транзисторе (в статических ОЗУ на одну ячейку памяти прих 2 тр)

![]()

в ДОЗУ хранение инф обеспечив за счет наличия заряда на паразит-ной емкости затвора-истока. Инф в динам ячейке ч/з какое-то время пропадает за счет рассеивания заряда из-за сопротивл этой емкости. Чтобы этого не происходило инф в ДОЗУ периодически восстанавл (регенерируется) t м/у интерва регенерации для совр микросх ДОЗУ составл 8-16 мс. Регенер обычно осущ подачей напряжения питания на транз ячейки (если U есть инф восст).

![]()

RAS – строк сопровожд адр строки

CAS – строк сопровожд адр столбца

На ША контроллером ДО ЗУ выставл адр стр Ах и защелкивает-ся отриц фронтом сигнала RAS в Рг

ДОЗУ, затем контроллер ДОЗУ выставл на ША адр столбща Ау ктр защелк по отриц фронту сигн СAS, RAS=0 и CAS=0 ; вкл микр в работу и она анализир сигналы W/R и в завис от него считывает инф с ШД в себя или выдает на ШД. Появл CAS и RAS =1 переводит ее выход по ШД в 3 сост. Для того чтобы вызвать регене-рацию (в завис от типа микросх) сущ неск способов:

1)Only RAS

![]()

2)Обычно использ в встр счетчиком адреса регенер и наз-ся CAS before RAS