Система команд 8-ми разрядных RISC микроконтроллеров AVR

.pdf

ÊÒÖ-ÌÊ

Наши координаты:

Москва, 1-й Щемиловский пер, 16, 2 подъезд, 2 этаж Тел.: (095) 972 3416, 973 1855, 973 1923, факс 973 1864 E-mail: cec-mc@mega.ru

Наш сервер http://www.cec-mc.ru

ПОЛНЫЙ КОМПЛЕКС РАЗРАБОТКИ ЭЛЕКТРОННЫХ ИЗДЕЛИЙ ЛЮБОЙ СЛОЖНОСТИ, ВКЛЮЧАЮЩИЙ В СЕБЯ ИЗГОТОВЛЕНИЕ ОПЫТНОГО ОБРАЗ ЦА

ПРОИЗВОДСТВО ИЗДЕЛИЙ ПО ТЕХНИЧЕСКОЙ ДОКУМЕНТАЦИИ ЗАКАЗ ЧИКА

ПРОЕКТИРОВАНИЕ ПЕЧАТНЫХ ПЛАТ ЛЮБОЙ СЛОЖНОСТИ КАК С ПРИНЦИПИАЛЬНОЙ СХЕМЫ, ТАК И ИСПОЛНЕНИЕ ПРОЕКТА С ТЕХНИЧЕСКОГО ЗАДАНИЯ

ИЗГОТОВЛЕНИЕ ПЕЧАТНЫХ ПЛАТ ДО 5 КЛАССА, ДО 24 СЛОЕВ, С ПОЛНЫМ ЭЛЕКТРОКОНТРОЛЕМ

МОНТАЖ ПЕЧАТНЫХ ПЛАТ ЛЮБОЙ СЛОЖНОСТИ ВКЛЮЧАЯ ПОВЕРХНОСТНЫЙ, В ТОМ ЧИСЛЕ КОРПУСОВ BGA

ИЗГОТОВЛЕНИЕ ШТАМПОВАННЫХ И ФРЕЗЕРОВАННЫХ КОРПУСОВ ДЛЯ ПРОМЫШЛЕННОЙ АППАРАТУРЫ

КОМПЛЕКСНЫЕ ПОСТАВКИ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ ДЛЯ ВЫПУСКАЕМЫХ ИЗДЕЛИЙ

165

ATMEL |

ÊÒÖ-ÌÊ |

СИСТЕМА КОМАНД

8-РАЗРЯДНЫХ RISC МИКРОКОНТРОЛЛЕРОВ

СЕМЕЙСТВА AVR

166

ÊÒÖ-ÌÊ

Система команд 8-разрядных RISC микроконтроллеров семейства AVR.

Принятые обозначения

Регистр статуса (SREG): SREG: Регистр статуса

C:Флаг переноса

Z:Флаг нулевого значения

N:Флаг отрицательного значения

V:Флаг-указатель переполнения дополнения до двух

S:N V, Для проверок со знаком

V, Для проверок со знаком

H:Флаг полупереноса

T:Флаг пересылки, используемый

командами BLD и BST

I:Флаг разрешения/запрещения глобального прерывания

Регистры и операнды:

Rd: |

Регистр назначения (и источник) в |

|

регистровом файле |

Rr: |

Регистр источник в регистровом файле |

R:Результат выполнения команды

K:Литерал или байт данных (8 бит)

k:Данные адреса константы для счетчика программ

b:Бит в регистровом файле или I/O

регистр (3 бита)

s:Бит в регистре статуса (3 бита)

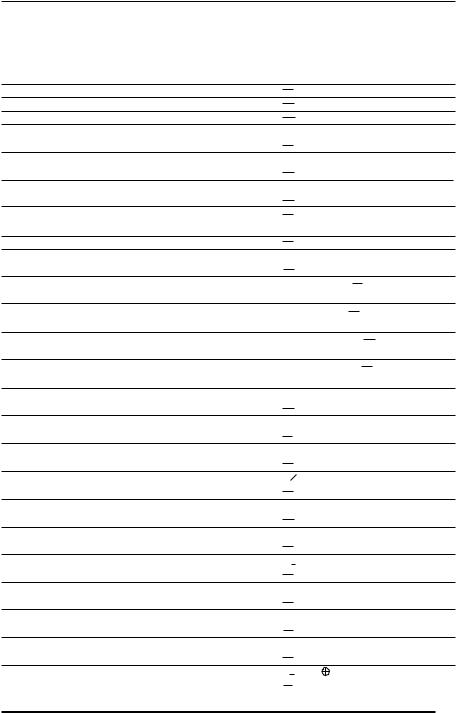

Сводная таблица условных переходов

X, Y, Z: Регистр косвенной адресации (X=R27:R26, Y=R29:R28, Z=R31:R30)

P:Адрес I/O порта

q:Смещение при прямой адресации (6 бит)

I/O регистры

RAMPX, RAMPY, RAMPZ: Регистры связанные с X, Y и Z регистрами, обеспечивающие косвенную адресацию всей области СОЗУ микроконтроллера с объемом СОЗУ более 64 Кбайт.

Ñòåê:

STACK: Стек для адреса возврата и опущенных в стек регистров

SP: Указатель стека

Флаги:

<=> Флаг, на который воздействует команда

0: Очищенный командой Флаг

1: Установленный командой флаг -: Флаг, на который не воздействует

команда

Тестирование |

Булево |

|

|

Мнемоника |

Комплементарное |

Булево |

Мнемоника |

Комментарий |

||||||||||||||||||

условия |

выражение |

|

условие |

выражение |

|

|

||||||||||||||||||||

Rd > Rr |

Z (N |

|

|

|

V)=0 |

BRLT* |

Rd < Rr |

Z+(N |

|

|

|

V)=1 |

BRGE* |

Со знаком |

||||||||||||

Rd > Rr |

(N |

|

|

V)=0 |

BRGE |

Rd < Rr |

(N |

|

|

V)=1 |

BRLT |

Со знаком |

||||||||||||||

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

||||||||||||||||||||||

Rd = Rr |

Z=1 |

|

|

|

|

|

|

|

|

|

BREQ |

Rd = Rr |

Z=0 |

|

|

|

|

BRNE |

Со знаком |

|||||||

Rd |

< |

Rr |

Z+(N |

|

|

|

|

|

|

|

V)=1 |

BRGE* |

Rd > Rr |

Z N |

|

|

|

V)=0 |

BRLT* |

Со знаком |

||||||

Rd < Rr |

(N |

|

|

V)=1 |

BRLT |

Rd > Rr |

(N |

|

|

|

|

V)=0 |

BRGE |

Со знаком |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rd > Rr |

C+Z=0 |

BRLO* |

Rd < Rr |

C+Z=1 |

BRSH* |

Без знака |

||||||||||||||||||||

Rd > Rr |

C=0 |

|

|

|

|

|

|

|

|

|

BRSH/BRCC |

Rd < Rr |

C=1 |

|

|

|

|

BRLO/BRCS |

Без знака |

|||||||

Rd = Rr |

Z=1 |

|

|

|

|

|

|

|

|

|

BREQ |

Rd = Rr |

Z=0 |

|

|

|

|

BRNE |

Без знака |

|||||||

Rd |

< |

Rr |

C+Z=1 |

BRSH* |

Rd > Rr |

C+Z=0 |

BRLO* |

Без знака |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rd < Rr |

C=1 |

|

|

|

|

|

|

|

|

|

BRLO/BRCS |

Rd > Rr |

C=0 |

|

|

|

|

BRSH/BRCC |

Без знака |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Перенос |

C=1 |

|

|

|

|

|

|

|

|

|

BRCS |

Нет переноса |

C=0 |

|

|

|

|

BRCC |

Простой |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Отрицательное |

N=1 |

|

|

|

|

|

|

|

|

|

BRMI |

Положительное |

N=0 |

|

|

|

|

BRPL |

Простой |

|||||||

значение |

|

|

|

|

|

|

|

|

|

|

|

|

значение |

|

|

|

|

|

|

|

|

|

|

|

||

Переполнение |

V=1 |

|

|

|

|

|

|

|

|

|

BRVS |

Нет переполнения |

V=0 |

|

|

|

|

BRVC |

Простой |

|||||||

Нулевое значение |

Z=1 |

|

|

|

|

|

|

|

|

|

BREQ |

Не нулевое значение |

Z=0 |

|

|

|

|

BRNE |

Простой |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

* Смена Rd и Rr при операции перед тестированием, т.е. CP Rd,Rr > CP Rr,Rd

167

ATMEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

ÊÒÖ-ÌÊ |

Арифметические и логические команды |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Ìíåì- |

Îïåð- |

Описание |

Операция |

Флаги |

Ê-âî |

|||||||||

оника |

àíäû |

|

|

|

|

|

|

|

|

|

|

|

|

öèê- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ëîâ |

|

|

|

|

|

|

|

||||||||

ADD |

Rd,Rr |

Add without Carry - |

Rd< |

Rd + Rr |

Z,C,N,V,H |

1 |

||||||||

|

|

Сложить без переноса |

|

|

|

|

|

|

|

|

|

|

|

|

ADC |

Rd,Rr |

Add with Carry - Сложить с переносом |

Rd< |

Rd + Rr + C |

Z,C,N,V,H |

1 |

||||||||

ADIW |

Rd,K |

Add Immediate to WordСложить |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

непосредственное значение со словом |

Rdh:Rdl< |

Rdh:Rdl + K |

Z,C,N,V |

2 |

||||||||

SUB |

Rd,Rr |

Subtract without Carry - |

Rd< |

Rd - Rr |

Z,C,N,V,H |

1 |

||||||||

|

|

Вычесть без переноса |

|

|

|

|

|

|

|

|

|

|

|

|

SUBI |

Rd,K |

Subtract Immediate - Вычесть |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

непосредственное значение |

Rd< Rd - K |

Z,C,N,V,H |

1 |

|||||||||

SBC |

Rd,Rr |

Subtract with Carry - Вычесть с переносом |

Rd< |

Rd - Rr - C |

Z,C,N,V,H |

1 |

||||||||

SBCI |

Rd,K |

Subtract Immediate with Carry - Вычесть |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

непосредственное значение с переносом |

Rd< |

Rd - K - C |

Z,C,N,V,H |

1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SBIW |

Rd,K |

Subtract Immediate from WordВычесть |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

непосредственное значение из слова |

Rdh:Rdl< Rdh:Rdl - K |

Z,C,N,V |

2 |

|||||||||

|

|

|

|

|

|

|

|

|

||||||

AND |

Rd,Rr |

Logical ANDВыполнить логическое AND |

Rd< |

Rd |

|

Rr |

Z,N,V |

1 |

||||||

ANDI |

Rd,K |

Logical AND with Immediate- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить логическое AND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c непосредственным значением |

Rd< |

Rd |

|

K |

Z,N,V |

1 |

||||||

|

|

|

|

|

|

|

||||||||

OR |

Rd,Rr |

Logical OR - Выполнить логическое OR |

Rd< |

Rd v Rr |

Z,N,V |

1 |

||||||||

ORI |

Rd,K |

Logical OR with Immediate - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить логическое OR с |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

непосредственным значением |

Rd< |

Rd v K |

Z,N,V |

1 |

||||||||

EOR |

Rd,Rr |

Exclusive OR - Выполнить |

Rd< |

Rd |

|

|

|

|

|

Rr |

Z,N,V |

1 |

||

|

|

исключающее OR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COM |

Rd |

One’s Complement - Выполнить |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

дополнение до единицы |

Rd< $FF - Rd |

Z,C,N,V |

1 |

|||||||||

NEG |

Rd |

Two’s Complement - Выполнить |

Rd< |

$00 - Rd |

Z,C,N,V,H |

1 |

||||||||

|

|

дополнение до двух |

|

|

|

|

|

|

|

|

|

|

|

|

SBR |

Rd,K |

Set Bits in Register- |

Rd< |

Rd v K |

Z,N,V |

1 |

||||||||

|

|

Установить биты в регистре |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

CBR |

Rd,K |

Clear Bits in Register - |

Rd< |

Rd |

($FF - K) |

Z,N,V |

1 |

|||||||

|

|

Очистить биты в регистре |

|

|

|

|

|

|

|

|

|

|

|

|

INC |

Rd |

Increment - Инкрементировать |

Rd< |

Rd + 1 |

Z,N,V |

1 |

||||||||

DEC |

Rd |

Decrement - Декрементировать |

Rd< Rd - 1 |

Z,N,V |

1 |

|||||||||

TST |

Rd |

Test for Zero or Minus - |

Rd< |

Rd |

|

|

|

|

|

Rd |

Z,N,V |

1 |

||

|

|

Проверить на ноль или минус |

|

|

|

|

|

|

|

|

|

|

|

|

CLR |

Rd |

Clear Register- Очистить регистр |

Rd< |

Rd |

|

|

|

|

|

|

Rd |

Z,N,V |

1 |

|

|

|

|

|

|

|

|

||||||||

SER |

Rd |

Set all bits in Register- |

Rd< |

$FF |

Íåò |

1 |

||||||||

|

|

Установить все биты регистра |

|

|

|

|

|

|

|

|

|

|

|

|

CP |

Rd,Rr |

CompareСравнить |

Rd |

- Rr |

|

|

|

|

|

|

|

Z,C,N,V,H |

1 |

|

CPC |

Rd,Rr |

Compare with Carry - |

Rd - Rr - C |

Z,C,N,V,H |

1 |

|||||||||

|

|

Сравнить с учетом переноса |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CPI |

Rd,K |

Compare with Immediate- |

Rd - K |

|

|

|

|

|

|

|

Z,C,N,V,H |

1 |

||

|

|

Сравнить c константой |

|

|

|

|

|

|

|

|

|

|

|

|

168

ÊÒÖ-ÌÊ

Команды переходов

Ìíå- |

Îïå- |

Описание |

Операция |

|

Ôëà- |

Ê-âî |

|

ìîíè- |

ðàí- |

|

|

|

|

ãè |

öèê- |

êà |

äû |

|

|

|

|

|

ëîâ |

RJMP |

k |

RelativeJump-Перейтиотносительно |

PC< PC + k + 1 |

|

Íåò |

2 |

|

IJMP |

|

Indirect JumpПерейти косвенно |

PC< |

Z |

|

Íåò |

2 |

JMP |

k |

JumpПерейти |

PC< |

k |

|

Íåò |

3 |

RCALL |

k |

Relative Call to Subroutine - Вызвать |

|

|

|

|

|

|

|

подпрограмму относительно |

PC< |

PC + k + 1 |

|

Íåò |

3 |

ICALL |

|

Indirect Call to Subroutine - Вызвать |

|

|

|

|

|

|

|

подпрограмму косвенно |

PC< |

Z |

|

Íåò |

3 |

CALL |

k |

Long Call to a Subroutine - Выполнить |

|

|

|

|

|

|

|

длинный вызов подпрограммы |

PC< |

k |

|

Íåò |

4 |

RET |

|

Return from Subroutine - |

PC< |

STACK |

|

Íåò |

4 |

|

|

Вернуться из подпрограммы |

|

|

|

|

|

RETI |

|

Return from InterruptВернуться из прерывания |

PC< |

STACK |

|

I |

4 |

CPSE |

Rd,Rr |

Compare Skip if EqualСравнить и |

If Rd = Rr then |

|

|

|

|

|

|

пропустить если равно |

PC< |

PC + 2 (or 3), |

|

Íåò |

1/2/3 |

SBRC |

Rr,b |

Skip if Bit in Register is ClearedПропустить |

If Rr (b) = 0 then PC< |

PC |

|

|

|

|

|

если бит в регистре очищен |

+ 2 (or 3) |

|

Íåò |

1/2/3 |

|

SBRS |

Rr,b |

Skip if Bit in Register is SetПропустить |

If Rr(b) = 1 then PC< |

PC |

|

|

|

|

|

если бит в регистре установлен |

+ 2 (or 3) |

|

Íåò |

1/2/3 |

|

SBIC |

P,b |

Skip if Bit I/O Register is Cleared - Пропустить |

If I/O(P,b) = 0 then PC< |

|

|

||

|

|

если бит в регистре I/O очищен |

PC + 2 (or 3) |

|

Íåò |

1/2/3 |

|

SBIS |

P,b |

Skip if Bit I/O Register is SetПропустить |

If I/O(P,b) = 1 then PC< |

|

|

||

|

|

если бит в регистре I/O установлен |

PC + 2 (or 3) |

|

Íåò |

1/2/3 |

|

BRBS |

s,k |

Branch if Bit in SREG is SetПерейти если |

If SREG(s) = 1 then |

|

|

|

|

|

|

бит в регистре статуса установлен |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRBC |

s,k |

Branch if Bit in SREG is Cleared - Перейти |

If SREG(s) = 0 then |

|

|

|

|

|

|

если бит в регистре статуса очищен |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BREQ |

k |

Branch if EqualПерейти если равно |

If Rd = Rr (Z = 1) then |

|

|

|

|

|

|

|

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRNE |

k |

Branch if Not EqualПерейти если не равно |

If Rd = Rr (Z = 0) then |

|

|

|

|

|

|

|

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRCS |

k |

Branch if Carry SetПерейти если флаг |

If Ñ= 1 then |

|

|

|

|

|

|

переноса установлен |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRCC |

k |

Branch if Carry ClearedПерейти если |

If Ñ= 0 then |

|

|

|

|

|

|

флаг переноса очищен |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRSH |

k |

Branch if Same or Higher (Unsigned) - Перейти |

If Rd > Rr (C = 0) then |

|

|

|

|

|

|

если равно или больше (без знака) |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRLO |

k |

Branch if Lower (Unsigned) - Перейти если |

If Rd < Rr (C = 1) then |

|

|

|

|

|

|

меньше (без знака) |

PC< |

PC + k +1 |

|

Íåò |

1/2 |

BRMI |

k |

Branch if Minus - Перейти если минус |

If N = 1 then |

|

Íåò |

1/2 |

|

|

|

|

PC< |

PC + k +1 |

|

|

|

BRPL |

k |

Branch if PlusПерейти если плюс |

If N = 0 then |

|

Íåò |

1/2 |

|

|

|

|

PC< |

PC + k +1 |

|

|

|

BRGE |

k |

Branch if Greater or Equal (Signed)- Перейти |

f Rd > Rr (N V = 0) then |

|

|

||

|

|

еслибольшеилиравно(сучетомзнака) |

PC< PC + k +1 |

|

Íåò |

1/2 |

|

|

|

|

|

|

|

|

|

169

ATMEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ÊÒÖ-ÌÊ |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BRLT |

|

k |

|

BranchifLessThen(Signed)-Перейти |

|

If Rd < Rr (N |

V |

|

= 1) |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

еслименьшечем(сознаком) |

|

then PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRHS |

|

k |

|

Branch if Half Carry Flag is SetПерейти если |

|

If H = 1 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

флагполупереносаустановлен |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BRHC |

|

k |

|

Branch if Half Carry Flag is Cleared - Перейти |

|

If H = 0 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

еслифлагполупереносаочищен |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRTS |

|

k |

|

Branch if T Flag is SetПерейти если |

|

If T = 1 then |

|

|

|

|

|

|

|

Íåò |

1/2 |

|||

|

|

|

|

флагTустановлен |

|

PC< PC + k +1 |

|

|

|

|

|

|

||||||

BRTC |

|

k |

|

Branch if T Flag is ClearedПерейти |

|

If T = 0 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

если флаг T очищен |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRVS |

|

k |

|

BranchifOverflowSet-Перейтиесли |

|

If V = 1 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

переполнениеустановлено |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRVC |

|

k |

|

BranchifOverflowCleared-Перейтиесли |

|

If V = 0 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

переполнениеочищено |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRIE |

|

k |

|

Branch if Global Interrupt is Enabled - Перейти |

|

If I = 1 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

еслиглобальноепрерываниеразрешено |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

BRID |

|

k |

|

Branch if Global Interrupt is Disabled - Перейти |

|

If I = 0 then |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

еслиглобальноепрерываниезапрещено |

|

PC< PC + k +1 |

|

|

Íåò |

1/2 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Команды пересылки данных |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ìíå- |

|

Îïåð- |

Описание |

|

|

|

|

|

Операция |

|

Ôëà- |

Ê-âî |

||||||

ìîíè- |

àíäû |

|

|

|

|

|

|

|

|

|

|

|

|

ãè |

|

öèê- |

||

êà |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ëîâ |

ELPM |

|

|

|

Extended Load ProgramMemoryРасширенная загрузка |

|

|

|

R0 |

< |

(Z+RAMPZ) |

Íåò |

|

3 |

|||||

|

|

|

|

|

памяти программ |

|

|

|

|

|

|

|

|

|

|

|

|

|

MOV |

Rd,Rr |

|

CopyRegister-Копироватьрегистр |

|

|

|

|

Rd< |

Rr |

|

Íåò |

|

1 |

|||||

LDI |

Rd,K |

|

LoadImmediate-Загрузитьнепосредственноезначение |

|

|

|

|

Rd< |

K |

|

Íåò |

|

1 |

|||||

LDS |

Rd,k |

|

Load Direct from RAM - |

|

|

|

|

Rd< |

(k) |

|

Íåò |

|

3 |

|||||

|

|

|

|

|

ЗагрузитьнепосредственноизСОЗУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

Rd,X |

|

LD-LoadIndirect-Загрузитькосвенно |

|

|

|

|

Rd< |

(X) |

|

Íåò |

|

2 |

|||||

LD |

Rd,X+ |

|

LoadIndirectandPost-Increment-Загрузить |

|

|

|

|

Rd< |

(X), |

|

|

|

|

|||||

|

|

|

|

|

косвенноинкрементироваввпоследствии |

|

|

|

|

|

X< |

X + 1 |

|

Íåò |

|

2 |

||

LD |

Rd,-X |

|

LoadIndirectandPre-Decrement-Загрузить |

|

|

|

|

X< X - 1, |

|

|

|

|

||||||

|

|

|

|

|

косвеннодекрементировавпредварительно |

|

|

|

|

Rd< |

(X) |

|

Íåò |

|

2 |

|||

LD |

Rd,Y |

|

LoadIndirect-Загрузитькосвенно |

|

|

|

|

Rd< |

(Y) |

|

Íåò |

|

2 |

|||||

LD |

Rd,Y+ |

|

LoadIndirectandPost-Increment-Загрузить |

|

|

|

|

Rd< |

(Y), |

|

|

|

|

|||||

|

|

|

|

|

косвенноинкрементироваввпоследствии |

|

|

|

|

|

Y< |

Y + 1 |

|

Íåò |

|

2 |

||

LD |

Rd,-Y |

|

LoadIndirectandPre-Decrement-Загрузить |

|

|

|

|

Y< Y - 1, |

|

|

|

|

||||||

|

|

|

|

|

косвеннодекрементировавпредварительно |

|

|

|

|

Rd< |

(Y) |

|

Íåò |

|

2 |

|||

LDD |

Rd,Y+q |

|

LoadIndirectwithDisplacement- |

|

|

|

|

Rd< |

(Y + q) |

|

Íåò |

|

2 |

|||||

|

|

|

|

|

Загрузитькосвеннососмещением |

|

|

|

|

|

|

|

|

|

|

|

|

|

LD |

Rd,Z |

|

LoadIndirect-Загрузитькосвенно |

|

|

|

|

Rd< |

(Z) |

|

Íåò |

|

2 |

|||||

LD |

Rd,Z+ |

|

LoadIndirectandPost-Increment-Загрузить |

|

|

|

|

Rd< |

(Z), |

|

|

|

|

|||||

|

|

|

|

|

косвенноинкрементироваввпоследствии |

|

|

|

|

|

Z< |

Z + 1 |

|

Íåò |

|

2 |

||

LD |

Rd,-Z |

|

LoadIndirectandPre-Decrement-Загрузить |

|

|

|

|

Z< Z - 1, |

|

|

|

|

||||||

|

|

|

|

|

косвеннодекрементировавпредварительно |

|

|

|

|

Rd< |

(Z) |

|

Íåò |

|

2 |

|||

LDD |

Rd,Z+q |

|

LoadIndirectwithDisplacement- |

|

|

|

|

Rd< |

(Z + q) |

|

Íåò |

|

2 |

|||||

|

|

|

|

|

Загрузитькосвеннососмещением |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

170

ÊÒÖ-ÌÊ

STS |

k,Rr |

|

StoreDirecttoRAM-ЗагрузитьнепосредственновСОЗУ |

|

|

|

|

|

(k)< Rr |

|

|

|

Íåò |

3 |

|||

ST |

X,Rr |

|

StoreIndirect-Записатькосвенно |

|

|

|

|

|

(X)< Rr |

|

|

|

Íåò |

2 |

|||

ST |

X+,Rr |

|

StoreIndirectandPost-Increment-Записать |

|

|

|

|

|

(X)< Rr, |

|

|

|

|

|

|

||

|

|

|

|

косвенно инкрементировав впоследствии |

|

|

|

|

|

X< |

X + 1 |

|

Íåò |

2 |

|||

ST |

-X,Rr |

|

Store Indirect and Pre-Decrement - Записать |

|

|

|

|

|

X< |

X - 1, |

|

|

|

|

|||

|

|

|

|

косвенно декрементировав предварительно |

|

|

|

|

|

(X)< |

Rr |

|

|

|

Íåò |

2 |

|

ST |

Y,Rr |

|

Store Indirect - Записать косвенно |

|

|

|

|

|

(Y)< |

Rr |

|

|

|

Íåò |

2 |

||

ST |

Y+,Rr |

|

Store Indirect and Post-Increment - Записать |

|

|

|

|

|

(Y) < |

Rr, |

|

|

|

|

|

|

|

|

|

|

|

косвенно инкрементировав впоследствии |

|

|

|

|

|

Y< |

Y + 1 |

|

Íåò |

2 |

|||

ST |

-Y,Rr |

|

Store Indirect and Pre-Decrement - Записать |

|

|

|

|

|

Y< Y - 1, |

|

|

|

|

|

|

||

|

|

|

|

косвенно декрементировав предварительно |

|

|

|

|

|

(Y)< |

Rr |

|

|

|

Íåò |

2 |

|

STD |

Y+q,Rr |

|

Store Indirect with Displacement - |

|

|

|

|

|

(Y + q)< |

Rr |

|

Íåò |

2 |

||||

|

|

|

|

Записать косвенно со смещением |

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

Z,Rr |

|

Store Indirect - Записать косвенно |

|

|

|

|

|

(Z)< |

Rr |

|

|

|

Íåò |

2 |

||

ST |

Z+,Rr |

|

Store Indirect and Post-Increment - Записать |

|

|

|

|

|

(Z)< |

Rr, |

|

|

|

|

|

|

|

|

|

|

|

косвенно инкрементировав впоследствии |

|

|

|

|

|

Z< |

Z + 1 |

|

Íåò |

2 |

|||

ST |

-Z,Rr |

|

Store Indirect and Pre-Decrement - Записать |

|

|

|

|

|

Z< Z - 1, |

|

|

|

|

|

|

||

|

|

|

|

косвенно декрементировав предварительно |

|

|

|

|

|

(Z)< |

Rr |

|

|

|

Íåò |

2 |

|

STD |

Z+q, Rr |

|

Store Indirect with Displacement - |

|

|

|

|

|

(Z + q)< |

Rr |

|

Íåò |

2 |

||||

|

|

|

|

Записать косвенно со смещением |

|

|

|

|

|

|

|

|

|

|

|

|

|

LPM |

|

|

Load Program Memory - Загрузить байт памяти программ |

|

|

|

R0< |

(Z) |

|

|

|

Íåò |

3 |

||||

IN |

Rd,P |

|

Load an I/O Port to Register - Загрузить данные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

из порта I/O в регистр |

|

|

|

|

|

Rd< |

P |

|

|

|

Íåò |

1 |

|

OUT |

P,Rr |

|

Store Register to I/O port - Записать данные |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

из регистра в порт I/O |

|

|

|

|

|

P< |

Rr |

|

|

|

Íåò |

1 |

|

PUSH |

Rr |

|

Push Register on Stack - Поместить регистр в стек |

|

|

|

|

|

STACK< |

Rr |

|

Íåò |

2 |

||||

POP |

Rd |

|

Pop Register from Stack - Загрузить регистр из стека |

|

|

|

|

Rd< |

STACK |

|

Íåò |

2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

По-битовые команды и команды тестирования битов |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Ìíå- |

|

Опера |

Описание |

Операция |

|

|

Флаги |

|

Ê-âî |

||||||||

ìî- |

|

íäû |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

öèê- |

íèêà |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ëîâ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

LSL |

|

Rd |

Logical Shift LeftЛогически сдвинуть влево |

Rd(n+1)< |

|

|

Rd(n), |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

Rd(0)< |

0, C< |

Rd(7) |

|

Z,C,N,V,H |

1 |

|||||||

LSR |

|

Rd |

Logical Shift RightЛогически сдвинуть вправо |

Rd(n)< |

Rd(n+1), |

|

|

|

|

|

|

||||||

|

|

|

|

|

Rd(7)< |

0, C< |

Rd(0) |

|

Z,C,N,V |

|

1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

ROL |

|

|

Rotate Left trough CarryСдвинуть влево через |

Rd(0)< |

C, |

|

|

|

|

|

|

|

|||||

|

|

|

перенос |

Rd(n+1)< |

Rd(n), |

|

|

|

|

|

|

||||||

|

|

|

|

|

C< |

Rd(7) |

|

|

|

|

Z,C,N,V,H |

1 |

|||||

ROR |

|

Rd |

Rotate Right trough CarryСдвинуть вправо |

Rd(7)< |

C, |

|

|

|

|

|

|

|

|||||

|

|

|

через перенос |

Rd(n)< |

Rd(n+1), |

|

|

|

|

|

|

||||||

|

|

|

|

|

C< |

Rd(0) |

|

|

|

|

Z,C,N,V |

|

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

ASR |

|

Rd |

Arithmetic Shift RightАрифметически |

Rd(n)< |

|

Rd(n+1), |

|

|

|

|

|

|

|||||

|

|

|

сдвинуть вправо |

n=0...6 |

|

|

|

|

|

|

Z,C,N,V |

|

1 |

||||

SWAP |

Rd |

Swap Nibbles - Поменять нибблы местами |

Rd(3...0)< >Rd(7...4) |

Íåò |

|

1 |

|||||||||||

BSET |

|

s |

Flag Set -Установить флаг |

SREG(s)< |

1 |

|

|

SREG(s) |

|

1 |

|||||||

BCLR |

|

s |

Flag Clear -Очистить флаг |

SREG(s)< |

0 |

|

|

SREG(s) |

|

1 |

|||||||

SBI |

|

P,b |

Set bit to I/O Register - Установить бит в регистр I/O |

I/O (P,b)< |

1 |

|

|

Íåò |

|

|

2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

171

ATMEL |

|

|

|

|

ÊÒÖ-ÌÊ |

|

|

|

|

|

|

|

|

CBI |

P,b |

Clear Bit in I/O Register - Очистить бит в |

|

|

|

|

|

|

регистреI/O |

I/O(P,b)< 0 |

Íåò |

2 |

|

BST |

Rd,b |

Bit Store from Register to T - Переписать бит из |

|

|

|

|

|

|

регистра во флаг T |

T< |

Rd(b) |

T |

1 |

BLD |

Rd,b |

Bit Load from T to Register -Загрузить T флаг в |

|

|

|

|

|

|

бит регистра |

Rd(b)< T |

Íåò |

1 |

|

SEC |

|

Set Carry FlagУстановить флаг переноса |

Ñ< |

1 |

C |

1 |

|

|

|

|

|

|

|

CLC |

|

Clear Carry Flag -Очистить флаг переноса |

C< |

0 |

C |

1 |

|

|

|

|

|

|

|

SEN |

|

Set Negative FlagУстановить флаг |

N< |

1 |

N |

1 |

|

|

отрицательного значения |

|

|

|

|

|

|

|

|

|

|

|

CLN |

|

Clear Negative Flag -Очистить флаг |

|

|

|

|

|

|

отрицательного значения |

N< |

0 |

N |

1 |

SEZ |

|

Set Zero FlagУстановить флаг нулевого |

|

|

|

|

|

|

значения |

Z< |

1 |

Z |

1 |

|

|

|

|

|

|

|

CLZ |

|

Clear Zero Flag - Очистить флаг нулевого |

|

|

|

|

|

|

значения |

Z< |

0 |

Z |

1 |

SEI |

|

Set Global Interrupt FlagУстановить флаг |

|

|

|

|

|

|

глобального прерывания |

I< |

1 |

I |

1 |

CLI |

|

Clear Global Interrupt Flag -Очистить флаг |

|

|

|

|

|

|

глобального прерывания |

I< |

0 |

I |

1 |

SES |

|

Set Signed FlagУстановить флаг знака |

S< |

1 |

S |

1 |

|

|

|

|

|

|

|

CLS |

|

Clear Signed Flag - Очистить флаг знака |

S< |

0 |

S |

1 |

SEV |

|

Set Overflow FlagУстановить флаг |

|

|

|

|

|

|

переполнения |

V< |

1 |

V |

1 |

CLV |

|

Clear Overflow Flag - Очистить флаг |

|

|

|

|

|

|

переполнения |

V< |

0 |

V |

1 |

|

|

|

|

|

|

|

SET |

|

Set T FlagУстановить флаг T |

T< |

1 |

T |

1 |

|

|

|

|

|

|

|

CLT |

|

Clear T Flag - Очистить флаг T |

T< |

0 |

T |

1 |

|

|

|

|

|

|

|

SEH |

|

Set Half Carry FlagУстановить флаг полу |

|

|

|

|

|

|

переноса |

H< |

1 |

H |

1 |

|

|

|

|

|

|

|

CLH |

|

Clear Half Carry Flag -Очистить флаг полу |

|

|

|

|

|

|

переноса |

H< |

0 |

H |

1 |

NOP |

|

No Operation - Выполнить холостую команду |

|

|

Íåò |

1 |

|

|

|

|

|

|

|

SLEEP |

|

Sleep - Установить режим SLEEP |

См. описание |

Íåò |

1 |

|

|

|

|

команды |

|

|

|

|

|

|

|

|

|

|

WDR |

|

Watchdog ResetСбросить сторожевой таймер |

См. описание |

Íåò |

1 |

|

|

|

|

команды |

|

|

|

|

|

|

|

|

|

|

172

ÊÒÖ-ÌÊ

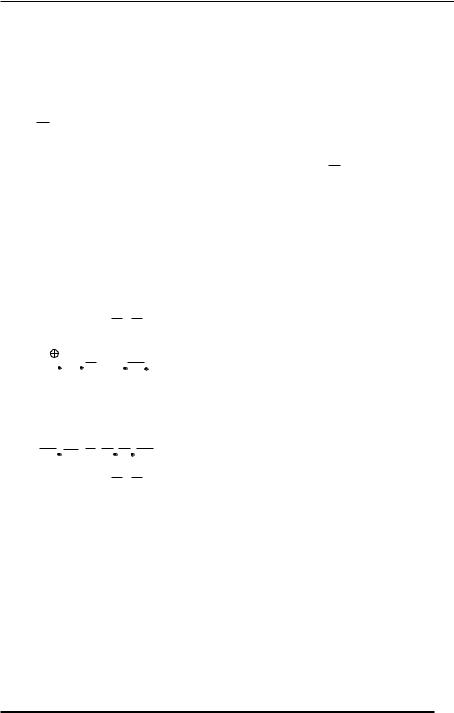

ADC - Add with Carry - Сложить с переносом

Описание:

Сложение двух регистров и содержимого флага переноса (С), размещение результата в регистре назначения Rd.

Операция:

(i) Rd < Rd + Rr + C

|

Синтаксис |

|

|

Операнды: |

|

|

|

|

Счетчик программ: |

|||||||||||

(i) |

ADC Rd,Rr |

|

|

0 |

< |

d |

< |

31, 0 |

< |

r |

< |

31 |

PC < |

PC + 1 |

||||||

|

|

|

|

|||||||||||||||||

|

|

|

||||||||||||||||||

16-разрядный код операции: |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0001 |

|

|

11rd |

|

|

|

|

|

dddd |

|

|

|

|

rrrr |

|

|

|

||

Булевы выражения регистра статуса (SREG) |

|

|

|

|||||||||||||||||

I |

T |

H |

S |

V |

|

|

|

N |

Z |

|

C |

|

|

|

||||||

- |

- |

<=> |

<=> |

|

<=> |

|

<=> |

|

<=> |

|

<=> |

|

|

|

||||||

H:Rd3 Rr3+Rr3+R3+R3

Rr3+Rr3+R3+R3 Rd3

Rd3

Устанавливается если есть перенос из бита 3, в ином случае о чищается

S: |

N V, Äëÿ ïðîâерок со знаком |

V: |

Rd7 Rr7 R7+Rd7 Rr7 R7 |

|

Устанавливается если в результате операции образуется п ереполнение |

|

дополнения до двух, в ином случае очищается |

N:R7

Устанавливается если в результате установлен MSB, в ином слу чае

очищается

Z:Rd7 Rr7 R7

R7 R7 R7 Rd7

R7 R7 Rd7

Устанавливается если результат $00, в ином случае очищается

C:Rd7 Rr7+Rr7+R7+R7

Rr7+Rr7+R7+R7 Rd7

Rd7

Устанавливается если есть перенос из MSB результата, в ином случае очищается

R: (Результат) соответствует Rd после выполнения команды

Пример:

|

; |

СложитьR1 : R0 с R3 : R2 |

add r2, r0 |

; |

Сложить младший байт |

adc r3, r1 |

; |

Сложить старший байт с переносом |

Ñëîâ: 1 (2 байта)

Циклов: 1

173

ATMEL |

ÊÒÖ-ÌÊ |

ADD - Add without Carry - Сложить без переноса

Описание:

Сложение двух регистров без добавления содержимого флаг а переноса (С), размещение результата в регистре назначения Rd.

Операция:

(i) Rd< Rd + Rr

|

Синтаксис |

|

|

|

Операнды: |

|

|

|

|

|

|

Счетчик программ: |

||||||||

(i) |

ADD Rd,Rr |

|

|

0 |

< |

d |

|

<31, 0 |

< |

r |

<31 |

PC< PC + 1 |

||||||||

|

|

|

|

|

|

|

||||||||||||||

16-разрядный код операции: |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0000 |

|

11rd |

|

|

|

|

|

dddd |

|

|

|

|

|

rrrr |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Булевы выражения регистра статуса (SREG) |

||||||||||||||||||||

I |

T |

H |

S |

V |

|

|

N |

|

Z |

C |

||||||||||

- |

- |

<=> |

|

<=> |

|

<=> |

|

<=> |

|

<=> |

|

|

<=> |

|

|

|||||

H:Rd3 Rr3+Rr3+R3+R3

Rr3+Rr3+R3+R3 Rd3

Rd3

Устанавливается если есть перенос из бита 3, в ином случае о чищается

S:N  V, Для проверок со знаком

V, Для проверок со знаком

V:Rd7 Rr7

Rr7 R7+Rd7

R7+Rd7 Rr7

Rr7 R7

R7

Устанавливается если в результате операции образуется п ереполнение

дополнения до двух, в ином случае очищается

N:R7 Устанавливается если в результате установлен MSB, в ином случае очищается

Z:R7 R6 R5

R5 R4

R4 R3

R3 R2 R1

R2 R1 R0

R0

Устанавливается если результат $00, в ином случае очищается

C:Rd7 Rr7+Rr7 R7+R7

Rr7+Rr7 R7+R7 Rd7

Rd7

Устанавливается если есть перенос из MSB результата, в ином случае очищается

R (Результат) соответствует Rd после выполнения команды Пример:

add r1,r2 |

; Сложить r2 с r1 (r1=r1+r2) |

adc r28,r28 |

; Сложить r28 с самим собой |

|

(r28=r28+r28) |

Ñëîâ: 1 (2 байта) Циклов: 1

174