- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 5. Оперативная память |

79 |

зисторов лежат явления, происходящие в полупроводниковом блоке, содержащем 3 области с чередующимися типами проводимости n и р, и, следовательно, с двумя р-n переходами, отстоящими друг от друга на расстояние, меньшее диффузионной длины неосновных носителей - электронов и «дырок». С использованием биполярной технологии разработана большая группа ЗЭ: на одноэмиттерных и многоэмиттерных транзисторах, на тиристорах, на инжекционных схемах.

В основе МДП-транзисторов, униполярных, лежит принцип управления проводимостью полупроводникового материала между двумя электродами при помощи электрического поля (полевые транзисторы). МДП-транзистор - активный прибор, в котором ток создается основными носителями под действием продольного электрического поля, а управление величиной тока осуществляется поперечным электрическим полем, приложенным к управляющему электроду. Существуют две разновидности МДП-транзисторов: с каналами п- и р- типов. Плотность упаковки достигает 106 бит на кристалл.

Схемотехнические признаки классификации:

-число транзисторов в ЗЭ (от 1 до 12-ти);

-количество и функции адресных и разрядных шин выборки (совмещенные или раздельные функции записи, считывания, подачи питающих напряжений);

-характер нагрузочных сопротивлений в триггере (линейная, нелинейная, переключаемая нагрузка);

-тип связи ЗЭ с разрядными шинами (непосредственная, через ключевые элементы). Системотехнических признаков три: принцип хранения, принцип считывания, форма

ивид считанного из ЗЭ сигнала. Принципы хранения: статический, динамических и квазистатический. Принципы считывания - с разрушением (ЗЭ на ферритовых сердечниках с прямоугольной петлей гистерезиса и ЗЭ на конденсаторах) и без разрушения информации. Формы считанного из ЗЭ сигнала - однополярный сигнал, двухполярный и парафазный. И, наконец, виды считанного сигнала - импульсный ток или импульсное напряжение.

5.2. Запоминающие элементы статических ОЗУ

Микросхемы памяти изготавливаются методами полупроводниковой технологии при использовании в качестве исходных материалов кремния, арсенида галлия, аморфных полупроводников или структур «кремний на сапфире». В настоящее время кремний остаётся основным материалом для изготовления микросхем памяти.

Особенности различных типов микросхем памяти определяются типом использованных в них запоминающих элементов, дешифраторов, формирователей сигналов записи-счи- тывания и буферных каскадов. В большинстве статических микросхем памяти эти схемы реализованы на базе биполярных элементов ТТЛ, ТТЛШ, ЭСЛ или на базе элементов комплементарных МОП и МДП структур.

|

+U пит |

|

|

|

+U пит |

R1 |

R2 |

|

|

R1 |

R2 |

|

|

|

ШР 0 |

|

ШР 1 |

ША |

|

|

ША Y |

|

|

VT1 |

VT2 |

ШР |

ША X |

VT1 |

VT2 |

ШР |

|

|

|

||

|

|

|

|

|

|

а) |

|

|

|

б) |

|

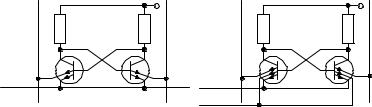

Рис. 5.2. Запоминающие элементы - триггеры - на биполярных транзисторах для статических ЗУ: а) с пословной выборкой, б) с поразрядной выборкой

Глава 5. Оперативная память |

80 |

VD1

VT1

VT1

Рис. 5.3. Схема включения транзистора и диода Шотки - интегральный транзистор Шотки

Наиболее распространенными являются ЗЭ в виде статического триггера на основе биполярных транзисторов. На рис. 5.2 показаны схемы ЗЭ для матриц, приведённых на рис. 5.11 - с пословной выборкой и с поразрядной выборкой.

С целью повышения быстродействия транзисторов применяется шун-тирование коллекторного перехода диодом Шотки (рис. 5.3).В этом диоде используется переход металлполупроводник, причём эта пара выбрана таким образом, чтобы работа выхода электронов из металла была больше, чем работа выхода электронов из полупроводника. По сравнению с обычным р-n переходом при прямом включении падение напряжения на переходе металлполупроводник на 30% меньше.

К числу микросхем памяти, ЗЭ которые выполнены по ТТЛ технологии относятся микросхемы серии КМ185РУ7 ёмкостью 256 слов по 4 разряда и серии КР185РУ9 - 64 слова по 9 разрядов. Время выборки адреса не более 45 нс. По ТТЛШ технологии выполнены ЗЭ микросхемы серии К589РУ01 ёмкостью 16х4 разрядных слов, время выборки не более 35 нс. Основные технические характеристики этих и других, рассматриваемых далее микросхем памяти, а также их достоинства и недостатки сведены в таблицу в Приложении.

Элементы с эмиттерно-связанной логикой (ЭСЛ) отличаются высоким быстродействием (tзп не более 1 нс), поэтому в настоящее время они являются основной элементной базой высокопроизводительных ЭВМ, быстродействующей измерительной аппаратуры и высокоскоростных систем цифровой связи. Различные варианты ЗЭ и логических элементов ЭСЛ технологии реализованы на основе простейшей логической схемы - переключателя тока (рис. 5.4). По ЭСЛ технологии изготовлены микросхемы памяти К1500РУ474 информационной ёмкостью 1024 4-разрядных слов, время выборки не более 15 нс, а также микросхемы КР1500РУ480A емкостью 16384 1-разрядных слов, время выборки не более 20 нс.

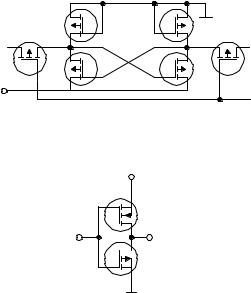

В последнее время получили широкое применение МДП транзисторы с каналом n- типа, характеризующиеся большой подвижностью носителей и меньшими размерами (рис. 5.5). По сравнению с биполярными транзисторами МДП-структура более технологична, так как для её изготовления требуется в 1,5 раза меньшее число операций. Кроме того, ввиду отсутствия в МДП-структуре специальных изолированных переходов, она занимает в несколько раз меньшую площадь. Основные параметры интегральных МДП транзисторов: ток стока до 10 мА, напряжение на стоке до 30 В, входное сопротивление 10 - 100 мОм, предельная частота - сотни МГц, порог напряжения - единицы вольт.

|

|

+U пит |

|

R1 |

R2 |

Вых. F0 |

|

Вых. F1 |

Вх. |

Вх. |

-Uоп |

|

||

VT1 |

VT2 |

VT3 |

|

|

R3 |

|

|

-Uпит |

Рис. 5.4. Схема переключателя тока ЭСЛ технологии

Глава 5. Оперативная память |

81 |

VT2 |

VT4 |

ШР 1 |

ШР 0 |

VT1 |

VT3 VT5 |

+U пит |

ША |

|

Рис. 5.5. Запоминающий элемент - триггер - на основе МОП структуры

+U пит

VT1

Вх.  Вых.

Вых.

VT2

Рис. 5.6. Инвертор на комплементарных МДП транзисторах

Комплементарный МДП транзистор (КМДП) представляет собой последовательное включение двух МДП транзисторов с каналами разного типа проводимости (рис. 5.6). Входом служат соединённые вместе затворы, выходом - истоки. Сопротивление между истоками очень велико, что обуславливает на 2-3 порядка меньшую, чем у ТТЛ, ЭСЛ, мощность потребления - в статическом режиме тысячные доли милливатт. КМДП транзисторы являются наиболее экономичными из широко используемых типов.

В случае применения в качестве диэлектрика в МДП транзисторах окисла кремния (слой SiO2) получают МОП-структуру, а в случае последовательного включения двух транзисторов с каналами разного типа проводимости - КМОП-структуру. На основе КМОП технологии созданы микросхемы памяти серии КР537 типов РУ4А, Б, РУ10, РУ11А, Б, РУ 13, РУ14, РУ17, параметры которых приведены также в таблице Приложения. Микросхемы типа КР573А, Б имеют информационную емкость 8Кх8-разрядних слов, время выборки не более 220 нс, потребляют мощность в режиме хранения не более 22 мВт, в режиме обращения - не более 470 мВт, напряжение источника питания 5 В ±10%.

Наряду с кремнием в качестве материала для изготовления быстродействующих интегральных микросхем в последнее время стал использоваться арсенид галлия (GaAs), что связано со следующими преимуществами: более высокая, в 5-6 раз, подвижность электронов, что и обуславливает увеличение быстродействия, а также на 2-4 порядка большее, чем у кремния, удельное сопротивление нелегированного арсенида галлия, позволяющее создавать полуизолированные подложки. Определённым ограничением в использовании арсенида галлия является высокая стоимость исходного материала, менее отработанные и более сложные технологические процессы и худшая, чем у кремния, теплопроводность.

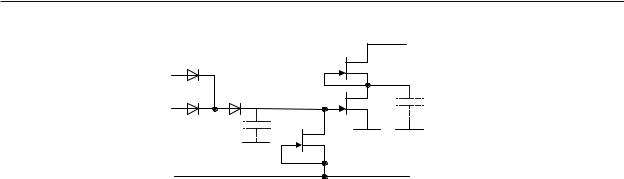

Основным активным элементом микросхем на основе арсенида галлия является транзистор с барьером Шотки - полевой транзистор. По сравнению с подобным транзистором, выполненным из кремния, транзистор на арсениде галлия обладает в 6 раз большей крутизной ВАХ и почти в 5 раз меньшей работой переключения. Границы частот транзистора лежат в пределах до 15 ГГц, время задержки - сотни пикосекунд. Наибольшее применение в сверхбыстродействующих БИС получили нормально открытые полевые транзисторы в инверторе и сборка диодов Шотки - диодно-полевая логика (ДПЛ), представленные на рис. 5.7. Микросхема памяти на базе арсенида галлия К6500РУ1 обладает информационной ёмкостью 1Кх1-разрядных слов, время выборки 4 нс, потребляемая мощность - менее 1,6 мВт.

Глава 5. Оперативная память |

|

82 |

|

|

Uпит1 |

VD1 |

VT2 |

|

VD2 VD3 |

VT3 |

Cн |

|

VT1 |

|

Cп |

|

|

|

|

|

|

|

Uпит2 |

Рис. 5.7. Схема инвертора ДПЛ технологии

Дальнейшим шагом по пути повышения плотности упаковки интегральных микросхем памяти явилось применение в качестве запоминающих элементов биполярных транзисторов с инжекционным питанием. Основой транзисторов с инжекционным питанием является эффект нарушения электрической нейтральности базы при непосредственном вводе в неё (инжекции) избыточных носителей заряда. В структуре транзистора имеется специальный электрод-инжектор (генератор тока), обеспечивающий постоянный ввод избыточных носителей в базу n-р-n транзистора.

Элементы с инжекционным питанием имеют ряд достоинств. По плотности размещения элементов они почти на порядок превосходят обычные транзисторные схемы, в первую очередь из-за отсутствия резисторов, занимающих большие площади на кристалле. В приборах с инжекционным питанием элементы соединены непосредственно. Один инжектор используется на 10-20 элементов. В элементах отсутствует изолирующий р-n переход. Всё это также сказывается на уменьшении размеров. По потребляемой мощности инжекционные элементы являются одними из самых экономичных (0,01-0,1 мВт). Время задержки сигнала в элементах невелико - 5-10 нс. Работа переключения (произведение времени задержи на потребляемую мощность) очень мала, порядка 1 пДж. Перечисленные свойства элементов с инжекционным питанием обуславливают их перспективность и широкое применение в БИС с повышенной степенью интеграции.

Начало 90-х годов характеризуется возрождением биполярной технологии. Это связано в первую очередь с большим быстродействием и масштабированием элементной базы. Последние достижения биполярной технологии и уменьшение литографических размеров наряду с новыми схемотехническими разработками позволили значительно снизить величину задержи переключения. Созданы высокопроизводительные CБИC на основе кремниевых комплементарных биполярных вертикальных р-n-р транзисторных структур. В них использован двухтактный выходной каскад на комплементарных биполярных транзисторах, который по потребляемой в статическом режиме мощности близок к КМОП-вентилю.

Однако вертикальным комплементарным транзисторным структурам присущи такие недостатки, как протяжённость во времени технологического цикла и значительные, в силу использования несовмещенных технологий, площади р-n переходов и транзисторных структур в целом.

5.3. Запоминающие элементы динамических ОЗУ

Запоминающие элементы динамических ОЗУ построены на базе МОП транзисторов. Здесь используется тот факт, что у МОП транзистора высокое входное сопротивление. Это позволило построить схемы ЗЭ, у которых входной ток близок к нулю. В основу положен принцип накопления и восстановления - регенерации - заряда на затворе МОП транзистора. Основой ЗЭ является паразитная ёмкость Сп, накапливающая заряд. Из-за постепенного

Глава 5. Оперативная память |

83 |

разряда Сп за счёт токов утечки необходимы схемы восстановления, регенерации заряда. Периодическое, а не постоянное поступление энергии в ЗЭ позволяет сократить потребляемую мощность и упростить схему, что снижает размер площади и увеличивает плотность компоновки на кристалле. На рис. 5.8 приведена схема ЗЭ динамического типа. В режиме записи VТ1 и VT3 совмещают функции возбуждения разрядных шин и нагрузки для транзисторов триггера VT2, VT4.

|

ША |

|

|

|

VT1 |

VT3 |

|

|

VT2 |

VT4 |

|

ШР 0 |

Cп1 |

Cп2 |

ШР 1 |

Рис. 5.8. Динамические ЗЭ на МОП транзисторе

Врежиме записи подаются положительный импульс в адресную шину ША и отрицательный в разрядную шину ШР1 либо ШР2 в зависимости от того, записывается логический 0 или логическая единица. При этом VT1 или VT3 открывается, информация заносится

втриггер. Информация хранится в виде зарядов паразитных емкостей Сп1 и Сп2, причём «0» хранится неограниченное время, а «1» из-за токов утечки должна периодически восстанавливаться. Для регенерации информации периодически возбуждается шина ША, и одновременно на разрядные шины подается одинаковое по знаку напряжение низкого уровня в случае р-канальных транзисторов. В этом состоит одна из отличительных особенностей динамических ОЗУ.

Врежиме считывания возбуждают ША, как бы подключая источник питания к триггеру, и ток считывания через VT1 или VT3 поступает в соответствующую ШР - в ШР0, если хранился «0», или в ШР1, если хранилась «1».

Технологически проще выполняются ЗЭ на МОП транзисторах с диодами Шотки, схема которого приведена на рис. 5.9. Для регенерации информации периодически в адресную шину подаются импульсы с частотой порядка 1кГц. Потребляемая мощность в режиме хранения гораздо ниже, чем у статических ЗЭ на МОП транзисторах. Время выборки - менее 10 нс.

VD1 |

VD2 |

VT1 |

VT2 |

Cп1 Cп2 |

ШР 1 |

ША |

|

Рис. 5.9. Запоминающий элемент на МОП транзисторах и диодах Шотки

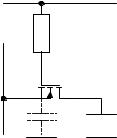

Дальнейшее совершенствование динамических ЗЭ привело к созданию ЗЭ на одном транзисторе. В его схеме присутствует конденсатор С ёмкостью порядка 400 пФ. Площадь такого ЗЭ вдвое меньше, чем площадь ЗЭ на трёх транзисторах для статических ЗУ. Cxeмa статического элемента приведена на рис. 5.10. При записи «1» транзистор открывается, и конденсатор С заряжается до потенциала шины ШР. При записи «0» ток через транзистор не протекает и конденсатор не заряжается.

Глава 5. Оперативная память |

84 |

ША

R

ШР

Cп  C

C

Рис. 5.10. Запоминающий элемент на одном МОП транзисторе

Врежиме считывания подают импульс низкого уровня в адресную шину ША, тогда на ШР заряд изменяется или нет в зависимости от того, записан «0» или «1»; заряд с С поступает в ШР.

Динамические ЗЭ по сравнению со статическими обладают рядом преимуществ: меньшее число транзисторов, вплоть до одного, обуславливает большую плотность размещения, меньшую потребляемую мощность, дешевизну изготовления и более высокое быстродействие. На одном кристалле можно разместить до 16 К запоминающих элементов. Так, микросхема типа К565РУ3А на основе n-МОП структуры обладает информационной ёмкостью 16Кх1р, время выборки менее 200 нс, потребляемая мощность - 0,04 мВт/бит. Недостатком динамических ЗЭ на МОП транзисторах является необходимость регенерации информации.

Как статическим, так и динамическим ЗЭ на МОП транзисторах присущ общий недостаток, а именно: потеря информации при аварийном выключении питания. Этот недостаток устраняется путём автоматического перехода на аварийное питание от аккумуляторов.

С целью исключения зависимости хранения от аварийного отключения созданы полупроводниковые ЗЭ с гистерезисными, как у магнитных материалов, свойствами. Для этого

кроме слоя окиси кремния SiO2 под затвор вводится слой нитрида кремния Si3N4 или слой алунда Al2O3, и получаются, таким образом, МОП транзисторы с двухслойной изоляцией, называемые МНОП и МАОП соответственно. Сопротивление слоя нитрида значительно выше, чем сопротивление слоя оксида кремния. Принцип работы МНОП транзистора связан с накоплением заряда на границе между двумя слоями диэлектрика и влиянием этого заряда на величину порога напряжения срабатывания транзистора. При подаче логического 0 на затвор МНОП транзистора с индуцированным каналом р подаётся импульс положительной полярности порядка 30-50 В. Это вызывает туннелирование электронов из подложки под затвор. Из-за очень высокого сопротивления слоя нитрида кремния электроны будут накапливаться на границе раздела между диэлектрическими слоями. Накопление заряда приведёт к установлению низкого (1.5- 4В) порогового напряжения. Благодаря хорошим диэлектрическим свойствам слоев накопленный заряд может оставаться неизменным в течении нескольких тысяч часов при отсутствии питания, а в некоторых специальных разработках в течении нескольких лет.

При записи логической 1 подаётся импульс отрицательной полярности порядка -30 В, вызывая переход электронов в диэлектрическую подложку. При этом на границе между слоями диэлектрика образуется положительный заряд, что сопровождается увеличением порогового напряжения до - 20В.

Врежиме считывания на затвор подаётся напряжение, достаточное для перевода транзистора в проводящее состояние, если был записан «0», и недостаточное, если «1». Таким образом, МНОП транзисторы имеют два установившихся состояния с различным пороговым напряжением и используются как запоминающие элементы, длительно сохраняющие информацию при снятии напряжения питания. Параметры динамических БИС ЗУ приведены в Приложении.