- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 3. Системы команд микроЭВМ |

59 |

Входные параметры: регистр С - длина чисел (байт); регистры Н, L - адрес младшего байта вычитаемого; регистры D, Е - адрес младшего байта уменьшаемого. Каждое из чисел описывается в последовательных адресах памяти, начиная с младших байтов. Результат заносится в память, отведенную под вычитаемое. В этом случае, если уменьшаемое меньше вычитаемого, будет вызвана подпрограмма ВРР формирования звукового сигнала.

Контрольные вопросы к главе 3

1. Для описания функционирования какого уровня ЭВС предназначен язык микроопераций (ЯМ)?

2.Назовите средства описания на ЯМ регистра, шины, массива памяти.

3.Назовите средства описания на ЯМ приращения содержимого счетчика, сдвига, составления слова.

4.Как на ЯМ описать двухместную микрооперацию?

5.Как на ЯМ записываются условные микрооператоры?

6.Как составить и записать на ЯМ программу?

7.Как на ЯМ записать программу функционирования в режиме записи памяти с произвольным обращением?

8.То же в режиме считывания с разрушением?

9.Как взаимосвязаны язык Ассемблера и мнемокод?

10. На какие группы делится система (набор) команд МПС и микроЭВМ?

11. Какие языки высокого уровня используются для программирования микроЭВМ?

12. Чем отличаются правила записи ассемблерных программ для ручной и для автоматической трансляции? 13. Каким образом команды программ, написанные на языке высокого уровня и на языке Ассемблера переводятся в машинный код?

14. Что понимается под форматом команд? Переменным форматом команд и данных? Упрощенным форматом?

15. Для чего используются признаки (флаги)?

16. В какой форме записывается программа в мнемокодах? 17. В какой форме записывается программа в машинном коде?

18. Какие команды используются для вызова подпрограммы и для возврата в основную? 19. В чем заключается процедура выполнения программы по шагам?

20. Как осуществляется начальный вход в микропрограмму?

21. Как заставить микропроцессор выполнять функцию таймера, т.е. получать от него сигнал через заданный отрезок времени после поступления определенного входного сигнала?

22.Охарактеризуйте на память пять каких-либо выполняемых микроЭВМ команд.

23.В чем заключается назначение команд пересылки данных?

24.Почему команды пересылки данных можно назвать командами “копирования” данных?

25.Какую текущую команду отрабатывает МП, ответвляясь в подпрограмму?

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

60 |

Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

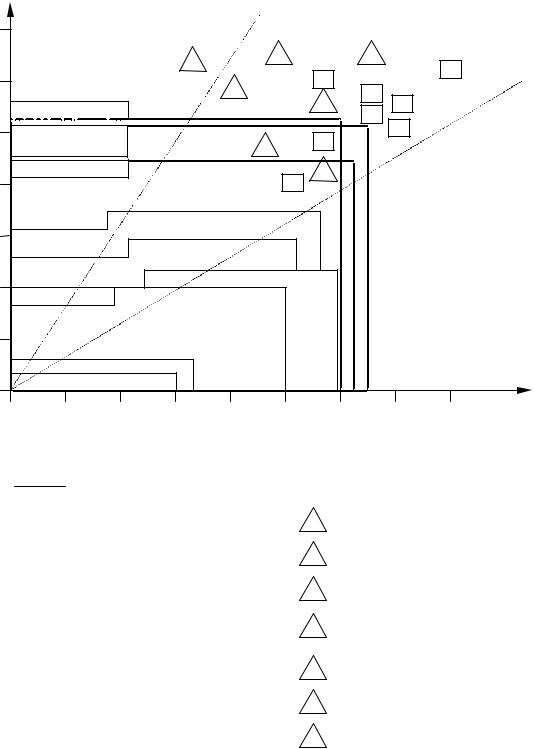

В последнее время быстро развивающиеся технологические возможности привели к созданию мощных однокристальных микропроцессоров, таких, как Альфа, Power PC, Pentium, Intel 860 и др. Многие сложные вычислительные задачи удаётся решать на современных PС и рабочих станциях, объединённых в единую локальную сеть. Однако требования, предъявляемые к ЭВМ при необходимости решения проблемных задач первостепенной важности со временем повышаются, а возможности ЭВМ традиционной фон-Неймановской архитектуры ограничены теоретическим и техническими пределами скорости выполнения операций. На рис. 4.1 в координатах производительность - память даны требования к ЭВМ для различных задач. Производительность рассчитана исходя из требования 15-минутного решения задачи, указаны типы современных ЭВМ, включая супер-ЭВМ, которые перекрывают эти требования.

Из приведенной на рис. 4.1 информации можно сделать вывод, что супер-ЭВМ в настоящеевремя неудовлетворяютпредъявляемымк ним требованиямпo производительности иобъему памяти на несколько порядков. Принципиальные причины, не позволяющие построить ЭВМ требуемой производительности, заключаются в следующем. Ограничения накладываются возможностями отвода тепла от микросхем. Жидкостное охлаждение позволяет отвести 20 Вт с одного квадратного сантиметра. Следовательно, чем меньше выделяет энергии схема на одно логическое срабатывание А э , тем меньше выделяется мощности

Рэ=Аэ/tэ

при том же быстродействии, где tэ - время срабатывания элемента. Следовательно, в одном и том же объеме можно сосредоточить большее количество логических элементов и элементов памяти. Если объем растет, растут потери во времени на связи между элементами tсв, и времена tэ становятся соизмеримы, а иногда много меньше, чем tсв. Поэтому, чем выше производительность элемента, тем меньший объем должна иметь вычислительная система.

Немалую роль при создании ЭВМ играет показатель надёжности элемента λ . В зарубежных разработках этот параметр не ограничивает производительности, так как даже для схем большой интеграции величина λ не превышает 10-8. Отечественная элементная база, в особенности на первом этапе производства, имеет λ >10-6, это заставляет вводить резервирование и аппаратный контроль во все устройства машины, что увеличивает объём устройств и потребляемую мощность. Предельная производительность одного процессора, работающего по фон-Неймановскому принципу, вряд ли превзойдёт 108 оп/с на скалярных операциях. В конечном счёте требования к развитию вычислительных средств сводятся к увеличению производительности при уменьшении потребляемой мощности и повышению ожидаемой надёжности функционирования.

Традиционная модель вычислителя сформулирована в работах Тьюринга, Клини, Колмогорова, Глушкова и наиболее полно представлена в работах фон-Неймана в 1969 году. Фон-Неймановская архитектура имеет 4 характеристики (рис. 4.2)

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

61 |

1. Наличие единого вычислительного устройства, включающего процессор, средства передачи информации и память.

2. Линейная структура адресации памяти, состоящей из слов фиксированной длины.

|

Производительность, |

|

|

|

|

|

|

|

1014 |

F lops |

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

3 |

6 |

|

|

|

|

|

|

|

||

1013 |

|

|

|

|

|

4 |

|

|

|

|

|

4 |

|

2 |

|

||

|

|

|

|

|

5 |

|

||

|

NCube-3 (65 т. Пр.) |

|

|

|

3 |

|

||

|

|

|

|

|

1 |

|

||

1012 |

CM 5 (16 т. Пр.) |

|

|

|

|

7 |

5 |

|

|

|

|

6 |

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

1011 |

Cray T3D (2 т. Пр.) |

|

|

8 |

7 |

|

|

|

|

|

|

|

|

|

|

||

|

CM 5 (1 т. Пр.) |

|

|

|

|

|

|

|

1010 |

Cray T3D (128 Пр.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

109 |

NCube-2S (1 т. Пр.) |

|

|

|

|

|

|

|

Cray Y-MP/8 128 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

108 |

|

|

|

|

|

|

|

Емкость памя- |

|

МВК Э-2-10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ти |

|

107 |

SPAR C-10/36 |

|

|

|

|

|

|

|

104 |

105 |

106 |

107 |

108 |

109 |

1010 |

1011 |

64 р. слов |

1012 |

||||||||

Теоретически возможная пиковая производительность при максимальной комплектации Реально достигнутая производительность на тестовых задачах

Теоретически возможная пиковая производительность при максимальной комплектации Реально достигнутая производительность на тестовых задачах

1 |

Аэродинамика - летательные аппараты |

1 |

Наука о земле |

|

|

Моделирование технологий конструиро- |

|

|

|

2 |

2 |

Сложные объекты |

||

|

вания космических кораблей и станций |

|||

|

|

|

||

|

Трехмерные сближения, столкновения и |

3 |

Модель климата атмосферы, океа- |

|

3 |

||||

|

проникновения динамических объектов |

|

на |

|

|

Сложные объемные структуры - нелиней- |

4 |

Строение вещества, элементарных |

|

4 |

частиц и их взаимодействие |

|||

|

ные мультитела |

5 |

Экономический анализ деятельно- |

|

|

Лазерная оптика - трехмерные связанные |

|||

5 |

сти человека |

|||

|

резонаторы |

6 |

Структурная биология |

|

|

Трехмерная магнитогидродинамика |

|||

6 |

||||

|

|

|||

|

Проблемы визуализации и распознавание объ- |

7 |

Синтез в фармакологии |

|

7 |

||||

|

ектов |

|

|

|

8 |

Трехмерные модели атмосферы |

|

|

Рис. 4.1. Требования к ЭВМ при решении различных задач

3.Низкий уровень машинного языка, команды которого осуществляют операции над элементарными операндами.

4.Централизованное последовательное управление.

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

62 |

Процессор

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Память |

Устройства |

|||||

|

Вв - Выв |

|||||

|

|

|

|

|||

Рис. 4.2. Традиционная структура ЭВМ

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Системн. |

|

Общая |

|

|

Процессоры |

|

|

|||||||

|

|

|

|

|||||||||||

Вв - Выв |

|

память |

|

с локальными |

|

|

||||||||

|

|

|

|

|

|

|

|

|

памятью и |

|

|

|||

|

|

|

|

|

|

|

|

|

|

УВв - Выв |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.3. Многопроцессорная архитектура с общей шиной

Один из способов повышения скорости передачи и обработки информации - увеличение числа битов, передаваемых по шине параллельно, почему разрядность МП увеличилась с 8 до 16, затем до 32 бит, а в больших ЭВМ - до 64 разрядов.

4.2. Распараллеливание процессов обработки информации

Первый путь повышения производительности вычислительных средств увеличением быстродействия элементной базы практически исчерпал все возможности, натолкнувшись на теоретический предел 109 - 1016 оп/с. Дальнейнее продвижение в этом направлении требует открытия новых физических принципов обработки информации.

Второй путь, в основе которого лежит распараллеливание процессов обработки информации на всех уровнях решения задачи, шроко использовался на всех этапах развития вычислительных средств (рис. 4.3):

-переход от последовательного счета к параллельному,

-параллельная работа основных устройств ЭВМ,

-введение пакетного режима работы и режима разделения времени,

-мультиплексный режим обработки данных,

-конвейерный режим,

-многопроцессорные и многомашинные комплексы,

-режим управления потоками данных и другие.

Второй путь не исчерпал себя и о успехом будет развиваться в перспективных ЭВМ, особенно в супер-ЭВМ.

4.3. Принцип совмещения операций. Конвейерная обработка информации

Элементной базой ЭВМ многопроцессорной конфигурации с успехом могут служить наборы многокристальных секционных микропроцессоров (рис. 2.8, в). Автономность работы и большое быстродействие БИС управляющего процессора позволяют выбирать команды из памяти с большей скоростью, чем скорость их исполнения БИС операционного процессора. При этом в управляющем процессоре образуется очередь ещё не исполненных команд. Напомним, что очередь - последовательный список, в котором все дополнения вносятся в один конец, а доступ для выборки осуществляется к другому концу списка (FIFO).

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

63 |

Одновременно либо заранее подготавливаются те данные, которые потребуются операционному процессору в следующих циклах работы. Это так называемая опережающая выборка команд, которая экономит время процессора на ожидание операндов, необходимых для выполнения команд программы. В этом случае проводится совмещение операций выборки команд и подготовки операндов.

В многокристальном секционном микропроцессоре выбираемые из памяти команды распознаются и выполняются каждой частью МП автономно, поэтому может быть обеспечен режим одновременной работы всех БИС МП, то есть конвейерный поточный режим исполнения последовательности команд программы с небол ьшим временным сдвигом.

При конвейерной обработке последовательность выполнения команды разбивается на этапы, которые могут выполняться одновременно.

Для выполнения операций каждого типа служат специализированные блоки. Во время выполнения предыдущей команды производится опережающая выборка из памяти очередной команды.

Пример 4.1. Разбить на этапы команду “Умножение двух десятичных чисел Процессор выполняет три операции:

а) перемножает мантиссы |

(3,8• 9,6 = 36,48), |

б) складывает порядки (2+3=5), |

|

в) нормализует результат, то есть размещает в необходимом месте запятую (точку) 3,648• 106. |

|

Эти три операции (этапа) реализуются тремя отдельными исполнительными блоками; во время выполнения операции в) блоки а) и б) не заняты никакими действиями. При применении конвейера эти исполнительные блоки могли бы обрабатывать очередную пару чисел одновременно с выполнением операции в) над данной парой.

Рассмотрим теперь функционирование конвейера МП Z8000 фирмы Zilog, 16-разрядного, степень интеграции - 20.000 транзисторов на кристалле. Цикл выполнения команды состоит из 6-ти этапов:

а) выборка команды, б) декодирование команды,

в) вычисление адреса операнда, г) выборка операнда,

д) собственно выполнение команды, е) запоминание результата.

Когда в конвейере заканчивается выполнение определённого этапа предыдущей команды, высвобождается соответствующий исполнительный блок, и может быть начато выполнение аналогичного этапа следующей команды. В идеале очередная команда поступает на конвейер в тот момент, когда предыдущая команда с него сходит, что определяет шестикратное повышение производительности.

В случае, если команды не выполняются одна за другой, или не в каждой команде используются все исполнительные блоки конвейера, а также если этапы имеют различную длительность, оптимальное повышение производительности не достигается. На рис. 4.4 представлено во времени конвейерное выполнение последовательности трёх команд. Видны потери производительности вследствие того, что отдельные команды используют не все блоки конвейера.

Команда INC R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

а |

б |

|

в |

|

г |

|

д |

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Простой |

|

|

|

Ожид. |

|

|

|

|

|

|

|

|

|

||||

Команда MOVE R3,@R2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

а |

|

б |

|

|

|

|

|

в |

|

г |

|

д |

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Ожид. |

|

|

|

|

|

|

Простой |

|

|

|

|||||

Команда DIV R4, R3 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

а |

|

б |

|

в |

|

г |

|

д |

|

д |

|

д |

|

е |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ТЦ |

|

|

|

|

|

|

Простой |

Ожид. |

|

|

|

|

|

|

t |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

2 |

3 |

4 |

5 |

6 |

|

7 |

8 |

9 |

10 |

|

|||||||||

Рис. 4.4. Конвейерное выполнение последовательности команд