- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 2. Структура и функционирование процессора |

17 |

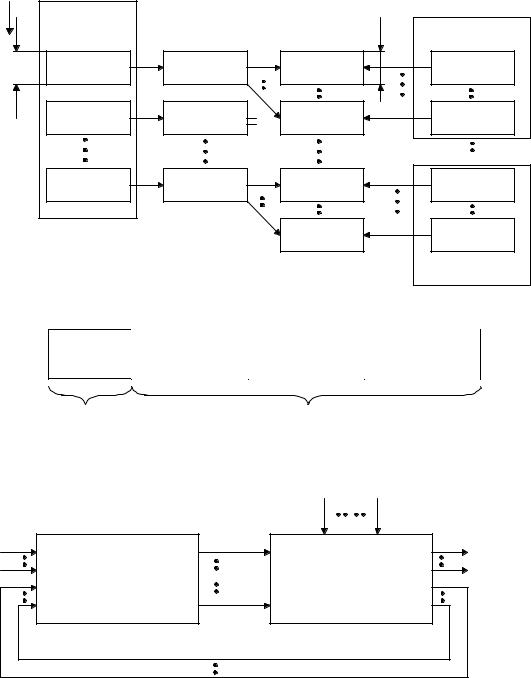

Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

2.1. Рабочий цикл процессора. Микропрограммная интерпретация команд центрального процессора

Один из многих параметров, характеризующих ВС, рабочий цикл процессора иначе называется циклом центрального процессора либо машинным циклом. Это время, требуемое для выборки из памяти и выполнения одной простой машинной команды, например, сложения и вычитания. На рис. 2.1, а он обозначен ТЦ. По команде программы в АЛУ центрального процессора выполняются арифметические и логические действия над операндами-операции (рис. 1.1). Выполнение операции производится по частям, называемым микрооперациями - элементарным операциям, выполняемым за один машинный такт ТТ. Таким образом, каждой микрооперации соответствует выполняемое в АЛУ элементарное действие передачи информации между регистрами общего назначения РОН или ее преобразования. Это действие инициируется (вызывается) поступлением управляющего сигнала V на внутреннюю управляющую шину. Для реализации команды необходимо на соответствующие линии ШУ подать распределенную во времени последовательность управляющих сигналов Vi, Vi+1, Vi+2,... Их вырабатывает управляющий блок УУ.

Последовательность микрокоманд, необходимых для выполнения операции, называется микропрограммой. Микропрограммная интерпретация микрокоманд иллюстрируется примером (рис. 2.1, б, в).

Пример 2.1. Выполнение команды операции сложения. К управляющим шинам АЛУ необходимо подвести следующую последовательность управляющих сигналов:

Номера тактов ТТ |

Микрооперации и названия управляющих сигналов |

1 |

Прием Рг 1 |

2 |

Прием Рг 2 |

3 |

Прием Рг Сумм или Прием Рг Сумм+ 1 Смещ |

4 |

Прием Рг Аккумулятор |

5 |

Прием ШД вых. |

Таким образом, УУ вырабатывает управляющие сигналы для осуществления выборки кода очередной команды из памяти, дешифрации кода команды, нормирования адресов операндов, выборки операндов из памяти, передачи их в АЛУ, выполнения в АЛУ операции, предусмотренной кодом команды, передачи результата в память. Последовательности управляющих сигналов V вызывают выполнение в процессоре микроопераций. В процессорах малых и средних ЭВМ часто применяют микропрограммное УУ. В больших же машинах применяется управление с «жесткой» логикой, то есть аппаратно реализованной, что приводит к повышению быстродействия ЭВМ. В МП наборах разных типов применяются оба способа выработки управляющих сигналов (см.разд. 2.5) .

УУ можно рассматривать как конечный автомат (рис. 2.1, в), определяемый:

1. Множеством входных сигналов (u1, u2,...,un), соответствующих задаваемому УУ извне двоичному коду операции (КОП) и двоичным значениям осведомительных сигналов.

Глава 2. Структура и функционирование процессора |

18 |

2.Множеством двоичных выходных сигналов (V1, V2,...Vm), соответствующих множеству микроопераций операционного блока - АЛУ. При Vi =1 возбуждается i-я микрооперация.

3.Множеством подлежащих реализации микропрограмм, устанавливающих в

зависимости от значении входных сигналов ui управляющие сигналы, выдаваемые устройством управления в определенные такты.

|

ОЗУ |

|

|

|

|

t |

Программа |

|

|

T Т |

Микро- |

(задача) |

|

|

|||

|

|

1 |

|

V 1 |

программа 1 |

T Ц |

|

Микро- |

Микро- |

||

Команда 1 |

Операция |

операция |

|

команда |

|

|

|

5 |

Микро- |

V 5 |

Микро- |

|

Команда 2 |

Операция |

|||

|

операция |

|

команда |

||

|

|

|

|

||

|

Команда N |

Операция |

Микро- |

|

Микро- |

|

операция |

|

команда |

||

|

|

|

|

||

|

|

|

Микро- |

V m |

Микро- |

|

|

а) |

операция |

|

команда |

|

|

|

|

Микро- |

|

|

|

|

|

|

программа N |

Сложить |

Рг 1 |

Рг 2 |

Рг Сумм |

Код |

Адрес |

Адрес |

Адрес |

операции |

1-го операнда |

2-го операнда |

результата |

Операционная |

|

Адресная |

|

часть |

б) |

часть |

|

Код команды |

|

Управляющие |

Вход |

Операнды |

||

|

сигналы |

|

|

|

||

Вход |

УУ - |

V 1 |

|

|

Выход |

|

|

Операционный |

Результат |

||||

u1 |

управляющий |

обработки |

||||

блок - автомат |

||||||

|

автомат |

V n |

|

|||

un |

|

Осведомительные |

|

|

|

|

|

|

сигналы |

|

|

|

|

в)

Рис. 2.1. Микропрограммная интерпретация команд и микрокоманд: а - распределение во времени выполнения команд и микрокоманд, б - структура трехадресной команды, в - процессор как два конечных автомата

По множествам входных и выходных сигналов и микропрограмм определяется множество внутренних состояний УУ (Q0, Q1, Q2,...Qr), мощность которого (объем памяти

Глава 2. Структура и функционирование процессора |

19 |

управляющего устройства) в процессе проектирования стараются минимизировать. Управляющий автомат может быть задан, как автомат Мура

Q(t+1)=A[Q(t), u1(t), u2(t),...,un(t)]; V1(t)=B1[Q(t)];

........................

Vm(t)=Bm[Q(t)];

или как автомат Мили (автомат с памятью) Q(t+1)=A[Q(t), u1(t), u2(t),...,un(t)]; V1(t)=B1[Q(t), u1(t), u2(t),...,un(t)];

........................

Vm(t)=Bm[Q(t), u1(t), u2(t),...,un(t)],

где функции переходов и выходов А, В определяются выданной из памяти микропрограммой. Автомат неходится в состоянии Q(t) в течение времени ТTi, а в состоянии Q(t+1) - в

следующем такте ТTi+ 1.

Операционный блок - АЛУ - является также конечным автоматом. Взаимодействие двух конечных автоматов, УУ и АЛУ показано на укрупненной схеме процессора на рис. 2.1, в. Все сигналы будут подробно рассмотрены в разд.2.2 и 2.3. Процессор строится на 2- х разнотипных автоматах, Мура и Мили.

2.2. Устройство управления с программируемой логикой

Микропрограммные УУ, называемые в технической литературе и как УУ с программируемой логикой, с хранимой в памяти логикой, появились позже, чем УУ с «жесткой» логикой. Но, поскольку микропрограммное УУ обладает наглядностью, облегчающей изучение процесса функционирования ЭВМ, рассмотрим его в первую очередь.

Схему микропрограммного управления предложил в 1851 г. Уилкс. Она изображена на рис. 2.2. Управляющие сигналы Vi , соответствующие каждый своей микрооперации, по одному или по нескольку будут поступать в собственно операционный блок (АЛУ, ПЗУ, ОЗУ) с управляющей матрицы С. Матрица С, управляющая, и матрица S - память микропрограмм, представляют собой ПЗУ. В простейшем случае ПЗУ реализуется как горизонтальные и вертикальные шины, связанные между собой в нужных точках через диоды или перемычки, прожигаемые при программировании в процессе изготовления микропроцессорной БИС. Чтобы не загромождать рисунок, элементы связи между горизонтальными и вертикальными шинами ПЗУ - диоды или перемычки - показаны условно в виде жирных точек. Вертикальные выходные шины матрицы С являются линиями управляющей, шины операционного блока. Каждая линия соответствует одному из управляющих сигналов микроопераций V1, V2,..., Vi,..., Vm. Появление сигналов на шине инициирует выполнение соответствующей микрооперации в АЛУ.

Вертикальные шины матрицы S устанавливают определенный код в регистре номера (адреса) микрокоманды РгНМК. В момент поступления синхросигнала дешифратор Дш в соответствии с l-разрядным кодом на РгНМК возбуждает одну из 2l горизонтальных шин (на рис. 2.2 - это шина номер 3, она показана жирной чертой) . Когда горизонтальная шина возбуждена, она, в свою очередь, возбуждает отмеченную точкой (или отмеченные точками) вертикальную (вертикальные) шину управления матрицы С, задавая, таким образом, последовательность управляющих сигналов, соответствующих набору микроопераций, выполняемых в данном машинном такте ТТj. Одновременно эта горизонтальная шина возбуждает соответствующие вертикальные шины матрицы S, устанавливая в РгНМК номер горизонтальной шины и тем самым номер микрокоманды, которая должна выполняться в следующем такте Т . Таким образом, задаётся набор микроопераций, то есть микропрограмм, выполняемых в данном цикле. Задержка введена для устранения «гонок»

Глава 2. Структура и функционирование процессора |

20 |

сигналов. Ветвление в микропрограмме, то есть условный переход по некоторому условию, реализуется триггером условия, принимающим состояние и выдающим сигнал, зависящий от результата проверки в АЛУ условия (значения входного осведомительного сигнала или логической функции входных сигналов), заданного в предыдущем (одном из предыдущих) такте. В зависимости от того, выполняется или не выполняется проверяемое условие, триггер Тг возбуждает одно из ответвлений горизонтальной шины в матрице S, тем самым задавая тот или иной номер следующей микрокоманды.

НМК |

|

Дш |

Рг |

|

|

Код номера микрокоманды |

Пуск |

Синхросигналы |

|

|

микропрограммы

Задержка |

l-разрядный код |

|

В операционный блок |

|

|

номера следующей |

Шина управления |

|

|

микрооперации |

V 1 V 2 ............................ |

V m |

r1 r2 |

....................rl |

Матрица С - |

|

Матрица S - |

Тг |

управляющая |

ПЗУ память микропрограмм |

|

|

|

Память |

От триггера |

|

микрокоманд |

условия осведомительный |

||

|

|

сигнал uj |

|

Структура микрокоманды

V 1 V 2 |

Код микрооперации |

V m |

Номер (адрес) |

след. микрокоманды |

|||

|

Операционная часть |

|

Адресная часть |

Рис. 2.2. Схема микропрограммного управления

Матрицы С и S могут быть реализованы в виде памяти микропрограмм (микрокоманд) - ПМК, в которой отдельные слова соответствуют микрокомандам, иначе говоря, горизонтальным шинам на рис. 2.2, а точки на этих шинах - значениям «логическая 1» в соответствующих разряда r этих слов. Для хранения микропрограмм естественно использовать постоянные памяти (память только для считывания), так как после разработки и проверки микропрограммы практически не изменяются. Кроме того, ПЗУ обладают большим быстродействием, чем ЗУ с произвольным обращением, что весьма существенно для ПМК, так как в процессе выполнения команды выполняемой программы задачи производится много обращений к ПМК за очередными микрокомандами.

При проектировании устройств управления метод микропрограммирования упрощает разработку самой МПС, изготовление, наладку и эксплуатацию, а также снижает стоимость аппаратуры. Ценность микропрограммирования в УУ с программируемой логикой управления (с «гибкой» логикой) состоит и в том, что каждый пользователь может сконструировать себе из микропрограмм тот набор команд, который наиболее годен для его конкретной задачи. Переход от одного набора команд к другому достигается путем простой замены информации в ЗУ без каких-либо переделок в аппаратуре. Это достигается