- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 5. Оперативная память |

|

|

|

91 |

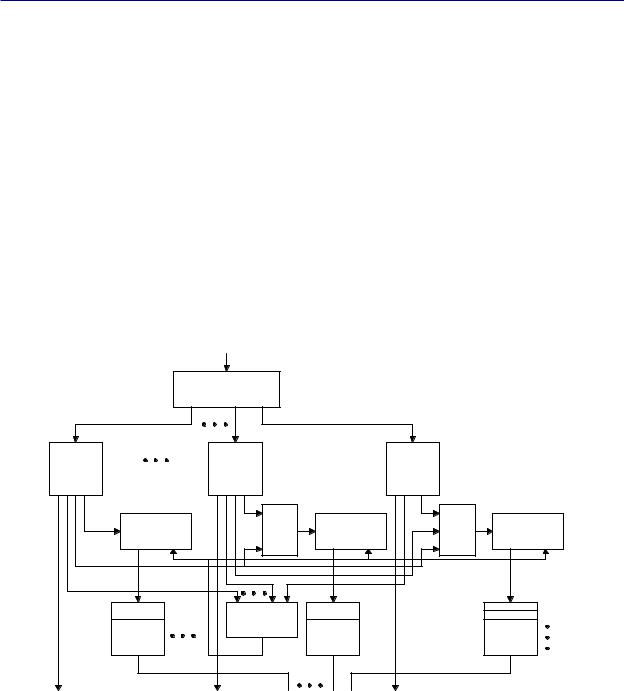

В модульном ОЗУ с опережающей выборкой (рис. 5.18) ячейки памяти разнесены по |

||||

разным модулям. Здесь применена сквозная адресация: «нулевой» адрес расположен в нуле- |

||||

вом 3М, первый- в первом ЗМ и так далее. При обращении по какому-либо адресу автомати- |

||||

чески подготавливается обращение по нескольким следующих адресам. Обращения к моду- |

||||

лям можно совместить по времени, если обращение к ОЗУ происходит без нарушения пос- |

||||

ледовательности адресов. Такую организацию ОЗУ целесообразно применять в ЭВМ с рас- |

||||

параллеливанием операций. |

|

|

|

|

5.6. Структура построения БИС динамических ОЗУ |

|

|

||

Для динамических запоминающих микросхем структурные схемы подобны вышерас- |

||||

смотренным и дополнены схемой регенерации. С этой целью введены усилители восста- |

||||

новления, число которых равно числу разрядов кода слова. Усилители подсоединены к ин- |

||||

формационным входам матрицы. Микросхемы динамических ОЗУ отличаются от микро- |

||||

схем статических ОЗУ большей информационной ёмкостью, что обусловлено меньшим ко- |

||||

личеством компонентов в одном ЗЭ и, следовательно, более плотным их размещением в |

||||

полупроводниковом кристалле. |

|

|

|

|

|

ША |

|

|

|

|

ДШ ЗМ |

|

|

|

БМУ |

БМУ |

|

БМУ |

|

ЗМN |

ЗМ1 |

+1 |

ЗМ0 |

+1 |

+1 |

|

|

||

|

1 |

|

1 |

|

|

|

|

||

СчА ЗМ N |

|

СчА ЗМ 1 |

|

СчА ЗМ 0 |

|

|

|

|

0 |

N |

1 |

1 |

|

N+1 |

ЗМN |

|

ЗМ1 |

|

ЗМ0 |

№ ЗМ |

|

|

|

|

|

|

ШД |

|

|

Рис. 5.18. Структура модульного ОЗУ с опережающей выборкой |

||||

При построении модуля динамического ОЗУ предусматривается специальный цикл регенерации, который представляет собой цикл считывания по адресу регенерации. Адрес регенерации формируется счетчиком, разрядность которого определяется разрядностью кода адреса строк. Число циклов регенерации равно числу строк в матрице. Поскольку регенерация осуществляется одновременно во всех ЗЭ выбранной строки, цикл обращения к матрице реализуется при отсутствии разрешающего сигнала ВМ, когда разрядные шины изолированы от шины ввода-вывода.

Время, необходимое для регенерации одной строки, равно длительности цикла считывания. В это время обращение к микросхеме запрещено. Для регенерации m строк требуется время mxtсч , что составляет часть от периода регенерации Трег, равного 1-2 мс. В част-

Глава 5. Оперативная память |

92 |

ности, для модулей ОЗУ на БИС К565РУ1 время занятости на регенерацию составляет 1,3% общего времени работы ОЗУ. Микросхемы К565РУЗ, РУ5 и РУ6 построены по такому же принципу, как и микросхема К565РУ1 (pис. 5.19), но имеют некоторые особенности, в частности, в их структуре предусмотрен мультиплексор адресного кода. Адресация осуществляется в два такта: вначале в ИС вводят адрес строки, а затем столбца. Ввод той или другой половин адресного кода сопровождается стробирующими сигналами RAS и CAS соответственно. На рис. 5.20 - временные диаграммы работы микросхемы типа КР565РУ6 в режимах записи, считывания и регенерации.

Существует несколько способов регенерации информации в динамическом ОЗУ. Наибольшее распространение получил способ равномерно распределённой регенерации, когда время регенерации Трег разбивается на равные интервалы времени с длительностью tрег=Tрег/ mp, где mp - число строк ЗЭ в ОЗУ. В конце каждого интервала формируется цикл регенерации, осуществляющий восстановление информации в одной из строк матрицы ЗЭ.

Другим способом является пакетная, или групповая, регенерация, в соответствии с которой в конце каждого Трег формируются mp циклов регенерации. При этом получается выигрыш во времени но и более высокий уровень помех в шинах электропитания по сравнению с равномерно распределённой регенерацией.

а0 |

|

а0 |

|

|

|

|

x1...x32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а5 |

|

|

|

Матрица 32х46 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

а1 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

а0 |

ДешифраторХ Ключивыборки |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

РегистрХ |

строк |

|

Селектор опорной |

строки |

|

|

|

Опорная строка 2 |

|

|

|||||

|

а5 |

|

|

|

|

|

|

|||||||||

а2 |

|

|

|

|

|

|

|

|

|

|

|

Опорная строка 1 |

|

|

||

а3 |

|

|

|

|

Ф1 |

|

|

|

|

Ф2 |

Усилители считывания |

|

|

|||

|

|

|

|

|

|

|

|

Регенер. |

|

|

||||||

а4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а5 |

|

|

|

|

|

|

|

а5 |

|

|

|

Матрица 32х64 |

|

|

||

|

|

а5 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

x ...x |

|

|

|

|

|

|

|

|

||

|

|

|

|

Ф1 |

|

|

33 |

64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выбор |

|

|

|

|

|

1 |

|

|

64 |

|

|

|

|

|

|

|

строки |

|

|

|

|

Ф3 |

|

|

|

|

|||

|

|

|

|

|

Выбор |

|

Ключи выборки |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||

ТС |

|

1 |

|

|

|

|

разряда |

|

|

|

столбцов |

|

|

|||

|

|

|

|

|

|

|

|

|

|

Дешифратор Y |

|

|

||||

Разреш. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

обращ. |

|

|

|

|

|

|

|

|

|

|

а6 |

а6 |

|

а11 |

а11 |

|

к адресу |

1 |

|

|

|

|

|

|

|

|

|

|

|||||

ВМ |

|

|

|

|

|

|

|

|

|

|

|

Регистр Y |

|

|

||

Разреш. |

|

|

|

& Ф |

|

& Ф |

|

|

|

|

|

|

|

|||

обращ. |

|

|

|

|

|

|

|

|

|

|

|

|

||||

по инф. |

Ф1 |

Ф2 |

|

|

3 |

|

|

3 |

а6 |

а7 |

а8 |

а9 а10 а11 |

|

|

||

входу и |

|

|

|

|

|

|

|

|

||||||||

выходу |

|

|

|

|

|

|

|

|

Ф4 |

|

|

|

|

|

|

|

|

|

|

Ф1 |

Ф2 |

|

|

Ф3 |

|

|

|

|

|

|

Запись/ |

||

|

|

|

|

|

|

|

|

|

|

|

& |

|||||

|

|

Управляющие |

|

|

|

|

|

|

|

|

|

считыв. |

||||

|

|

|

сигналы |

|

Ф4 |

|

Вывод |

|

|

Ввод |

|

|

||||

|

|

|

|

|

|

|

Разреш. |

F |

|

|

|

D |

|

ВМ |

||

|

|

|

|

|

|

|

вывода |

|

|

|

|

|||||

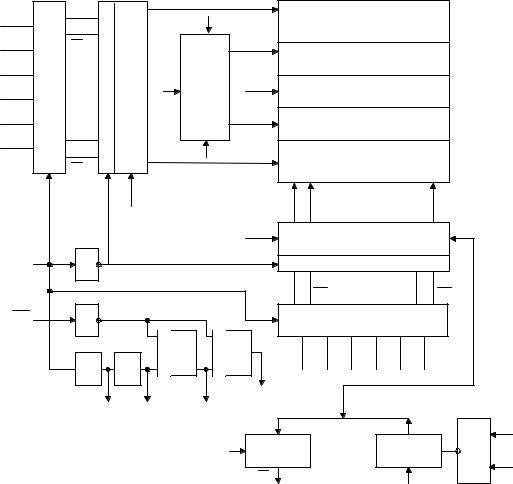

Рис. 5.19. Структурная схема БИС типа К565РУ1 динамического ОЗУ

Глава 5. Оперативная память |

|

|

|

|

93 |

|

ТЦ |

|

RAS |

τ |

ras=250 нс |

RAS |

|

|

|

||

|

|

|

|

|

|

CAS |

|

t |

A |

A0-A6 |

t |

|

|

|

|

|

|

A |

|

|

|

|

в) |

A0-A6 |

A7-A13 |

|

|

|

|

W/R |

|

|

a) |

|

|

|

|

|

|

|

|

DI |

|

|

|

|

|

A |

|

|

|

|

|

W/R |

|

|

б) |

|

|

|

|

|

|

|

|

DO |

|

|

|

|

|

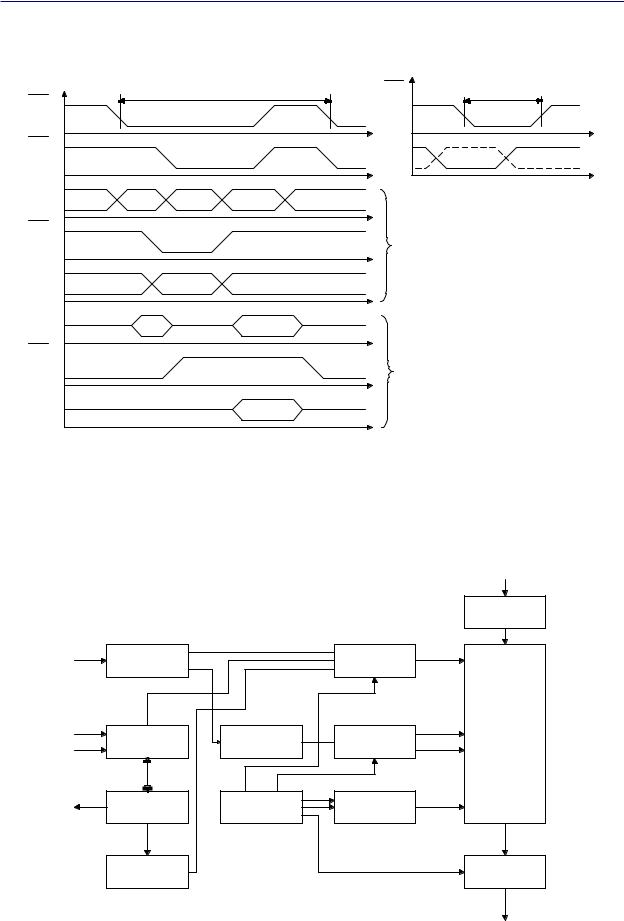

Рис. 5.20. Временные диаграммы работы БИС КР565РУ6 в режиме: а - записи; б - считывания; в - регенерации

ВхД

|

|

|

РгВхД |

А |

|

МлА |

Н |

РгА |

|

||

ОБР |

|

|

RAS |

БМУ |

ДШТС |

БФТС |

|

ЗАП |

|

|

CAS |

РГН |

БВД |

БФСЗ |

|

ГРгН |

|

||

СчА РгН |

|

|

РгВыхД |

ВыхД

Рис. 5.21. Базовая схема для ОЗУ на базе динамических БИС памяти

Глава 5. Оперативная память |

94 |

На рис. 5.21 показана базовая схема для ОЗУ на динамических БИС памяти. Работа схемы осуществляется следующим образом. Код адреса обращения принимается регистром адреса РгА, далее часть разрядов адреса поступает на входы мультиплексора адреса МлА, а другая их часть -на входы дешифратора тактовых сигналов ДшТС. При подаче на блок местного управления БМУ сигнала обращения.

ОБР сначала запускается блок выработки временной диаграммы БВД, а затем МлА и блок формирования тактовых сигналов БФТС RAS и CAS. В результате на блок накопителя Н поступают мультиплексированные разряды кода адреса и один из сигналов RAS или САS. При этом, если на входе БМУ отсутствует сигнал записи ЗП, то в ОЗУ реализуется режим считывания информации, которая из Н поступает на регистр выходных данных РгВыхД и далее - на процессор. При наличии на входе БМУ сигнала ЗП запускается в режиме обращения блок формирования сигнала записи БФСЗ и в Н производится запись информации из регистра данных РгВхД.

При наличии импульса на выходе генератора регенерации ГРгн, работающего с периодом Трег=Трег/mp, где mp - число строк элементов памяти в ДОЗУ, к состоянию счётчика адресов регенерации СчАРгн прибавляется 1. Код адреса регенерации поступает из СчАРгн в МлА и после запуска БЕД - далее в блок накопителя Н. Из ОЗУ в процессор видаётся признак регенерации РГН. При этом ВФТС формирует тактовые сигналы RAS, поступающие одновременно на все БИС ЗУ блока накопителя. Формирование тактовых сигналов САS в цикле регенерации не является обязательным.

Необходимым условием правильного функционирования ОЗУ на БИС памяти динамического типа является нормальное завершение любого рабочего цикла. Для этого требуется, чтобы между сигналами ОБР и РГН не возникало конфликтных ситуаций, так как сигнал РГН, как правило, формируется асинхронно. Одним из способов устранения конфликтов является размещение генератора регенерации и счётчика адресов регенерации в процессоре. Это позволяет в максимальной степени приблизить источники сигналов ОБР и РГИ и устранить разницу в задержках распространения сигналов.

В цепях электропитания ДОЗУ возникают помехи, вызванные импульсным характером тока потребления БИС ЗУ динамического типа. Особенно велики помехи во время регенерации информации, так как в активном состоянии в этом режиме находятся все элементы, входящие в состав ОЗУ. При отсутствии специальных средств по снижению уровня помех амплитуда помех во время цикла регенерации достигает больших значений. Это уменьшает область устойчивой работы ОЗУ и может вызвать ошибки в информации при его функционировании.

Достаточно эффективным способом уменьшения помех на шинах электропитания БИС ЗУ является размещение в непосредственной близости от микросхем памяти высокочастотных керамических конденсаторов фильтров. Они гасят высокочастотные импульсные выбросы, возникающие по фронту и спаду сигнала RAS. Уменьшению уровня помех способствует также сокращение числа одновременно регенерируемах микросхем памяти. Возможны и другие способы.

Надёжность ОЗУ в большей степени определяется надёжностью микросхем памяти. Нарушение функционирования БИС ЗУ имеет постоянный либо кратковременный характер. Причиной постоянной неисправности является отказ - необратимый физический дефект ЗУ, устраняемый только при ремонте ОЗУ. Кратковременное же нарушение функционирования БИС ЗУ возникает вследствие сбоев, которые вызывают временное изменение логического состояния отдельных бит, правильное состояние которых восстанавливается при записи истинных данных - регенерации. Причиной сбоев ОЗУ являются упоминавшиеся помехи в цепях электропитания а также деградация параметров элементов памяти и a-частица. Для ОЗУ наиболее характерны отказы отдельных бит, а не строк и столбцов.