- •Оглавление

- •Введение

- •Глава 1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ

- •1.1. Понятие архитектуры вычислительной системы. Структура аппаратной части и назначение основных функциональных узлов

- •1.2. Базовые параметры и технические характеристики ЭВМ

- •Контрольные вопросы к главе 1

- •Глава 2. СТРУКТУРА И ФУНКЦИОНИРОВАНИЕ ПРОЦЕССОРА

- •2.2. Устройство управления с программируемой логикой

- •2.3. Устройство управления с жесткой логикой

- •2.4. Слово состояния процессора

- •2.5. Микроконтроллеры

- •2.6. Особенности организации однокристальных и секционных микропроцессоров

- •2.8. Архитектура и функционирование микропроцессора

- •Контрольные вопросы к главе 2

- •Глава 3. СИСТЕМЫ КОМАНД МИКРОЭВМ

- •3.1. Язык микроопераций для описания вычислительных устройств

- •3.2. Структура и формат команд микропроцессора и МПС

- •3.3. Программирование микропроцессора

- •Контрольные вопросы к главе 3

- •Глава 4. ТЕНДЕНЦИИ РАЗВИТИЯ АРХИТЕКТУРЫ И АППАРАТНОГО ОБЕСПЕЧЕНИЯ ЭВС

- •4.1. Требования различных задач к вычислительным ресурсам и ограничения фон-Неймановской архитектуры

- •4.2. Распараллеливание процессов обработки информации

- •4.3. Принцип совмещения операций. Конвейерная обработка информации

- •4.4. Архитектура процессоров с сокращенным набором команд

- •4.5. Применение кэш-памяти и повышение пропускной способности

- •4.6. Транспьютеры

- •4.7. Развитие новых архитектурных принципов

- •4.8. Оценка производительности скалярного процессора

- •Контрольные вопросы к главе 4

- •Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

- •5.1. Классификация и иерархическая структура памяти ЭВМ

- •5.2. Запоминающие элементы статических ОЗУ

- •5.3. Запоминающие элементы динамических ОЗУ

- •5.4. Структуры матриц накопителей информации

- •5.5. Структура построения БИС статических ОЗУ и модулей памяти

- •5.6. Структура построения БИС динамических ОЗУ

- •5.7. Элементная база и организация постоянных запоминающих устройств

- •Контрольные вопросы к главе 5

- •Глава 6. ВНЕШНИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА НА МАГНИТНЫХ НОСИТЕЛЯХ

- •6.1. Принцип записи двоичной информации на магнитную поверхность

- •6.3. Методы записи цифровой информации на магнитный носитель

- •6.4. Воспроизведение информации и повышение ее достоверности

- •6.5. Накопители на гибких магнитных дисках и их контроллеры

- •6.6. Накопители на жестких магнитных дисках типа винчестер и их контроллеры

- •6.7. Накопители на сменных магнитных дисках

- •6.8. Накопители на магнитной ленте

- •Контрольные вопросы к главе 6

- •Глава 7. ОПТИЧЕСКИЕ И МАГНИТООПТИЧЕСКИЕ ВЗУ

- •7.1. Лазерные системы и их применение в устройствах внешней памяти

- •7.2. Оптические диски

- •7.3. Магнитооптические диски

- •7.4.Устройство накопителя на оптических дисках

- •Контрольные вопросы к главе 7

- •Глава 8. ВЗУ НА ЦМД-СОДЕРЖАЩИХ МАТЕРИАЛАХ

- •8.1. Принципы возникновения цилиндрических магнитных доменов

- •8.2. Организация продвижения ЦМД

- •8.4. Структура ЦМД-микросхем памяти

- •8.5. Устройство ЦМД-накопителя

- •Контрольные вопросы к главе 8

- •Глава 9. ВЗУ НА ОСНОВЕ ГОЛОГРАФИИ

- •9.1. Носители информации голографических ЗУ

- •9.2. Создание голограмм

- •9.3. Воспроизведение голограмм

- •9.4. Голографические ЗУ двоичной информации

- •Контрольные вопросы к главе 9

- •Глава 10. ОРГАНИЗАЦИЯ БЕЗАДРЕСНОЙ И ВИРТУАЛЬНОЙ ПАМЯТИ

- •10.1. Стековая память

- •10.2. Ассоциативная память

- •10.3. Виртуальная память со страничной организацией

- •10.4. Структура виртуальной памяти при сегментном распределении

- •Контрольные вопросы к главе 10

- •Глава 11. НАЗНАЧЕНИЕ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ

- •11.1. Классификация периферийных устройств

- •Контрольные вопросы к главе 11

- •Глава 12. УСТРОЙСТВА АВТОМАТИЧЕСКОГО СЧИТЫВАНИЯ ТЕКСТОВ

- •12.1. Устройства автоматического ввода печатных текстов

- •12.2. Методы распознавания образов печатных знаков

- •12.3. Устройства автоматического ввода рукописных текстов

- •12.4. Средства считывания и хранения графических изображений поврежденных рукописных текстов

- •12.5. Кодирование текстов для электронных публикаций

- •Контрольные вопросы к главе 12

- •Глава 13. УСТРОЙСТВА АВТОМАТИЧЕСКОГО ВВОДА ИЗОБРАЖЕНИЙ

- •13.1. Устройства автоматического ввода одноконтурных изображений

- •13.2. Устройства автоматического ввода многоконтурных и полутоновых изображений

- •13.3. Считывание цветных изображений

- •Контрольные вопросы к главе 13

- •Глава 14. УСТРОЙСТВА ПОЛУАВТОМАТИЧЕСКОГО ВВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ДИГИТАЙЗЕРЫ

- •14.1. Устройство рабочего поля планшета

- •14.2. Структурная схема дигитайзера и ее функционирование

- •Контрольные вопросы к главе 14

- •Глава 15. УСТРОЙСТВА ВВОДА - ВЫВОДА РЕЧЕВОЙ ИНФОРМАЦИИ

- •15.1. Модель речи

- •15.2. Структурная схема анализатора речи

- •15.3. Структура устройств ввода речи

- •15.4.Устройства вывода речевой информации - синтезаторы

- •Контрольные вопросы к главе 15

- •Глава 16. УСТРОЙСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ - ДИСПЛЕИ

- •16.1. Классификация дисплеев

- •16.2. Способы формирования изображения на экране телевизионного дисплея

- •16.3. Структурная схема текстового телевизионного дисплея

- •16.4. Структурная схема графического телевизионного дисплея

- •16.5. Устройство плоских экранов

- •Контрольные вопросы к главе 16

- •Глава 17. АВТОМАТИЧЕКИЕ УСТРОЙСТВА РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ - ГРАФОПОСТРОИТЕЛИ

- •17.1. Классификация и устройство графопостроителей

- •17.2. Принципы работы графопостроителя по вычерчиванию

- •17.3. Структурная схема планшетного графопостроителя

- •17.4. Структурная схема растрового графопостроителя

- •Контрольные вопросы к главе 17

- •Глава 18. АППАРАТУРА ПРИЕМА-ПЕРЕДАЧИ ИНФОРМАЦИИ

- •18.1. Обобщенная структурная схема аппаратуры передачи дискретной информации

- •18.2. Характеристики аппаратуры передачи данных

- •18.3. Принципы организации интерфейсов

- •18.4. Классификация интерфейсов

- •Контрольные вопросы к главе 18

- •Глава 19. АВТОМАТИЧЕСКИЕ УСТРОЙСТВА ВВОДА-ВЫВОДА АНАЛОГОВОЙ ИНФОРМАЦИИ В ЭВМ

- •19.1. Назначение устройств ввода-вывода аналоговой информации в ЭВМ

- •19.2. Принципы построения ЦАП и АЦП

- •19.3. Принципы построения и программирование системы ввода-вывода аналоговой информации в ЭВМ

- •Контрольные вопросы к главе 19

- •Глава 20. КАНАЛЫ ВВОДА-ВЫВОДА И АППАРАТУРА СОПРЯЖЕНИЯ

- •20.2. Организация обмена массивами данных

- •20.3. Мультиплексный канал

- •20.4. Селекторный канал

- •20.5. Устройства сопряжения - мультиплексоры передачи данных

- •Контрольные вопросы к главе 20

- •Глава 21. УСТРОЙСТВА ЗАЩИТЫ ОТ ОШИБОК В ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ

- •21.1. Причины возникновения ошибок в передаваемой информации

- •21.2. Краткая характеристика способов защиты от ошибок

- •21.3.Обнаруживающие коды - с проверкой на четность и итеративный код

- •21.4. Корректирующий код Хэмминга

- •21.5. Циклические коды

- •21.6. Циклический код Файра как средство коррекции пакетов ошибок

- •Контрольные вопросы к главе 21

- •ЗАКЛЮЧЕНИЕ

- •Приложение 2

- •Приложение 3

- •Приложение 4

- •Приложение 5

- •Приложение 6

- •Приложение 7

- •Приложение 8

- •Приложение 9

- •Приложение 10

- •Приложение 11

- •Приложение 12

- •Приложение 13

- •Приложение 14

- •Приложение 15

- •Приложение 16

- •Приложение 17

- •Приложение 18

- •Приложение 19

- •Приложение 20

- •Приложение 22

- •Приложение 23

- •Приложение 24

- •Приложение 25

- •Приложение 26

- •Предметный указатель

- •Список литературы

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

74 |

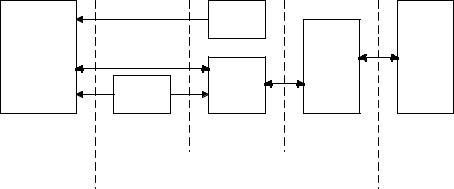

На рис. 4.15 приведены варианты архитектуры мультипроцессорных систем со слабой связанностью типа «танцевальный зал» и «рандеву».

По виду взаимоотношений процессоров мультипроцессорные системы могут быть, кроме того, подразделены на системы с аутократическим управлением (отношения «хозяев» и «подчинённых») и с равноправными процессорами, имеющими одинаковые возможности доступа к общей шине. Кроме того, в ВС может осуществляться как одновременность работы - независимое, асинхронное функционирование параллельно работающих процессоров, так и противоположное ему - синхронное (жёсткое) взаимодействие в составе мультипроцессорной системы.

4.8. Оценка производительности скалярного процессора

Любой алгоритм вычислительного процесса машин потока данных можно разбить на группы независимых операций, последовательно обрабатываемых машиной. Количество операций, находящихся в одной такой группе, определяет величину параллелизма n вычислительного процесса на данном этапе или шаге вычисления. Необходимым условием полной загрузки многопроцессорных машин должно быть выполнение следующего неравенства на каждом шаге вычисления:

N<n,

где N - количество процессоров.

Это только нижняя оценка требуемого неравенства. Это неравенство должно быть уточнено в той части, что N необходимо умножить на величину С, характеризующую максимально возможное количество операций в каждом процессоре, которое должно в них одновременно обрабатываться для обеспечения полной загрузки ЭВМ. Фактически должна быть учтена глубина конвейеризации по каждому параллельно работающему процессору. В этом случае неравенство примет вид:

NC<n.

Поэтому предельные возможности по загрузке разрабатываемой ЭВМ можно оценить следующими соотношениями:

если NС<n, то полная загрузка;

если NC>n, то загрузка будет пропорциональна соотношению N/nC. Для структуры, показанной на рис. 4.10:

NC=(NпрСпр + Nк1Ск+1 + Nк2Ск2 + NапСап)Nк,

где Nпр, Nап, Nк1, Nк2 - количество параллельно работающих процессоров, модулей ассоциативной памяти и коммутаторов в одном канале; Спр, Сап, Ск1, Ск2 - соответствующие величины глубины их конвейеризации.

Для простоты будем считать, что пропускные способности коммутаторов, процессоров и ассоциативной памяти согласованы, равны, и все устройства работают с одним и тем же темпом П. Тогда максимальная производительность системы будет равна ПNк. Величина NC определяет количество операций, над которыми вычислительная система потока данных должна работать одновременно, чтобы была обеспечена ее 100%-ая загрузка.

Из этих соотношений видно, что чем меньше величина NC, тем более эффективно будет работать комплекс при малом параллелизме задачи. В традиционных ЭВМ с увеличением значений n и N возможности человека как программиста резко падают, начиная с N=3- 4. Именно поэтому пользователи Connection machine, имеющей в своём составе более 64 тысяч элементарных процессоров сообщают об их только 10%-ной средней загрузке на ориентированных на эту машину задач. Кроме того, в традиционных машинах параллелизм выявляется человеком или процессором на небольшом участке программы, в лучшем случае в десяток команд. Поэтому средний параллелизм выполнения скалярных операций для машин ОКОД архитектуры, таких, как, например, супер-ЭВМ «Эльбрус-2» не превосходит 2 - 3, а для векторных конвейерных машин типа Cray не превышает 10.

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

75 |

Основным звеном, сдерживающим производительность машины потока данных является ассоциативная память. Ассоциативная память выполняет несколько команд в зависимости от кода операции. Ключом поиска - дескриптором - является код, состоящий из разрядов номера команды, индекса, итераций и активации. При реализации памяти на интегральных схемах БИКМОП структуры с разрешающей способностью технологического процесса 0,7 мкм, период темпа работы не превышает 10 нс. Модуль такого порядка можно реализовать объёмом в 32 тыс. ключей. Из ста модулей такой памяти можно иметь достаточный объём АП - более 3• 106 слов. С таким темпом может справиться работа 2-4-х транспьютеров, в каждом из которых может обрабатываться по два пакета одновременно в конвейерном режиме. 4 коммутатора обеспечат необходимый темп работы. Максимальная производительность ПNK=1010 операций/с будет достигнута только в случае, когда параллелизм задачи на объёме памяти 3• 106 слов будет не меньше, чем

NC=Nкан(NапСап + NкмрСкмр + NиуСиу + NкмапСкмап),

где Nкан - число каналов в системе, Nиу, Nкмр и Nкмап - число однотипных устройств ( исполняющих устройств - процессоров, коммутаторов) в блоке каждого канала; Сап, Скмр, Сиу, Скмап - уровень конвейеризации каждого устройства.

Так, для обеспечения темпа продвижения информации по кольцу, нa современной

технологической базе необходимо иметь Nап=1, Nкмр=2, Nиу=2, Nкмап=4 и соотватетвенно Сап=2, Скмр=2, Сиу=2, Скмап=1, что соответствует времени отерации АП 20 нс, времени операции КМР 40 нс, времени операции на транспьютере 40 нс и времени операции КМАП 40 нс.

Общая максимальная производительность системы каналов при полной загрузке будет 1010 оп/с. Полная загрузка системы будет на участках задачи, где параллелизм вычислительного процесса превосходит значение n=NK=1300. Во всех остальных случаях загрузка будет пропорциональна Kз=n/NС.

Оценка производительности и загрузки машины потока данных здесь проводилась без учёта возможностей векторного процессора, загрузка которого осуществляется от рассмотренного скалярного процессора, что может увеличить производительность ВС более чем на порядок.

Контрольные вопросы к главе 4

1. Какими причинами объясняется принципиальная невозможность создания ЭВМ, удовлетворяющей высоким требованиям различных задач по производительности и по объему памяти?

2.Назовите четыре основные характеристики фон-Неймановской архитектуры ЭВМ.

3.Чему равна предельная производительность процессора фон-Неймановской архитектуры?

4.Перечислите этапы ввода в архитектуру ЭВМ в процессе их развития методов распараллеливания процессов обработки информации.

5.Что является элементной базой многопроцессорной ЭВМ?

6.В чем состоит опережающая выборка команд?

7.В чем состоит конвейерный поточный режим исполнения команд программы?

8.Во сколько раз в пределе может быть повышена производительность при конвейерной

обработке?

9. За счет чего достигнуто сокращение числа команд в наборе команд КСНК (RISK-процессоров)? 10. В чем состоит логическая операция над байтом - маскирование?

11. Перечислите достоинства КСНК.

12. Каково назначение и какого порядка емкость высокоскоростного буферного ЗУ - кэш-памяти? 13. Приведите характеристикии и назначение транспьютера.

14. Поясните назначение линков в транспьютере.

15. Назовите состав семейства транспьютеров.

16. Какова разрядность регистрового стека транспьютера?

17. Какие функции выполняет сопроцессор транспьютера?

18. Перечислите отличия между микропроцессором, микроконтроллером и транспьютером. 19. В чем отличие блока событий транспьютера от обычного канала?

20. С каким количеством процессоров выпускаются современные мультипроцессоры?

21. Назовите три варианта архитектур ЭВМ, реализующих принцип параллельной обработки.

Глава 4. Тенденции развития архитектуры и аппаратного обеспечения ЭВС |

76 |

22.Что служит элементной базой МКМД машины?

23.В чем состоит отличие между векторным и матричным процессором?

24.Чем характеризуется архитектура суперЭВМ нового типа?

25.Поясните понятия “кластер”, “кластерная связь”.

26.Какой тип связи процессора с памятью обладает наибольшей степенью связанности? Наименьшей?

27.Чем измеряется величина параллелизма вычислительного процесса?

28.Чем объясняется низкий процент средней загрузки МКМД машины с коммутационной матрицей?

Глава 5. Оперативная память |

77 |

Глава 5. ОПЕРАТИВНАЯ ПАМЯТЬ

5.1. Классификация и иерархическая структура памяти ЭВМ

Память ЭВМ - функциональная часть ЭВМ, предназначенная для записи, хранения и выдачи данных. В соответствии с этим различают три режима заботы памяти: записи, хранения и считывания. Запись в запоминающее устройство (ЗУ) или считывание из него информации иначе называются обращением к ЗУ. Быстродействие памяти определяется продолжительностью операции обращения к ЗУ. Время обращения to при записи информации складывается из времени поиска операнда tп, стирания ранее записанной информации tст (при необходимости) и записи нового числа tзп:

to=tп+tст+tзп.

При считывании информации время цикла обращения складывается из времени поиска, времени считывания tсч и восстановления считанных кодов (при необходимости, в случае разрушающего считывания):

to=tп+tст+tвосст.

Запоминающие устройства разделяют: по использованию - на внешние и внутренние (или оперативные); по назначению - на сверхоперативные, оперативные, постоянные, буферные и внешние; по физическим принципам действия - на полупроводниковые, магнитные и оптические; по способу хранения информации - на статические и динамические; по способу доступа к заданной ячейке (для адресных ЗУ) - с последовательным, циклическим и произвольным доступом; по характеру обращения - с адресным обращением (или адресной выборкой) и с ассоциативным обращением (ассоциативной выборкой).

Для достижения в ЭВМ одновременно и большой информационной ёмкости и высокого быстродействия используется принцип иерархического построения памяти. Техническая реализация иерархических структур обеспечивает большую ёмкость памяти и малое время обращения, что позволяет решать на ЭВМ сложные задачи, требующие хранения большого количества данных. При иерархическом принципе построения структуры ЗУ логическая организация потоков информации должна быть такой, чтобы всё информационное поле ЭВМ или ВС представлялось в виде внутреннего абстрактного ЗУ с единым адресным пространством. Это абстрактное ЗУ называют виртуальным (кажущимся) ЗУ. Адресацию его ячеек осуществляют посредством абстрактных математических адресов с использованием страничных таблиц.

В иерархической структуре можно выделить следующие уровни памяти (рис. 5.1). Сверхоперативные ЗУ (СОЗУ) или местная память. Они имеют быстродействие,

соизмеримое с быстродействием процессора. Емкость СОЗУ обычно составляет от нескольких десятков до нескольких тысяч слов, а период обращения - десятые или сотые доли микросекунды. Они предназначаются для хранения ряда чисел, используемых некоторой текущей последовательностью команд программы. Сверхоперативные ЗУ применяют в том случае, если быстродействие процессора ограничивается быстродействием ОЗУ.

Глава 5. Оперативная память |

78 |

|

|

ПЗУ |

|

|

Процес- |

|

|

|

ВЗУ |

сор |

|

|

БЗУ |

|

|

|

|

||

|

СОЗУ |

ОЗУ |

|

|

|

|

|

|

|

Уровни |

I |

II |

III |

IV |

|

|

|

|

|

|

Внутренняя |

память |

|

Внешняя |

|

|

память |

Рис. 5.1. Схема иерархии ЗУ ЭВМ

Оперативные ЗУ (ОЗУ) или основная память, предназначены для хранения данных и программ текущих вычислений, а также программ, к которым следует быстро перейти, если в ходе вычислительного процесса возникло прерывание. ОЗУ современных ЭВМ имеют ёмкость от нескольких тысяч до сотен тысяч слов и период обращения от долей до нескольких микросекунд. ОЗУ может быть связано с процессором как непосредственными связями, так и через СОЗУ. В качестве элементов памяти ОЗУ и СОЗУ используются полупроводниковые элементы, тонкие магнитные пленки, ферритовые сердечники и др.

Постоянные ЗУ (ПЗУ) или односторонние ЗУ, предназначены только для хранения и считывания информации, которая не изменяется в процессе вычислений, например, постоянно используемые программы, различные константы, таблицы функций, микропрограммы и т.п. В ПЗУ информация записывается один раз при изготовлении, а при работе только считывается. Такие ПЗУ имеют меньшую аппаратную сложность, чем ОЗУ.

Буферные ЗУ (БЗУ). Эти ЗУ используются для промежуточного хранения данных при обмене между устройствами с разным быстродействием, например, между ОЗУ и ВЗУ. По емкости и быстродействию БЗУ занимают промежуточное место между ОЗУ и ВЗУ. Они могут быть построены на полупроводниковых элементах, ферритовых сердечниках и на магнитных дисках.

Внешние ЗУ (ВЗУ). Они предназначены для хранения больших массивов информации. Объём данных, которые могут одновременно храниться в таких ЗУ, обычно превышает сотни миллионов слов, однако период обращения к ним составляет от нескольких миллисекунд до нескольких десятков секунд. Данные, хранящиеся во внешних ЗУ, непосредственно не используются в вычислительном процессе, а передаются из ВЗУ в ОЗУ. В качестве внешних ЗУ чаще всего используют накопители информации на магнитных лентах (НМЛ), на гибких и жёстких магнитных дисках (НГМД, НЖМД), на микросхемах на основе материалов, содержащих цилиндрические магнитные домены (ЦМД), а также на оптических дисках.

Основой полупроводникового запоминающего элемента (ЗЭ) служит бистабильная схема триггера, состоящая из инверторов с перекрестными связями, с цепями управления для записи и считывания информации. Достоинством таких ЗЭ является единство технологического процесса изготовления как самих ЗЭ, так и элементов электронного обрамления - регистров, дешифраторов и др.

Разнообразие типов ЗЭ объясняет большое количество способов объединения ЗЭ в большие интегральные схемы, а также способов объединения БИС в накопитель.

Классификацию ЗЭ можно провести по трем типам признаков: физико-технологичес- ким, схемотехническим и системотехническим.

По физико-технологическим признаках ЗЭ подразделяются на выполненные на биполярных транзисторах и на выполненные на МДП-транзисторах. В основе биполярных тран-