- •Конспект лекций

- •1. Уровни детализации представления эвм

- •2. Основы булевой алгебры

- •6. Функция запрет по x1.

- •8. Функция неравнозначности (сумма по модулю 2, исключающее «или», xor)

- •9) Функция равнозначности (инверсия суммы по модулю 2)

- •3. Теоремы булевой алгебры

- •4. Синтез комбинационных логических схем в базисе с ограничениями

- •5. Дешифратор.

- •5.1 Синтез полного дешифратора.

- •5.2 Синтез неполного дешифратора.

- •6. Мультиплексор

- •7. Реализация функций на дешифраторах и мультиплексорах.

- •8. Элементы памяти. Триггерные схемы.

- •8.1 Асинхронный rs триггер (простейшая ячейка памяти)

- •8.2 Асинхронный триггер (базовая ячейка памяти)

- •8.3 Синхронный rs триггер.

- •8.4 Синхронный d триггер.

- •9. Регистры

- •9.1 Синтез параллельного статического регистра.

- •9.2 Синтез регистра для приема с нескольких направлений.

- •10. Счетчики

- •10.1 Синтез счетчиков с последовательным переносом

- •10.2 Синтез счетчиков с параллельным переносом.

- •11. Канонический синтез цифровых автоматов.

- •12. Структурный автомат.

- •13. Синтез управляющих автоматов

- •13.1 Уа Мура

- •13.2 Уа Мили

- •14. Шины.

- •15. Схемы сравнения

8.4 Синхронный d триггер.

Для этой схемы активный уровень – «1», пассивный – «0».

Таблица истинности:

С |

D (x) |

Qt+1 |

Сост |

0 |

* |

Qt |

Save |

1 |

0 |

0 |

Reset |

1 |

1 |

1 |

Set |

![]() ,

выход равен входу. Tdelay=40нс.

,

выход равен входу. Tdelay=40нс.

delay – задержка.

Условное графическое обозначение:

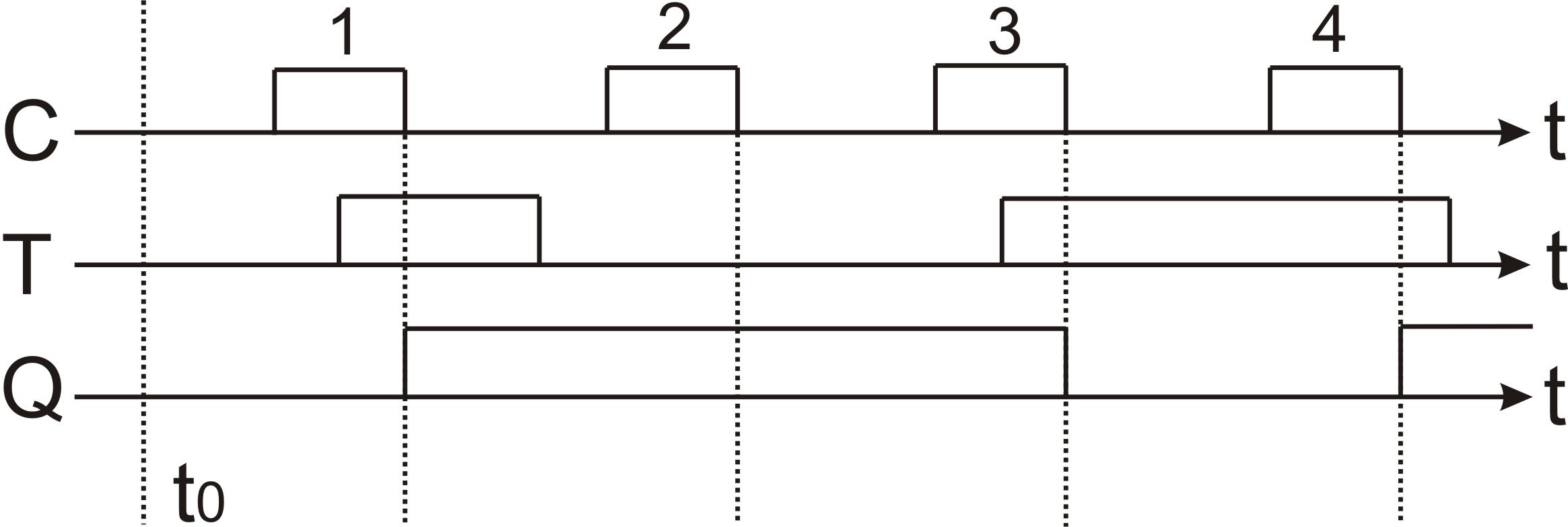

Временная диаграмма:

В одноступенчатом D-триггере любое изменение входного управляющего сигнала на входе вызывает реакцию на выходе. Изменение входного сигнала может быть и некорректным: запаздывание переключения (связано с гонками и помехами)

Гонки сигналов на входе триггера возникают вследствие разброса времен формирования входных сигналов. Особенно гонки опасны в схемах с обратными связями.

Помеха – это короткий сигнал, возникший по разным физическим причинам (скачка в сети питания, молния и т.д.)

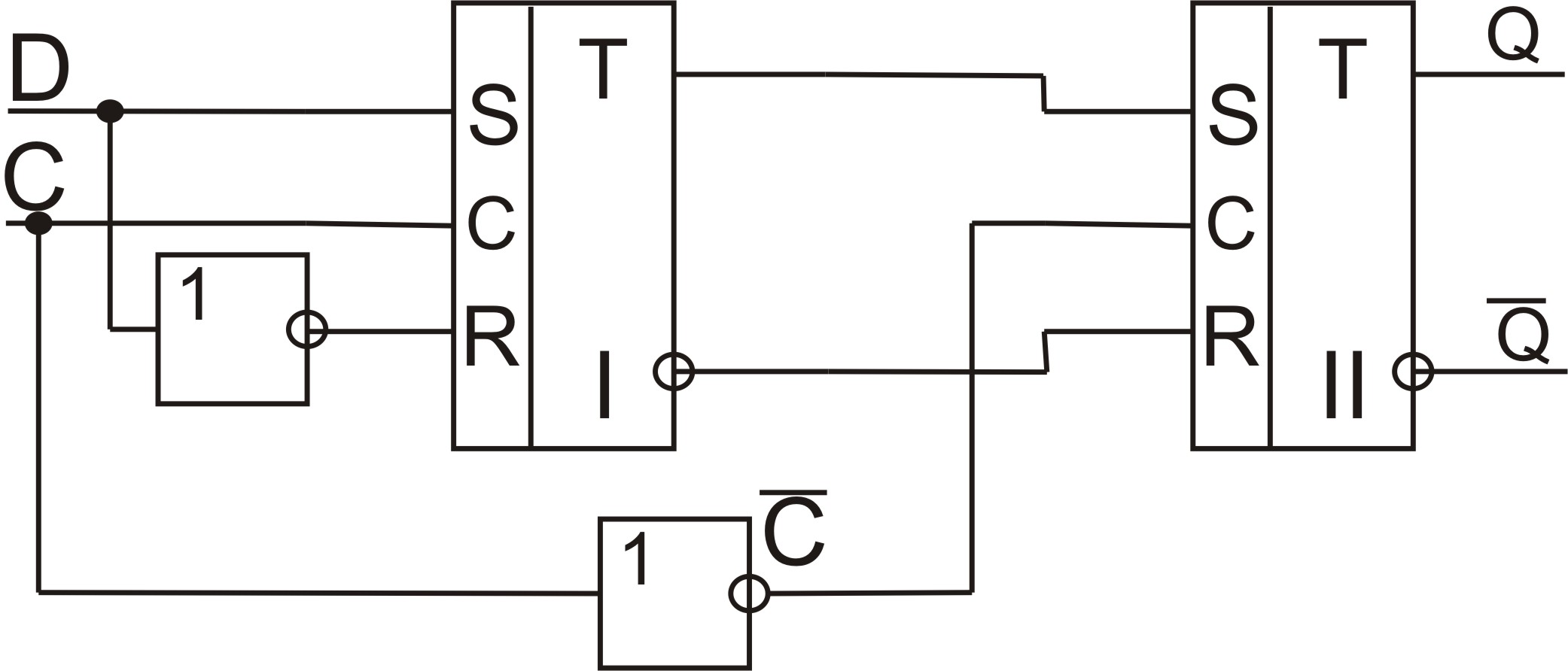

Для повышения устойчивости используют двухступенчатую схему D - триггера.

Первая ступень управляется синхронным сигналом «С», а вторая ступень его инверсией.

I ступень срабатывает при переключении «С» из 0 в 1., т.е. по переднему фронту синхроимпульсов. Когда «С» переключается из 1 в 0, I ступень в режиме хранения и не реагирует на изменение на входах.

А II ступень управляемая

![]() становится активной и переписывает

информацию с I ступени.

становится активной и переписывает

информацию с I ступени.

Таким образом, все устройство в целом срабатывает при переключении «С» из 1 в 0, то есть по заднему фронту (срезу) синхроимпульсов.

На условном обозначении это выглядит так:

При двухтактной синхронизации помеха может повлиять только в случае совпадения ее со срезом синхроимпульса. Т.о. вероятность влияния помехи очень мала.

Временная диаграмма двухступенчатого D – триггера:

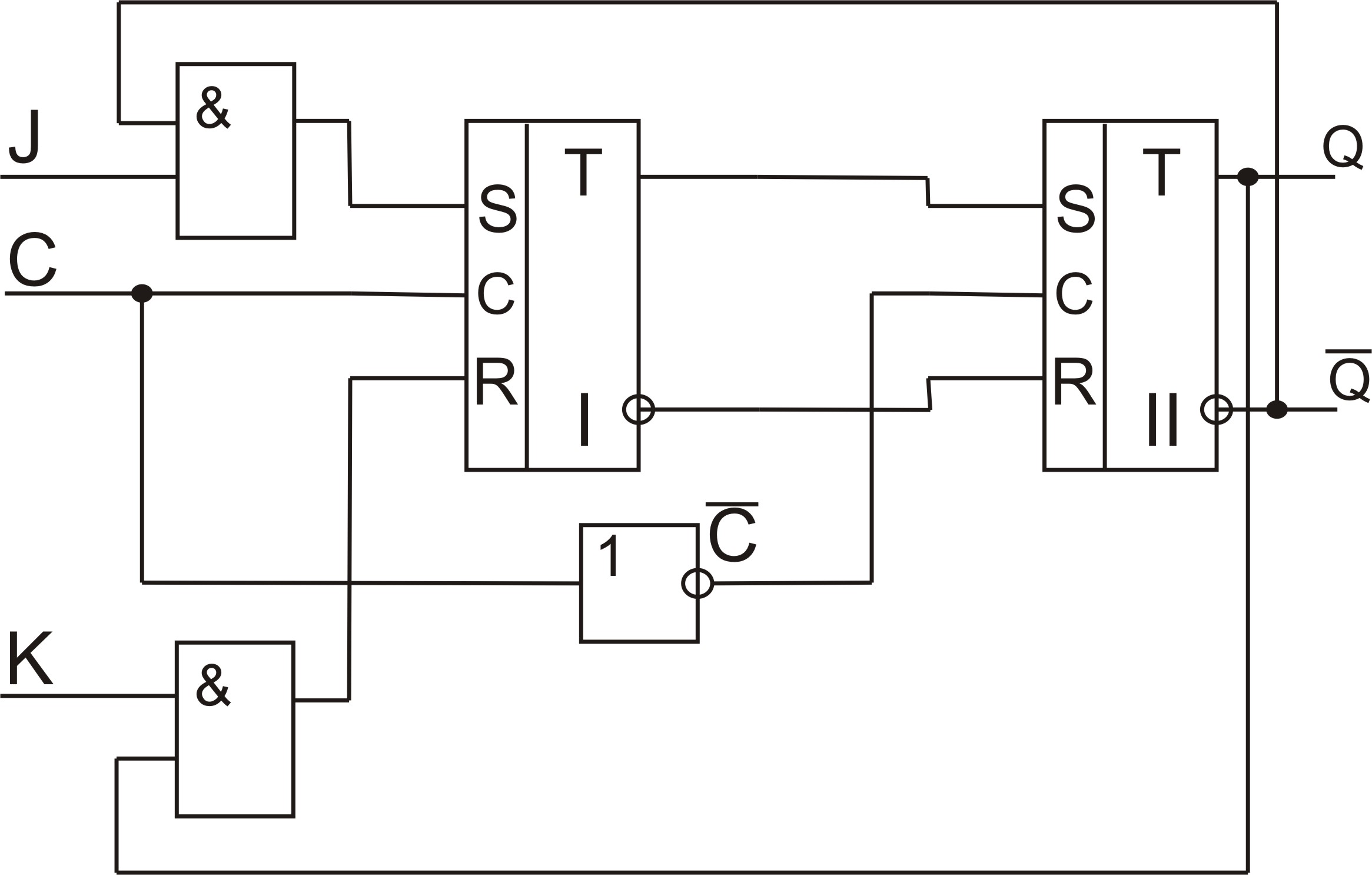

8.5 JK – триггер.

Таблица истинности:

C |

K |

J |

Qt |

Qt+1 |

Сост |

0 |

* |

* |

* |

Qt |

Save |

1 |

0 |

0 |

0 |

0 |

Save |

1 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

Set |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

Reset |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

Обратная таблица:

Qt |

Qt+1 |

J |

K |

0 |

0 |

0 |

0 |

0 |

1 |

||

0 |

* |

||

0 |

1 |

1 |

1 |

1 |

0 |

||

1 |

* |

||

1 |

0 |

1 |

1 |

0 |

1 |

||

* |

1 |

||

1 |

1 |

0 |

0 |

1 |

0 |

||

* |

0 |

Временная диаграмма:

8.6 Т – триггер.

Если на оба входа JK-триггера подавать одну и ту же информацию, то получится триггер с одним управляющим входом, называемым Т.

Условное графическое обозначение:

Таблица истинности:

С |

T |

Qt+1 |

0 |

* |

Qt |

1 |

0 |

Qt |

1 |

1 |

|

Временная диаграмма: