- •Конспект лекций

- •1. Уровни детализации представления эвм

- •2. Основы булевой алгебры

- •6. Функция запрет по x1.

- •8. Функция неравнозначности (сумма по модулю 2, исключающее «или», xor)

- •9) Функция равнозначности (инверсия суммы по модулю 2)

- •3. Теоремы булевой алгебры

- •4. Синтез комбинационных логических схем в базисе с ограничениями

- •5. Дешифратор.

- •5.1 Синтез полного дешифратора.

- •5.2 Синтез неполного дешифратора.

- •6. Мультиплексор

- •7. Реализация функций на дешифраторах и мультиплексорах.

- •8. Элементы памяти. Триггерные схемы.

- •8.1 Асинхронный rs триггер (простейшая ячейка памяти)

- •8.2 Асинхронный триггер (базовая ячейка памяти)

- •8.3 Синхронный rs триггер.

- •8.4 Синхронный d триггер.

- •9. Регистры

- •9.1 Синтез параллельного статического регистра.

- •9.2 Синтез регистра для приема с нескольких направлений.

- •10. Счетчики

- •10.1 Синтез счетчиков с последовательным переносом

- •10.2 Синтез счетчиков с параллельным переносом.

- •11. Канонический синтез цифровых автоматов.

- •12. Структурный автомат.

- •13. Синтез управляющих автоматов

- •13.1 Уа Мура

- •13.2 Уа Мили

- •14. Шины.

- •15. Схемы сравнения

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ УКРАИНЫ

ГОСУДАРСТВЕННОЕ ВЫСШЕЕ УЧЕБНОЕ ЗАВЕДЕНИЕ

«ДОНЕЦКИЙ НАЦИОНАЛЬНЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

Факультет компьютерных наук технологий

Кафедра компьютерной инженерии

Конспект лекций

по дисциплине

«Компьютерная схемотехника»

Донецк, 2010

Содержание

1. Уровни детализации представления ЭВМ 3

2. Основы булевой алгебры 3

3. Теоремы булевой алгебры 7

4. Синтез комбинационных логических схем в базисе с ограничениями 7

5. Дешифратор. 8

5.1 Синтез полного дешифратора. 9

5.2 Синтез неполного дешифратора. 10

6. Мультиплексор 11

7. Реализация функций на дешифраторах и мультиплексорах. 12

8. Элементы памяти. Триггерные схемы. 15

8.1 Асинхронный RS триггер (простейшая ячейка памяти) 15

8.2 Асинхронный триггер (базовая ячейка памяти) 17

8.3 Синхронный RS триггер. 18

8.4 Синхронный D триггер. 19

8.5 JK – триггер. 22

8.6 Т – триггер. 23

9. Регистры 24

9.1 Синтез параллельного статического регистра. 25

9.2 Синтез регистра для приема с нескольких направлений. 25

10. Счетчики 27

10.1 Синтез счетчиков с последовательным переносом 27

10.2 Синтез счетчиков с параллельным переносом. 28

11. Канонический синтез цифровых автоматов. 30

12. Структурный автомат. 30

13. Синтез управляющих автоматов 31

13.1 УА Мура 32

13.2 УА Мили 33

14. Шины. 35

15. Схемы сравнения 37

1. Уровни детализации представления эвм

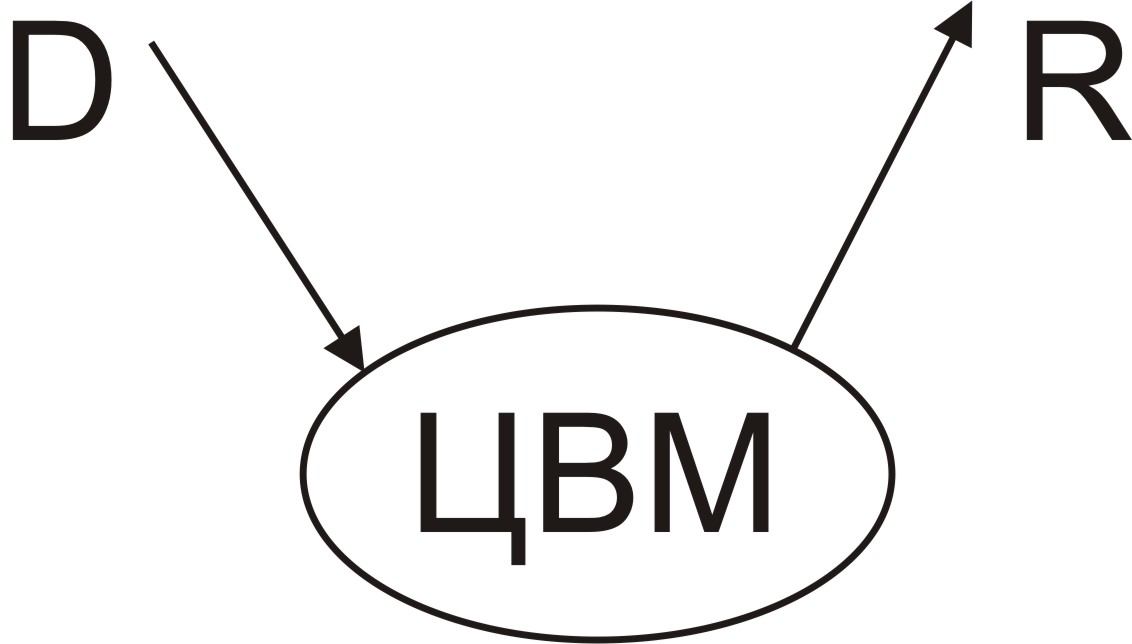

В курсе «Компьютерная схемотехника» предметом рассмотрения и исследования являются элементы и узлы цифровых вычислительных машин (ЦВМ). ЦВМ – это устройство, которое получает на вход данные D, обрабатывает их согласно алгоритму, который хранится в памяти машины, и генерирует результат R.

I уровень (в виде черного ящика)

|

|

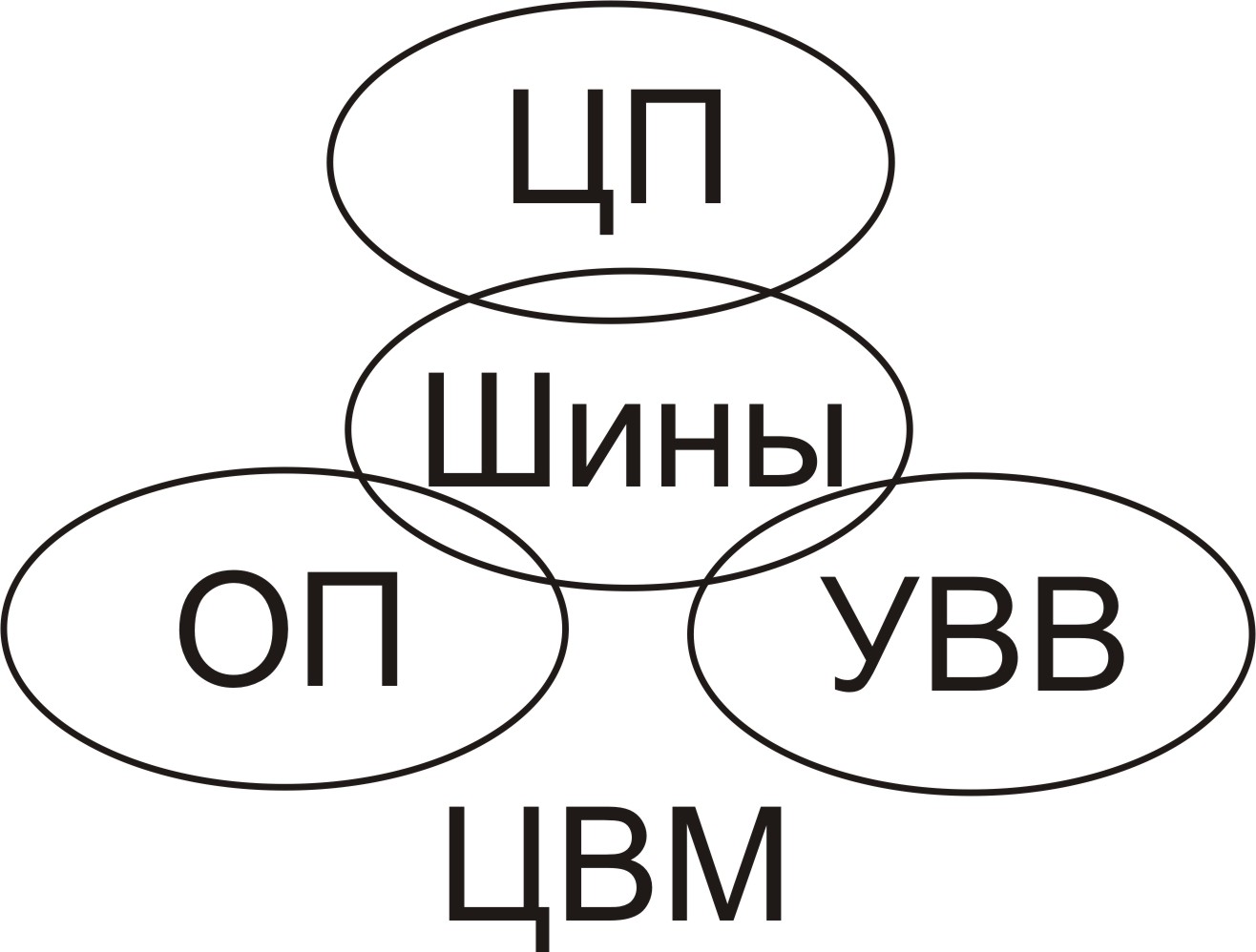

II уровень «Общая архитектура»

|

|

ЦП – центральный процессор,

ОП – оперативная память,

УВВ – устройство ввода/вывода.

Шины можно представлять как набор проводников в комплекте с шинным формирователем (ШФ).

ШФ – специальное устройство, которое обеспечивает корректный прием и передачу информации по шине.

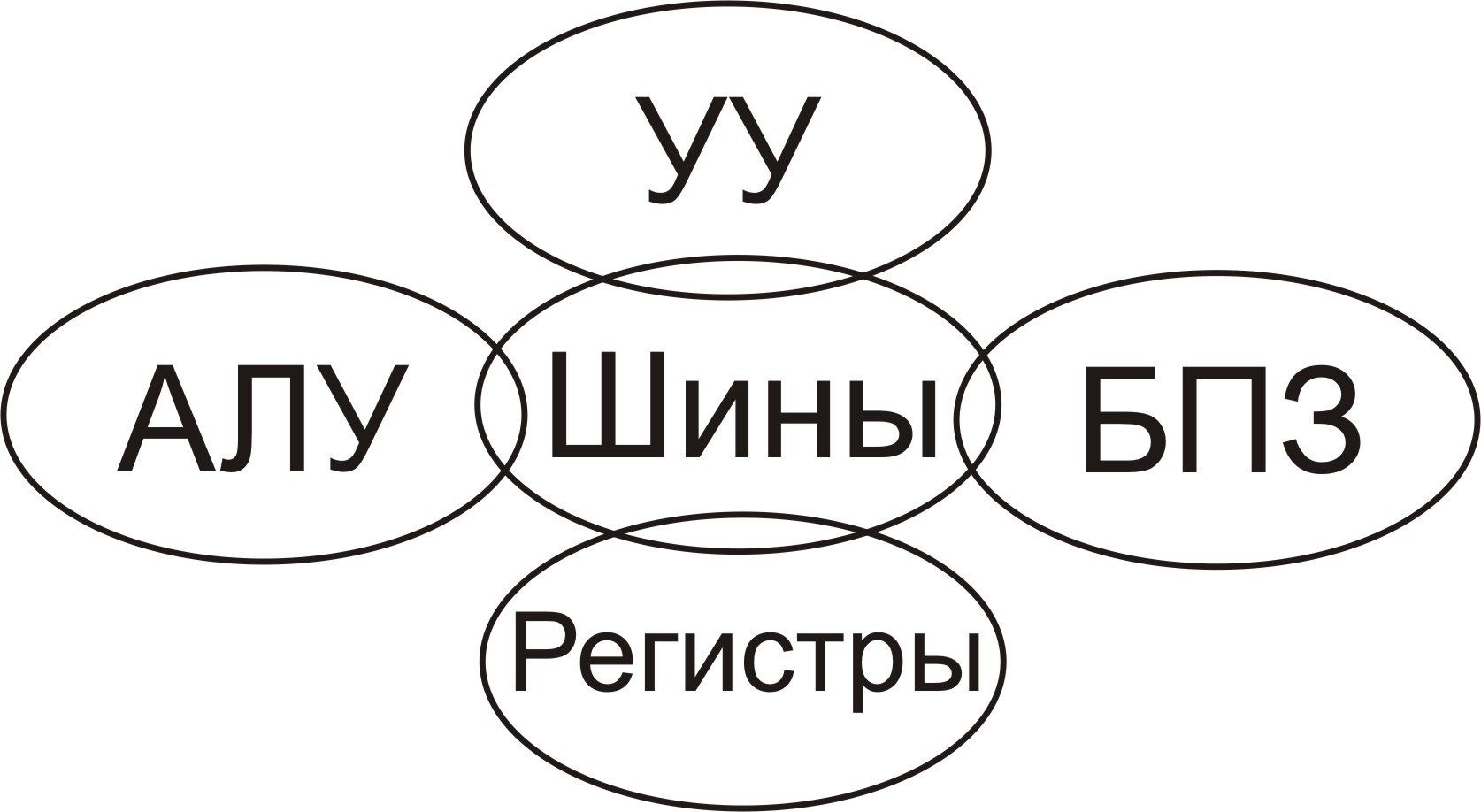

III уровень центрального процессора

|

|

УУ – устройство управления,

АЛУ – арифметико-логическое устройство (для обработки целых чисел),

БПЗ – блок арифметики с плавающей запятой,

Регистры – предназначены для хранения команд и адресов.

IV уровень детализации подробно рассматривает узлы III-го уровня. Например, устройство управления состоит из следующих деталей(узлов):

комбинационные логические схемы (КЛС), которые обеспечивают выполнение команд,

регистры, для хранения информации,

дешифраторы и мультиплексоры,

элементы программируемой логики(постоянные запоминающие устройства, программируемые логические матрицы ПЗУ, ПЛМ).

2. Основы булевой алгебры

В цифровой технике вся имнформация представляется в двоичном виде. Теоретической основой обработки битовой информации является булева алгебра.

Аргумент булевой функции(БФ) X может быть равен 0 или 1, и булева функция Y может принимать значения 0 или 1.

X € {0, 1};

Y = f(x1 x2 … xn) € {0, 1}

Для реализации основных булевых функций применяются соответствующие логические элементы.

Рассмотрим набор наиболее часто используемых булевых функций, их таблицы истинности, свойства, формулы и соответствующие им логические элементы.

1. Инверсия

y

=

|

x

y

0

1

1

0 |

|

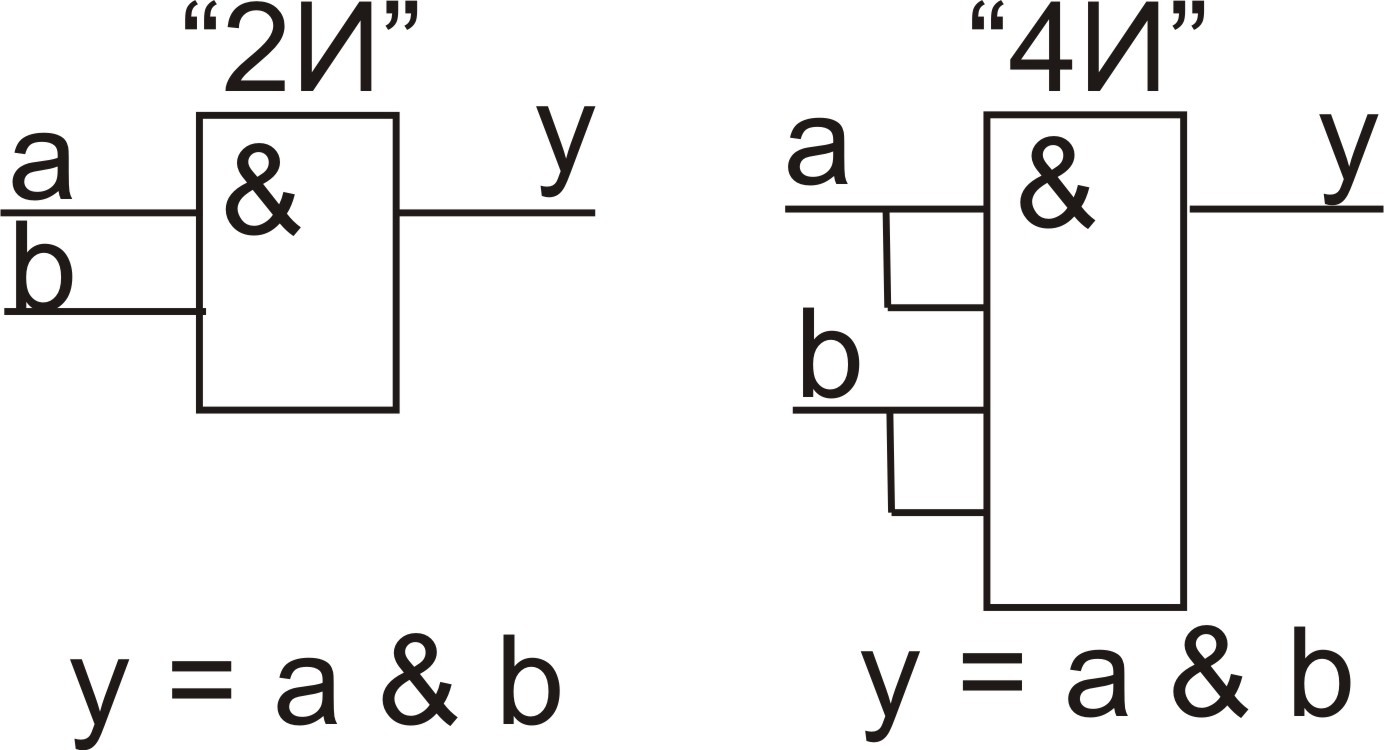

2. Логическое умножение («И», коньюнкция, AND)

y = a & b |

a

b

y

0

0

0

0

1

0

1

0

0

1

1

1 |

|

Свойства:

1) a & 0 = 0; 2) a & 1 = a; 3) a &

a &…& a = a, 4) a &

![]() = 0

= 0

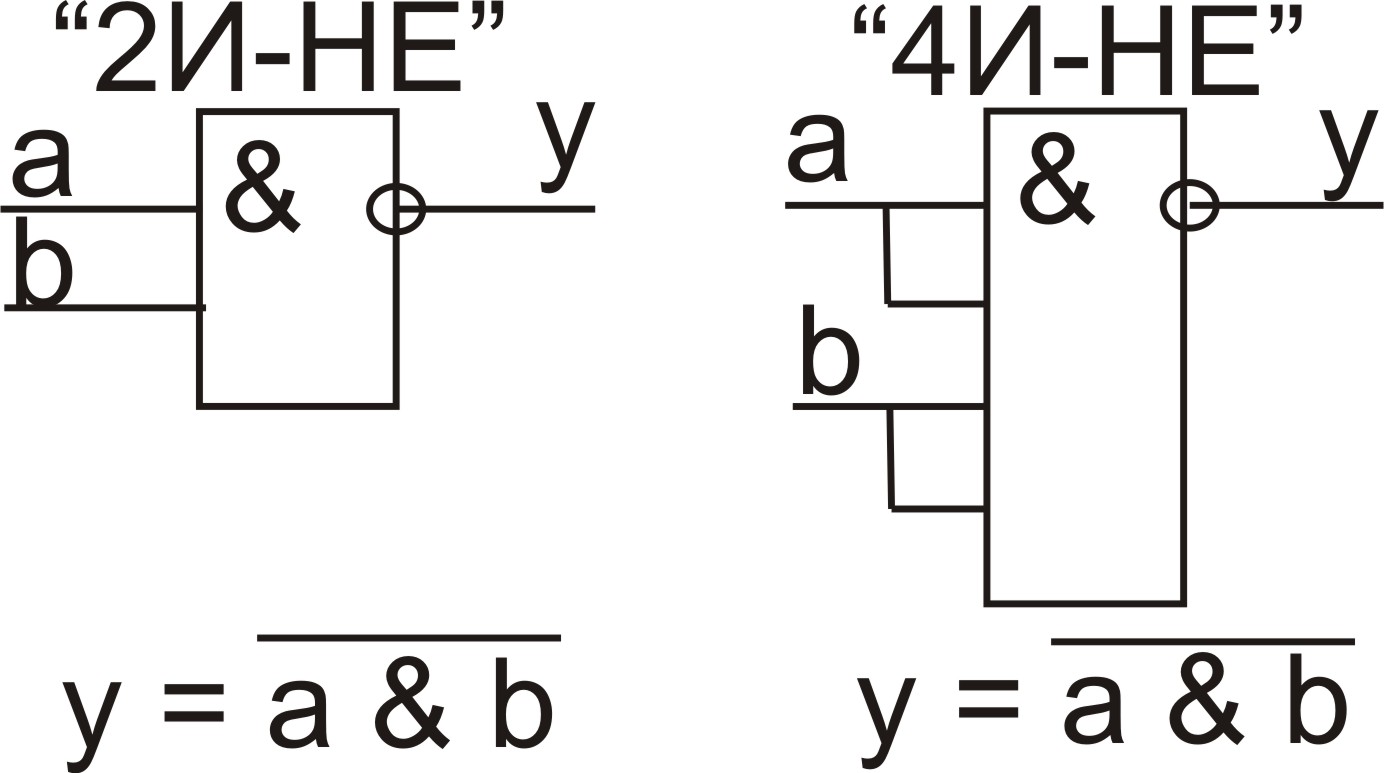

3. Инверсия логического умножения («И-НЕ»)

y

=

|

a

b

y

0

0

1

0

1

1

1

0

1

1

1

0 |

|

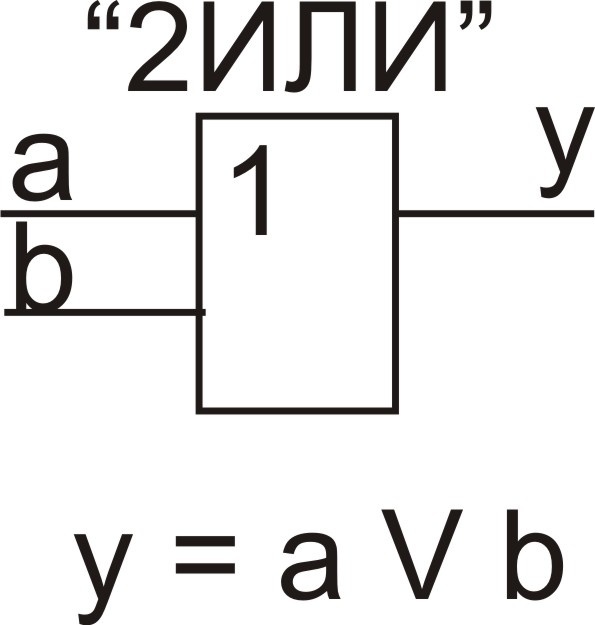

4. Логическое сложение («ИЛИ», дизъюнкция, OR)

y = a v b

|

a

b

y

0

0

0

0

1

1

1

0

1

1

1

1 |

|

Свойства:

1) a v 0 = a; 2) a v 1 = 1; 3) a v a v…v a = a; 4) a v = 1

5. Инверсия логического сложения («ИЛИ-НЕ», функция Пирса)

y

=

|

a

b

y

0

0

1

0

1

0

1

0

0

1

1

0 |

|