- •Конспект лекций

- •1. Уровни детализации представления эвм

- •2. Основы булевой алгебры

- •6. Функция запрет по x1.

- •8. Функция неравнозначности (сумма по модулю 2, исключающее «или», xor)

- •9) Функция равнозначности (инверсия суммы по модулю 2)

- •3. Теоремы булевой алгебры

- •4. Синтез комбинационных логических схем в базисе с ограничениями

- •5. Дешифратор.

- •5.1 Синтез полного дешифратора.

- •5.2 Синтез неполного дешифратора.

- •6. Мультиплексор

- •7. Реализация функций на дешифраторах и мультиплексорах.

- •8. Элементы памяти. Триггерные схемы.

- •8.1 Асинхронный rs триггер (простейшая ячейка памяти)

- •8.2 Асинхронный триггер (базовая ячейка памяти)

- •8.3 Синхронный rs триггер.

- •8.4 Синхронный d триггер.

- •9. Регистры

- •9.1 Синтез параллельного статического регистра.

- •9.2 Синтез регистра для приема с нескольких направлений.

- •10. Счетчики

- •10.1 Синтез счетчиков с последовательным переносом

- •10.2 Синтез счетчиков с параллельным переносом.

- •11. Канонический синтез цифровых автоматов.

- •12. Структурный автомат.

- •13. Синтез управляющих автоматов

- •13.1 Уа Мура

- •13.2 Уа Мили

- •14. Шины.

- •15. Схемы сравнения

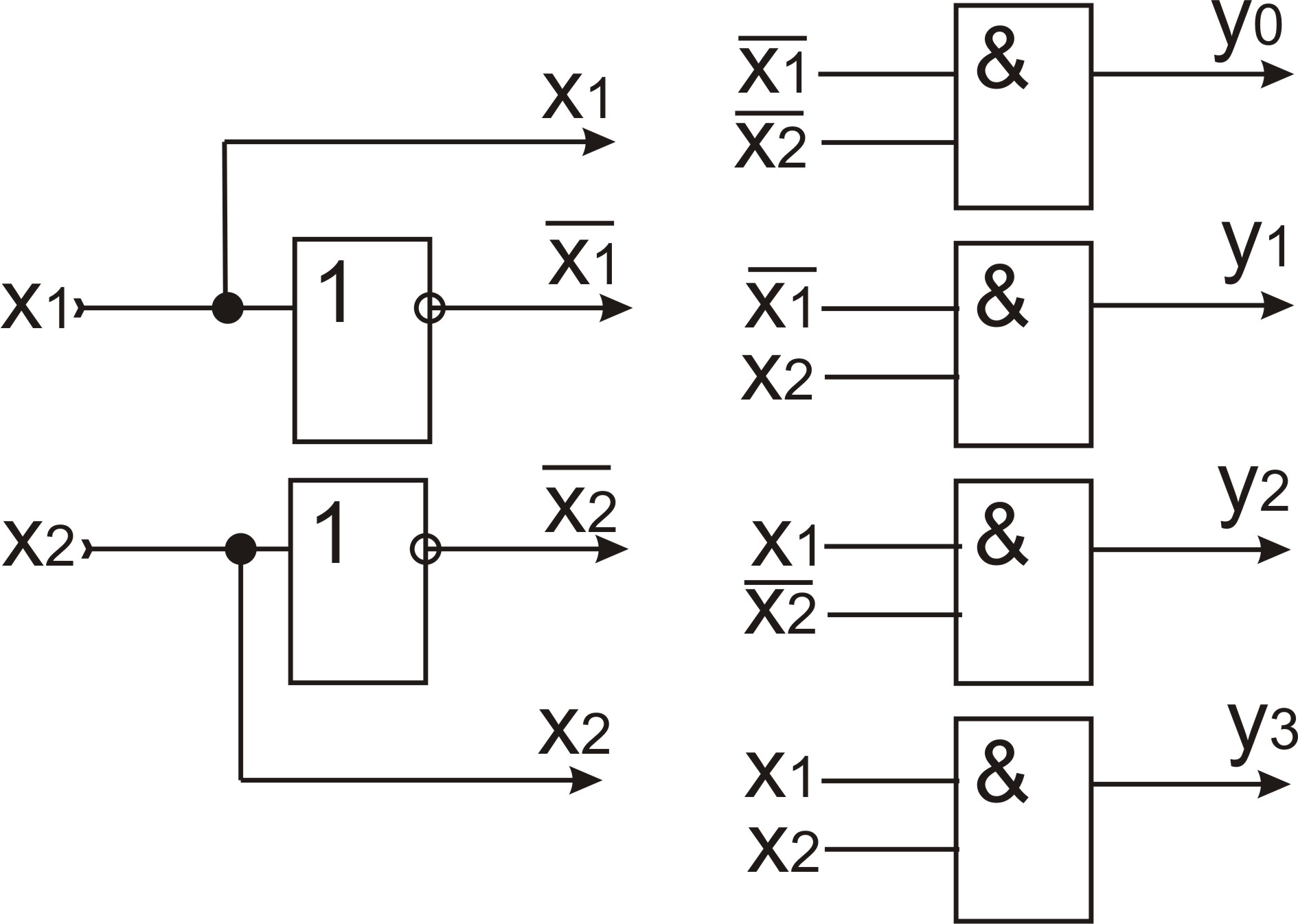

5.1 Синтез полного дешифратора.

Условное графическое обозначение, соответственно справочникам:

Старший бит (в примере Х1) подается на вход с большим весом (вход 2), а младший бит соответственно на вход с меньшим весом. Таблица истинности:

X1 |

X2 |

Y0 |

Y1 |

Y2 |

Y3 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

Для синтеза комбинационной схемы устройства нужно записать формулы выходных сигналов y0-y3, по таблице истинности в форме ДНФ, т.к. выходы дешифратора прямые:

![]()

![]()

![]()

![]()

Логическая схема дешифратора DC 24:

5.2 Синтез неполного дешифратора.

Для реализации неполного дешифратора:

Можно взять стандартную микросхему полного DC и использовать необходимое количество выходов. Но такое решение является избыточным.

Можно синтезировать неполный DC, как комбинационнцю схему с минимизацией аппаратных затрат.

Пример. Синтезировать DC 35

Таблица истинности:

X1 |

X2 |

X3 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

* |

* |

* |

* |

* |

1 |

1 |

0 |

* |

* |

* |

* |

* |

1 |

1 |

1 |

* |

* |

* |

* |

* |

В таблице имеется неопределенность (*), которая дает возможность минимизации выходных функций y0-y4.

В общем случае для каждой функции необходима своя карта Карно, но в данном случае каждая функция активна только на единственно соответствующем ей наборе сигналов x1, x2, x3, поэтому составим одну общую карту Карно, в которой вместо единиц укажем соответствующие функции yi.

Склеивать разные функции нельзя. Можно использовать только *.

Из карты Карно получили следующие формулы:

![]()

![]()

![]()

![]()

![]()

Логическая схема данного дешифратора имеет вид:

Сравним цену по кванту в случае использования полного DC и комбинационной схемы неполного DC.

Для полного: СКВ = 3*2 + 3*8 = 30 входов

Для КС неполного DC:

СКВ = 3*2 + 3 + 3*2 = 15 входов

Вывод: Очевидно, цена по кванту минимизированной схемы неполного DC 35 дает эффект 50%.