- •Конспект лекций

- •1. Уровни детализации представления эвм

- •2. Основы булевой алгебры

- •6. Функция запрет по x1.

- •8. Функция неравнозначности (сумма по модулю 2, исключающее «или», xor)

- •9) Функция равнозначности (инверсия суммы по модулю 2)

- •3. Теоремы булевой алгебры

- •4. Синтез комбинационных логических схем в базисе с ограничениями

- •5. Дешифратор.

- •5.1 Синтез полного дешифратора.

- •5.2 Синтез неполного дешифратора.

- •6. Мультиплексор

- •7. Реализация функций на дешифраторах и мультиплексорах.

- •8. Элементы памяти. Триггерные схемы.

- •8.1 Асинхронный rs триггер (простейшая ячейка памяти)

- •8.2 Асинхронный триггер (базовая ячейка памяти)

- •8.3 Синхронный rs триггер.

- •8.4 Синхронный d триггер.

- •9. Регистры

- •9.1 Синтез параллельного статического регистра.

- •9.2 Синтез регистра для приема с нескольких направлений.

- •10. Счетчики

- •10.1 Синтез счетчиков с последовательным переносом

- •10.2 Синтез счетчиков с параллельным переносом.

- •11. Канонический синтез цифровых автоматов.

- •12. Структурный автомат.

- •13. Синтез управляющих автоматов

- •13.1 Уа Мура

- •13.2 Уа Мили

- •14. Шины.

- •15. Схемы сравнения

6. Мультиплексор

Мультиплексор – устройство для передачи информации с одного из нескольких входов на единственный выход.

Вход, с которого принимается информация выбирается по адресу, который задается на специальных адресных входах мультиплексора.

Логическое обозначение мультиплексора:

Формула выходной функции y:

![]()

Внутренняя схема мультиплексора на основе полученной формулы:

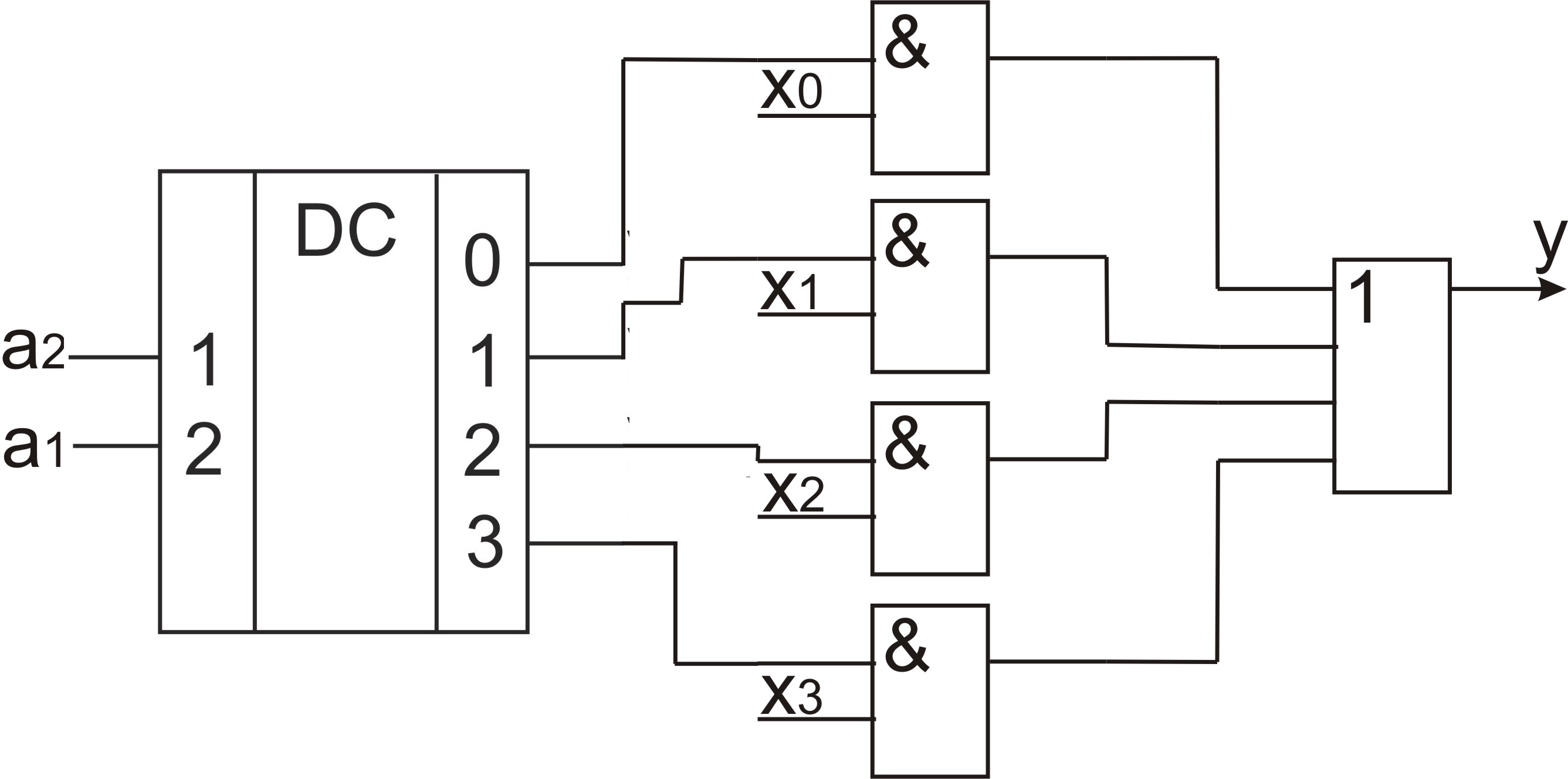

Схема мультиплексора на базе дешифратора.

Пример мультиплексора с управляющим входом выборки – MUX 8 1

![]()

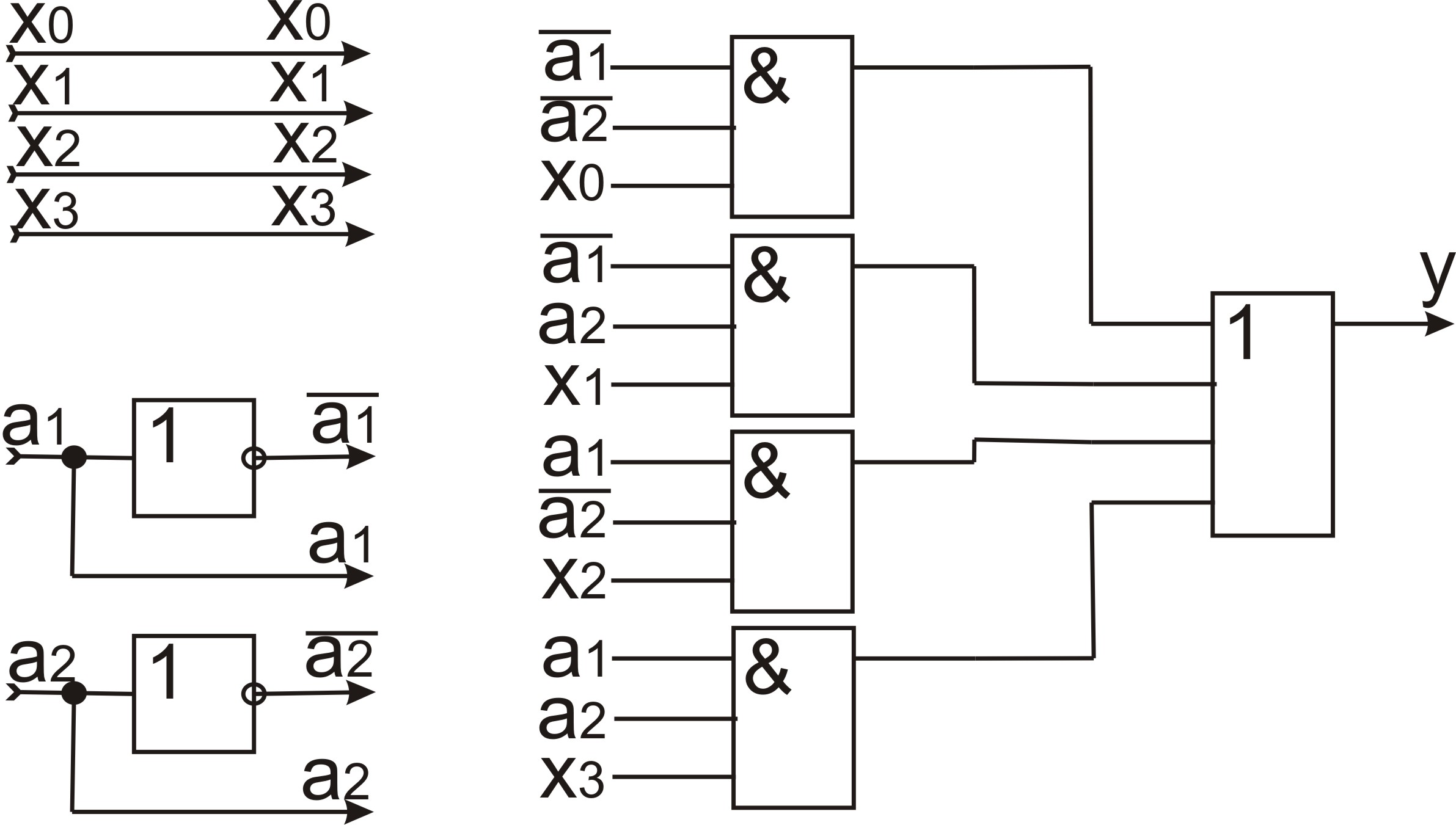

7. Реализация функций на дешифраторах и мультиплексорах.

Так как дешифраторы и мультиплексоры являются комбинационными схемами, их можно использовать для реализации булевых функций и их схем. При этом DC и MUX можно использовать как отдельно, так и в комбинации.

Пример 1 – Реализация СБФ на одном дешифраторе (тривиально)

Пусть СБФ задана таблицей истинности:

a |

b |

c |

y1 |

y2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

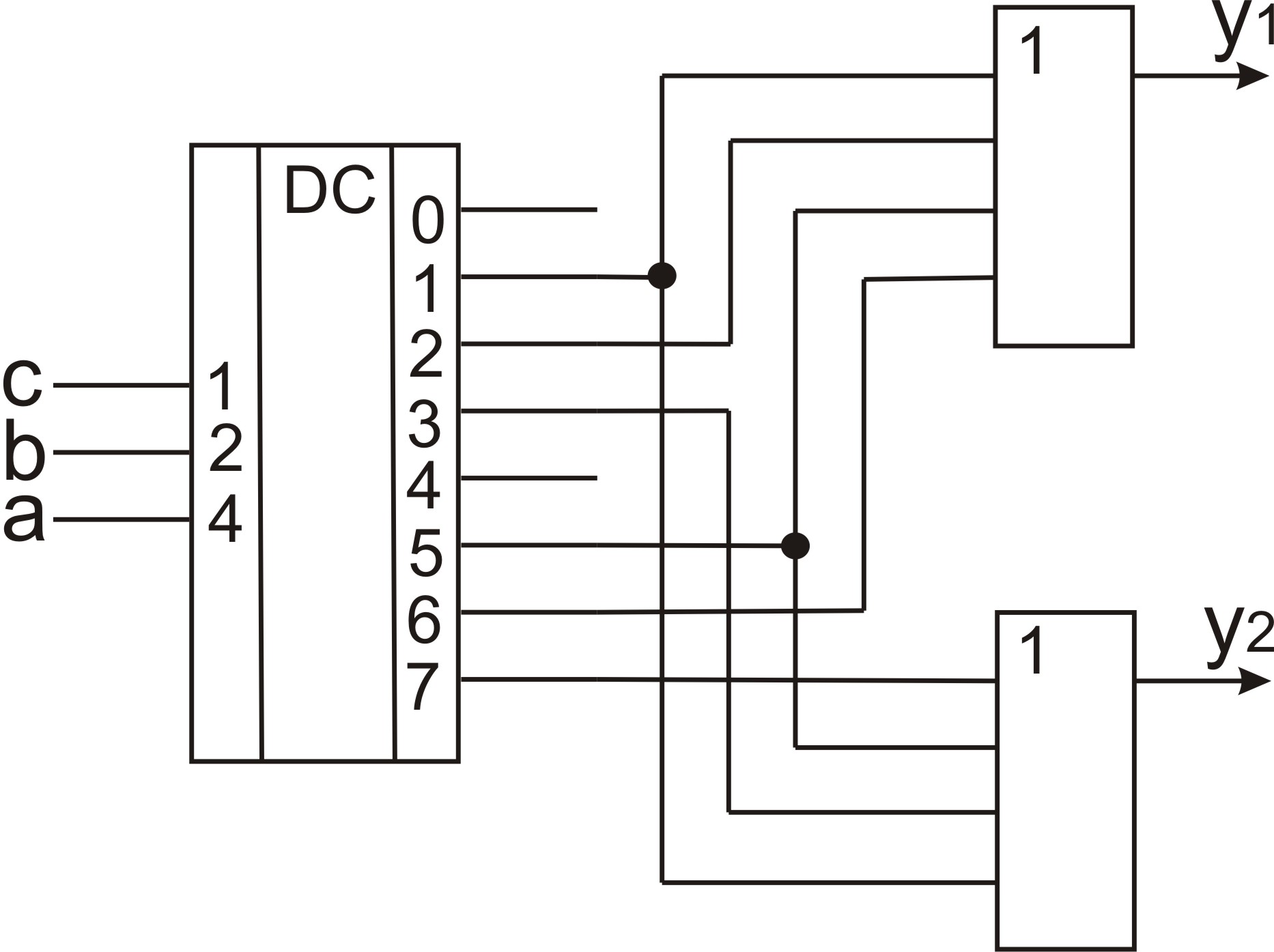

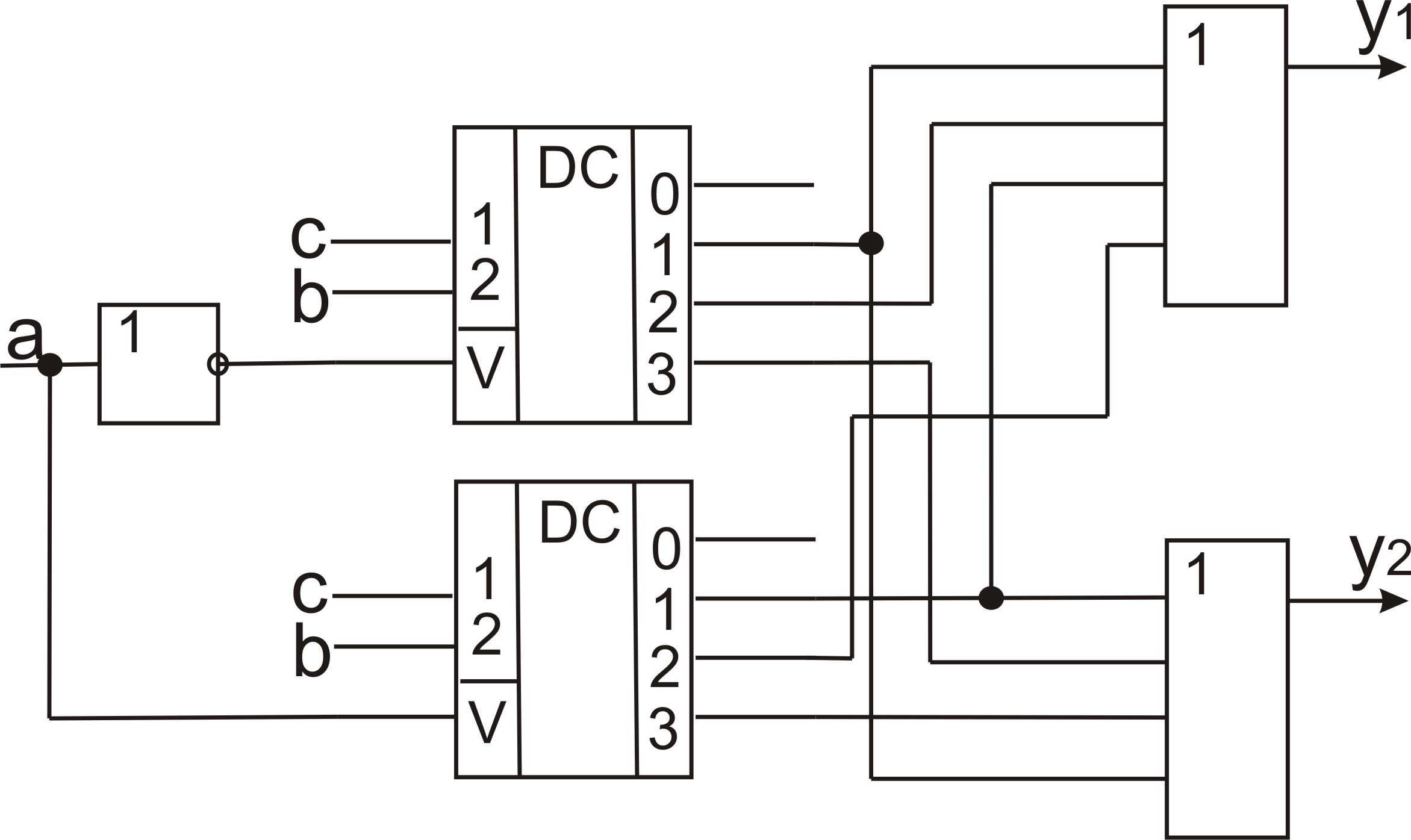

Пример 2 – Реализовать на DC 24 функцию от 3х переменных y=f (a,b,c),

Используя таблицу из предыдущего примера.

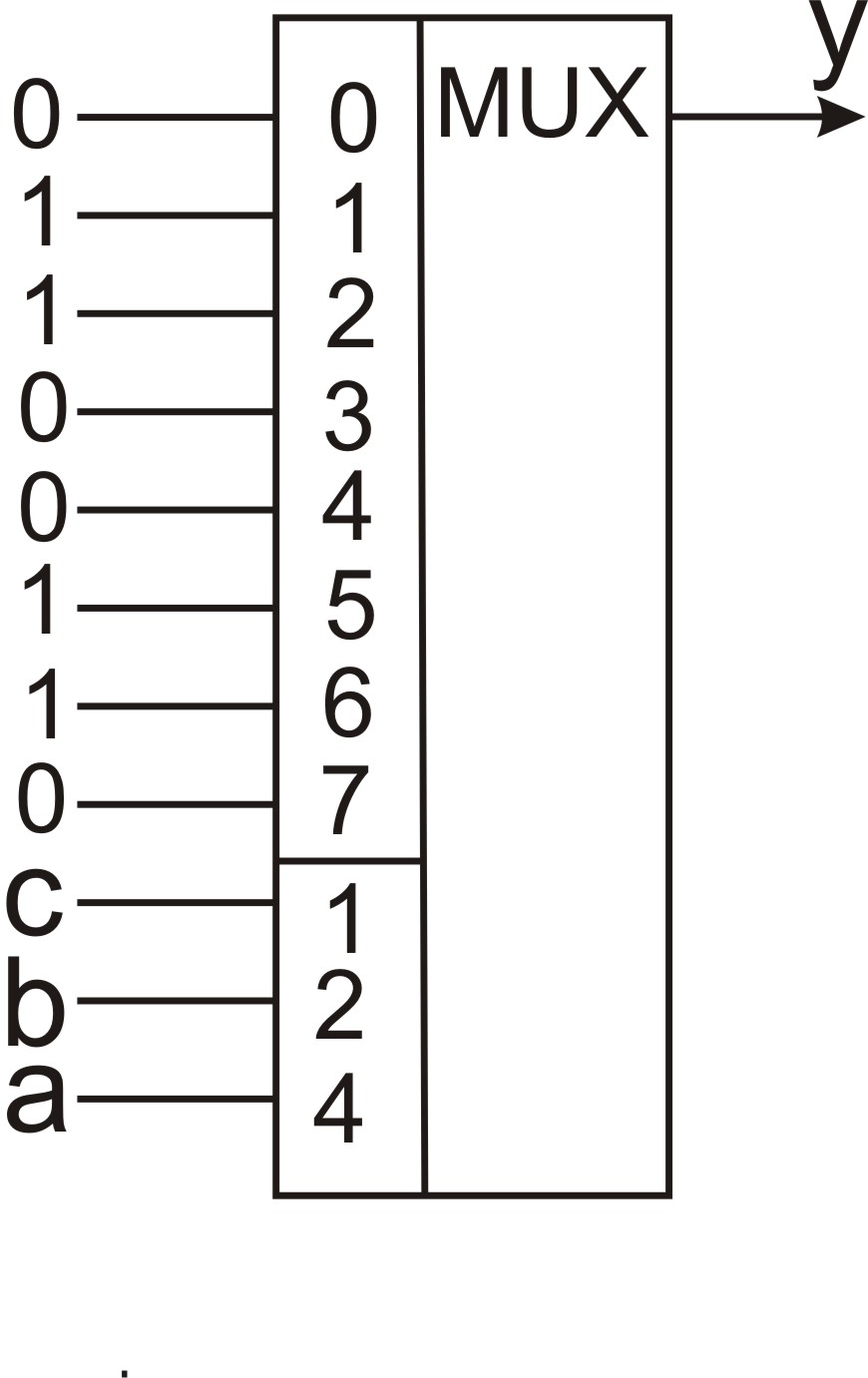

Пример 3 – Реализовать функцию y на мультиплексоре (тривиально).

Функция задана таблицей истинности:

a |

b |

c |

y |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

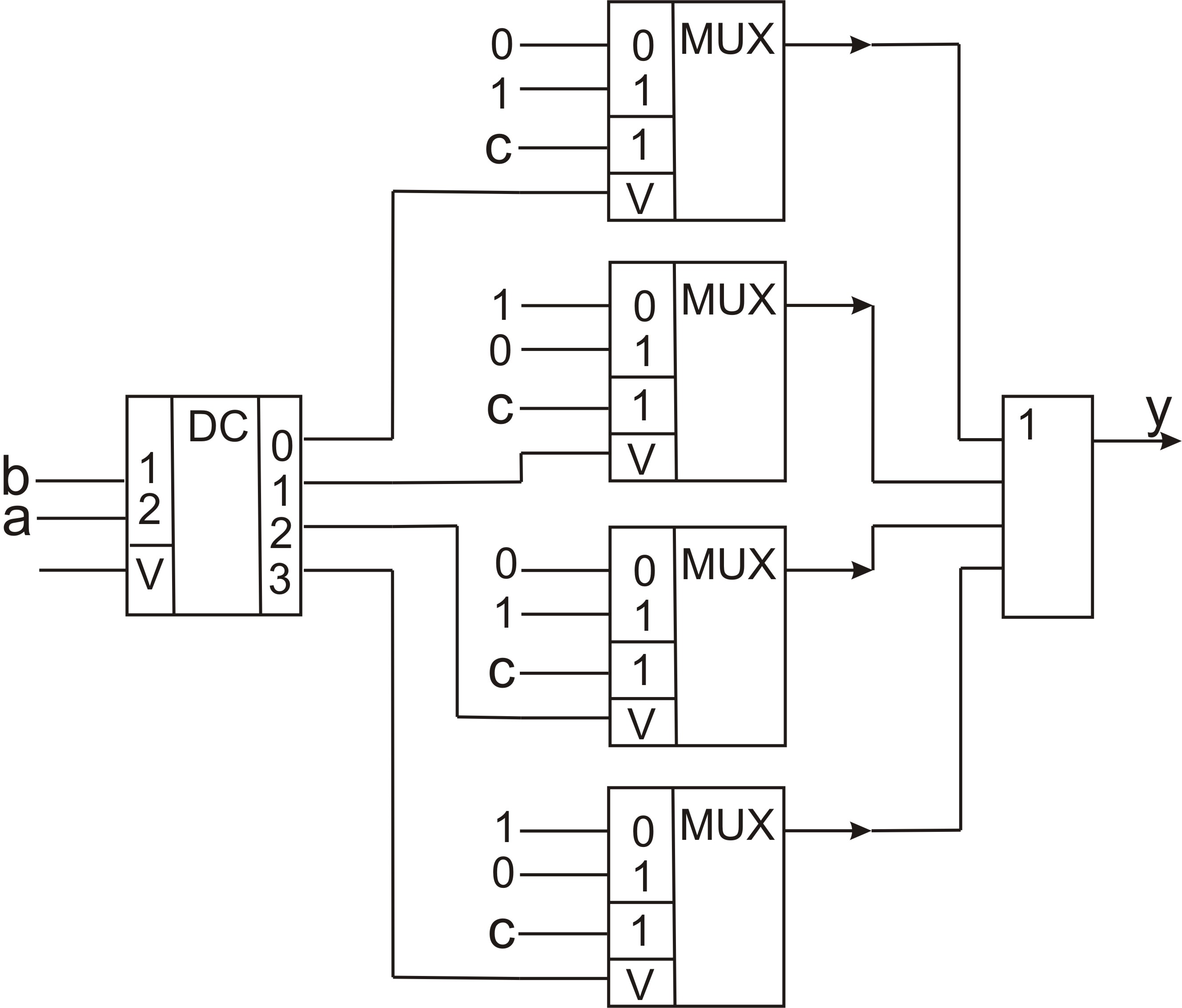

Логическая схема имеет вид:

Для тривиальной реализации функции на мультиплексоре достаточно, чтобы число адресных входов совпадало с числом аргументов функции.

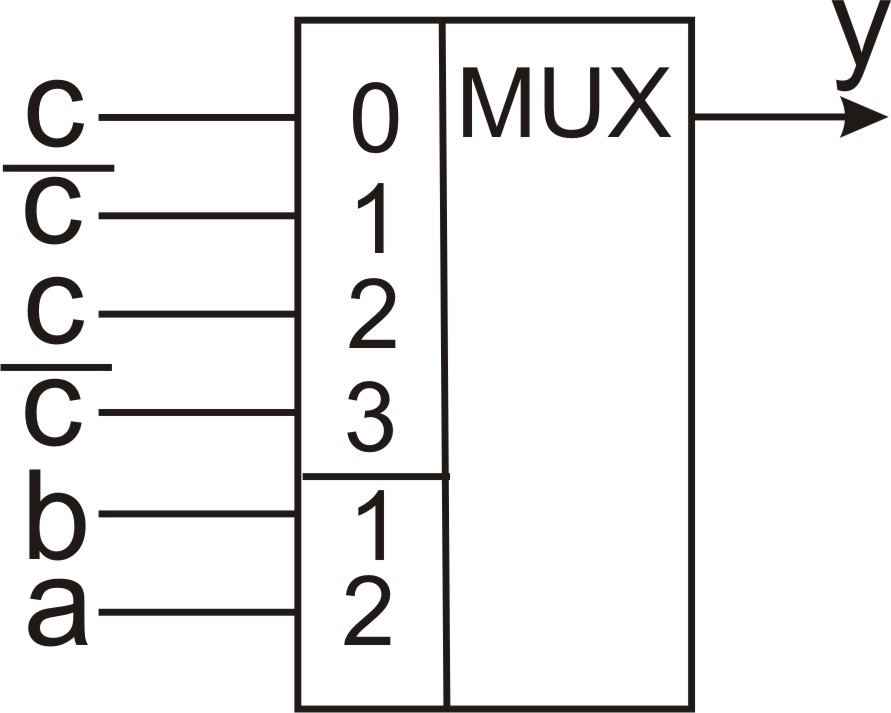

Пример 4 – Реализовать СБФ на мультиплексорах, если число аргументов функции больше на 1, чем число адресных входов мультиплексора.

Таблица истинности из предыдущего примера. Мультиплексор возьмем 4->1.

Для решения задачи добавим в таблицу столбец y' и сравним его со значением младшего бита (с) в каждой паре строк.

Таблица истинности:

a |

b |

c |

y |

y' |

0 |

0 |

0 |

0 |

c |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

c |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

Получены четыре значения y' , которые из преобразованной таблице переносятся на входы мультиплексора, при этом для адреса используются старшие биты (a,b).

Логическая схема имеет вид:

Для случаев, когда разница между числом аргументов функции и числом адресов мультиплексора составляет два бита и более, применяются схемы с каскадным соединением элементов, а также комбинированные схемы из дешифраторов и мультиплексоров.

Например, MUX 2 1