- •Конспект лекций

- •1. Уровни детализации представления эвм

- •2. Основы булевой алгебры

- •6. Функция запрет по x1.

- •8. Функция неравнозначности (сумма по модулю 2, исключающее «или», xor)

- •9) Функция равнозначности (инверсия суммы по модулю 2)

- •3. Теоремы булевой алгебры

- •4. Синтез комбинационных логических схем в базисе с ограничениями

- •5. Дешифратор.

- •5.1 Синтез полного дешифратора.

- •5.2 Синтез неполного дешифратора.

- •6. Мультиплексор

- •7. Реализация функций на дешифраторах и мультиплексорах.

- •8. Элементы памяти. Триггерные схемы.

- •8.1 Асинхронный rs триггер (простейшая ячейка памяти)

- •8.2 Асинхронный триггер (базовая ячейка памяти)

- •8.3 Синхронный rs триггер.

- •8.4 Синхронный d триггер.

- •9. Регистры

- •9.1 Синтез параллельного статического регистра.

- •9.2 Синтез регистра для приема с нескольких направлений.

- •10. Счетчики

- •10.1 Синтез счетчиков с последовательным переносом

- •10.2 Синтез счетчиков с параллельным переносом.

- •11. Канонический синтез цифровых автоматов.

- •12. Структурный автомат.

- •13. Синтез управляющих автоматов

- •13.1 Уа Мура

- •13.2 Уа Мили

- •14. Шины.

- •15. Схемы сравнения

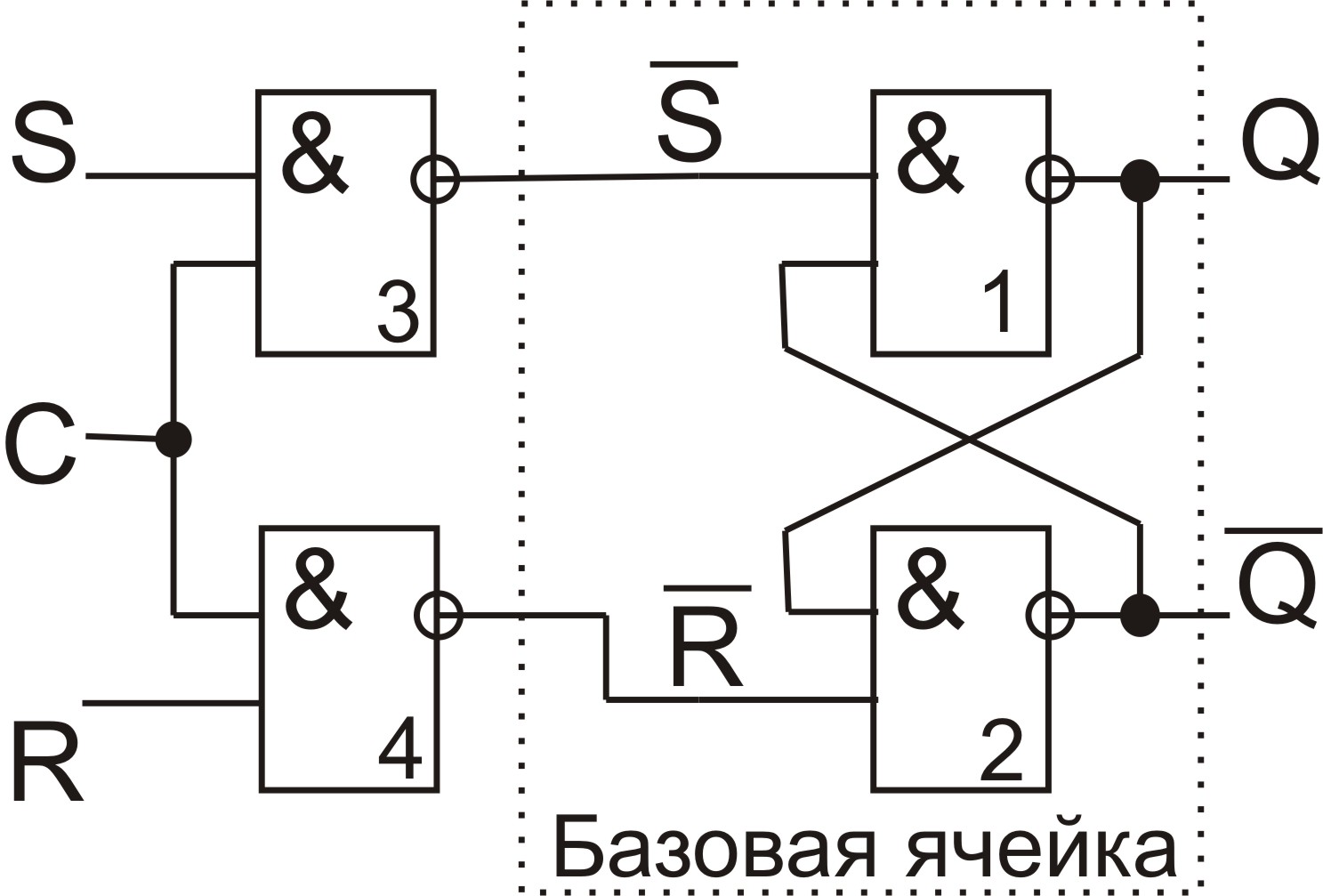

8.2 Асинхронный триггер (базовая ячейка памяти)

Исследуем схему с обратной связью, построенную на двух элементах «2И-НЕ». Анализ выполним используя таблицу истинности.

Таблица истинности (прямая таблица переходов триггера):

x1

( |

x2

( |

Qt |

Qt+1 |

Сост |

0 |

0 |

0 |

* |

Запр. комбинация |

0 |

0 |

1 |

* |

|

0 |

1 |

0 |

1 |

Set |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

Reset |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

Save |

1 |

1 |

1 |

1 |

Для функции «И» активный уровень – «0», а пассивный – «1».

1) x1=x2=0: – запрещенная комбинация.

2) x1=0, x2=1.

![]() ->

->

![]() ,

Set.

,

Set.

3) x1=1,

x2=0

.![]() ->

->

![]() ,

Reset.

,

Reset.

4) x1=x2=1:

![]() .

.

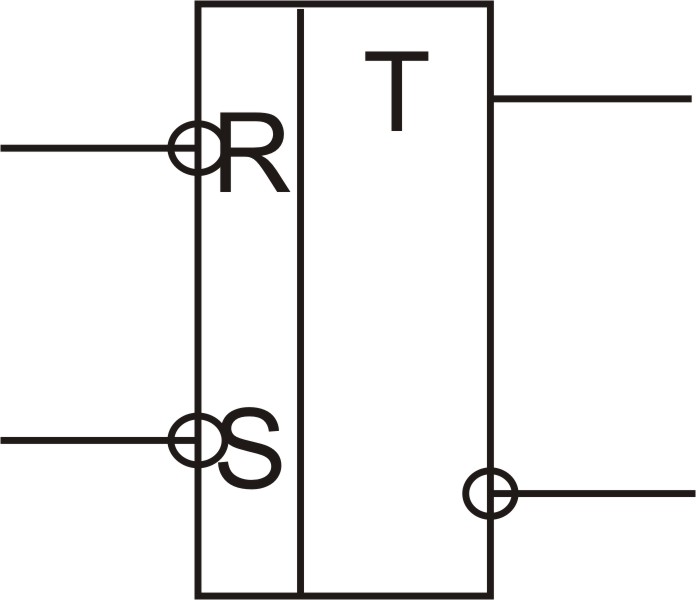

Условное графическое обозначение

асинхронного

![]() триггера:

триггера:

Инверсии на входах обозначаю то, что триггеры управляются нулем.

Вывод: Данная схема соответствует одноступенчатому асинхронному RS триггеру с инверсным управлением ( - триггер). Эта схема является базовой, для построения схем других типов.

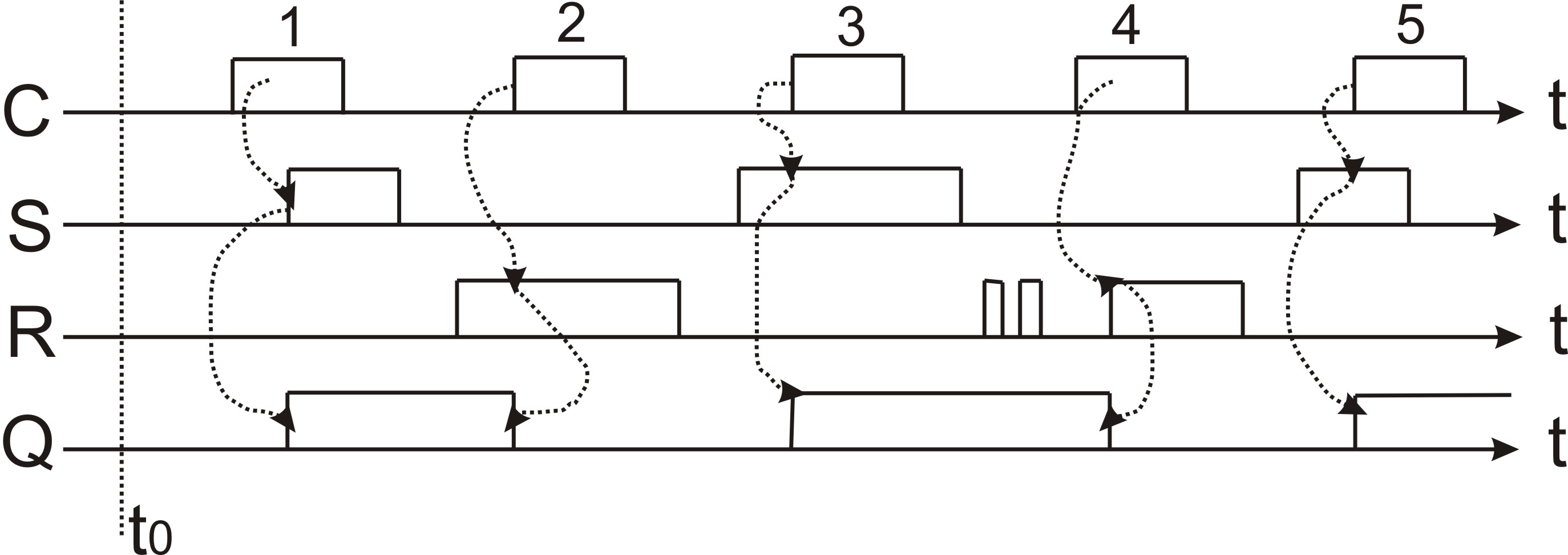

8.3 Синхронный rs триггер.

Как видно из временной диаграммы асинхронного триггера, любое изменение сигнала на входе может повлечь за собой изменение сигнала на выходе.

Чтобы избежать реакции устройства на любые входные сигналы, в т.ч. на некорректные комбинации, добавим в схему специальный разрешающий сигнал «C» “Clock”.

Сигнал «С» представляет собой серию импульсов одинаковой длительности, поступающих с одинаковым промежутком (паузой). Пауза синхроимпульса должна быть дольше его длительности. Для того чтобы успели сформироваться оба управляющих сигнала на входе R и S.

Для этой схемы активный уровень – «1», пассивный – «0».

Таблица истинности:

С |

S |

R |

Qt+1 |

Сост |

0 |

* |

* |

Qt |

Save |

1 |

0 |

0 |

Qt |

Save |

1 |

0 |

1 |

0 |

Reset |

1 |

1 |

0 |

1 |

Set |

1 |

1 |

1 |

* |

Запр. комбинация |

Сигнал «С» задает один из двух режимов работы:

1) С=0. Устройство находится в режиме хранения, его состояние не зависит от внешних входов R и S.(режим хранения).

2) С=1. Разрешается реакция устройства на изменение сигналов R и S(режим переключения).

Временная диаграмма:

Для обеспечения корректной работы устройства необходимо, чтобы управляющие сигналы на входах R и S оставались неизменны в течении импульса С.

В данной диаграмме только две корректные ситуации на импульсе 2 и 3.