- •1 .Параллельный регистр на rs-триггерах.

- •2. Параллельный регистр на d-триггерах.

- •3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

- •4. Сдвигающий регистр.

- •5. Организация межрегистровых связей

- •6. Основные параметры и классификация счетчиков

- •8. Вычитающий счетчик с последовательным переносом на т-триггерах

- •Реверсивный счетчик на т-триггерах.

- •10.Счетчик с параллельным переносом на т-триггерах.

- •11. Структура счетчика с комбинированным переносом.

- •12. Счетчик со сквозным переносом на т-триггерах.

- •13. Двоично-кодированные счетчики на т-триггерах.

- •14. Кольцевой счетчик на т-триггерах.

- •15.Мультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •16. Схема мультиплексорного дерева

- •17. Демультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •18.Схема демультиплексорного дерева

- •1 9. Преобразователи кодов.

- •Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •22.Реализация демультиплексора с использованием дешифратора.

- •23 Реализация мультиплексора с использованием дешифратора.

- •Многоступенчатый дешифратор.

- •25. Полный двоичный дешифратор на базе двух двоично–десятичных де-шифраторов.

- •26. Цифровой компаратор. Таблица истинности. Математическое описание. Принципиальная схема

- •27. Счетчики в коде Грея

- •1. Счетчики в коде «1 из n»

- •3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

- •4. Счетчик Джонсона.

- •5.Полиномиальные счетчики.

- •6. Схемы генераторов псевдослучайной последовательности (гпсп).

- •7. Арифметико-логические устройства (алу). Назначение и основные параметры.

- •8. Сумматоры. Алгоритм двоичного сложения.

- •9. Сумматоры. Сложение многоразрядных двоичных кодов.

- •11. Одноразрядный сумматор

- •12. Многоразрядный сумматор параллельного действия.

- •13. Многоразрядный сумматор последовательного действия.

- •14. Сумматор с параллельным переносом.

- •15.Сумматоры с цепным переносом.

- •16.Выполнение операций арифметического умножения.

- •17.Классификация запоминающих устройств.

- •18.Структура озу типа 2d.

- •19.Структура озу типа 3d.

- •20.Структура озу типа 2dm.

- •Запоминающие устройства типа

- •21.Масочные запоминающие устройства.

- •22.Матрица моп- транзисторных элементов зу.

- •23.Запоминающие устройства типа prom.

- •24/25.Запоминающие устройства типа eprom eeprom.

- •26.Статистические озу (sram).

- •27.Динамические озу(dram).

- •Запоминающие элементы

- •Основные сведения. Система параметров. Классификация

- •Параметры зу

- •Параметры зу

8. Вычитающий счетчик с последовательным переносом на т-триггерах

Счетчиком называется последовательное устройство, предназначенное для счета входных импульсов и фиксации числа в двоичном коде.

По направлению счета счетчики подразделяют на:

-суммирующие (выполняют микрооперацию инкремента над хранящимся кодовым словом);

-вычитающие (выполняют микрооперацию декремента над хранящимся кодовым словом);

-реверсивные (выполняют либо микроопер. инкремента, либо декремента в зависимости от значения управляющего сигнала);

Получим счетчик с модулем счета М=8, для этого нам понадобится 3 триггера. Таблица переключений будет иметь следующий вид:

C |

Q2 |

Q1 |

Q0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

![]() -

с приходом каждого 4 имп. синх. Данный

алгоритм легко реализовать используя

асинхронные Т-триггеры. При этом

синхронизацию каждого последующего

триггера осуществляют выходным сигналом

предыдущего, а переключение первого

триггера, который формирует значение

-

последовательностью синхроимпульсов.

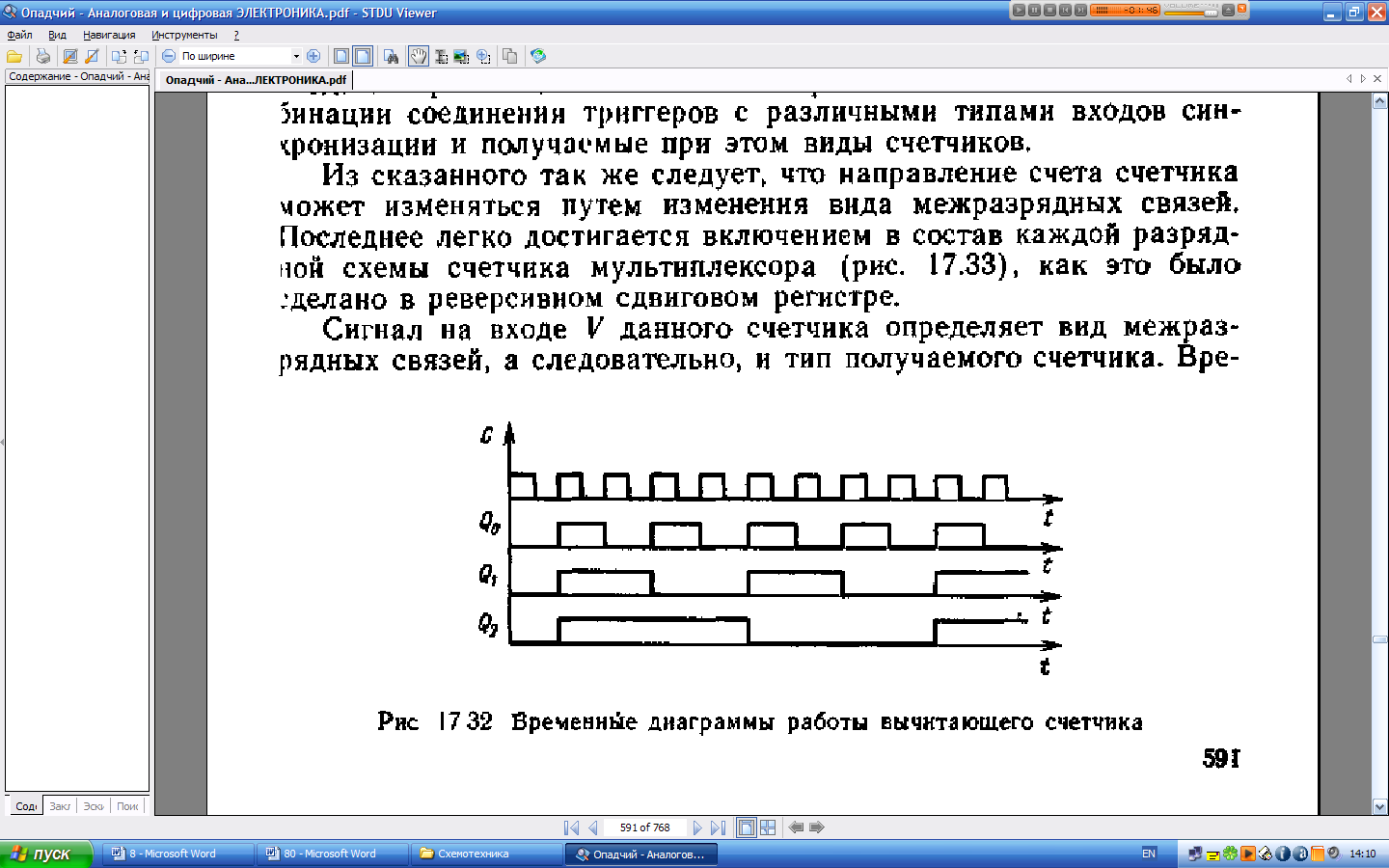

Временные диаграммы приведены ниже:

-

с приходом каждого 4 имп. синх. Данный

алгоритм легко реализовать используя

асинхронные Т-триггеры. При этом

синхронизацию каждого последующего

триггера осуществляют выходным сигналом

предыдущего, а переключение первого

триггера, который формирует значение

-

последовательностью синхроимпульсов.

Временные диаграммы приведены ниже:

И з

таблицы и временных диаграмм следует,

что для организации микрооперации

декремента переключение триггера должно

происходить в момент изменения выходного

сигнала предыдущего триггера из 0 в 1.

Следовательно, для получения вычитающего

счетчика последовательно включенные

асинхронные Т-триггеры должны быть

снабжены прямыми динамическими входами.

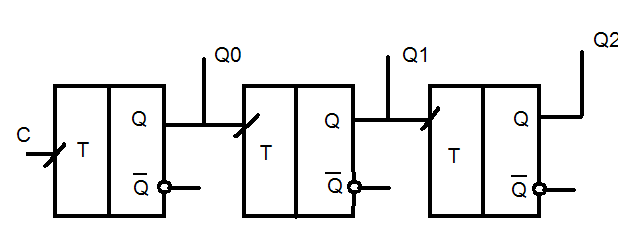

Схема счетчика приведена ниже:

з

таблицы и временных диаграмм следует,

что для организации микрооперации

декремента переключение триггера должно

происходить в момент изменения выходного

сигнала предыдущего триггера из 0 в 1.

Следовательно, для получения вычитающего

счетчика последовательно включенные

асинхронные Т-триггеры должны быть

снабжены прямыми динамическими входами.

Схема счетчика приведена ниже:

С казанное

справедливо, если для синхронизации

каждого последующего асинхронного

Т-триггера использовать прямой выход

предыдущего триггера. Если для этой

цели использовать инверсных выход

триггера, то вычитающий счетчик

реализуется на Т-триггерах с инверсными

динамическими входами.

казанное

справедливо, если для синхронизации

каждого последующего асинхронного

Т-триггера использовать прямой выход

предыдущего триггера. Если для этой

цели использовать инверсных выход

триггера, то вычитающий счетчик

реализуется на Т-триггерах с инверсными

динамическими входами.

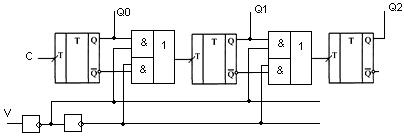

Реверсивный счетчик на т-триггерах.

Счетчик – это последовательное устройство предназначенное для счета входных импульсов и фиксации их числа в двоичном коде. Строятся на N однотипных связанных между собой разрядных схем, каждая из этих схем в общем случае состоит из триггера и комбинационной схемы, для формирования управляющих сигналов.

За счет изменения вида межразрядных связей можно получить как суммирующий счетчик так и вычитающий. Такой счетчик называется реверсивный.

С хема

реверсивного счётчика. Вход V задает

вид межразрядных связей, а значит и тип

счетчика. При V=0 вычитающий, при V=1 –

суммирующий.

хема

реверсивного счётчика. Вход V задает

вид межразрядных связей, а значит и тип

счетчика. При V=0 вычитающий, при V=1 –

суммирующий.

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

T+1 |

|

||||||

V |

Q2 |

Q1 |

Q0 |

Q2 |

Q1 |

Q0 |

|||

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|||

1 |

0 |

0 |

1 |

0 |

1 |

0 |

|||

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|||

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|||

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|||

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|||

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|||

0 |

1 |

1 |

1 |

1 |

1 |

0 |

|||

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|||

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|||

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|||

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|||

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|||

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|||