- •«Национальный исследовательский

- •I. Основы АнАлоговой электроники

- •1. Задачи, решаемые электронной техникой, и элементы, необходимые для их решения

- •1.1. Электрические сигналы. Временное и спектральное представление

- •1.2. Усиление электрических сигналов

- •1.3. Модуляция сигналов

- •1.3.1. Амплитудная модуляция

- •1.3.2. Импульсно-кодовая модуляция

- •1.3.3. Широтно-импульсная модуляция

- •А б Рис. 1.19. Компаратор: а – схема; б – временные диаграммы при шим1.4. Фильтрация сигналов

- •1.5. Хранение и отображение информации

- •1.6. Преобразование электрической энергии

- •Контрольные вопросы и задания

- •Основные результаты первой главы

- •2. Математический аппарат описания электронных элементов

- •2.1. Описание нелинейных элементов

- •2.2. Линеаризация нелинейных уравнений

- •2.3. Частотный анализ линеаризованных цепей

- •2.4. Временной анализ линеаризованных цепей

- •Контрольные вопросы и задания

- •Основные результаты второй главы

- •3. Полупроводники – основа современной элементной базы электроники

- •3.1. Преимущества полупроводниковых элементов перед электровакуумными

- •3.2. Физические основы электропроводности полупроводников

- •3.3. Электропроводность беспримесного (собственного) полупроводника

- •3.4. Электропроводность примесных полупроводников

- •3.4.1. Донорная примесь

- •3.4.2. Акцепторная примесь

- •3.6. Инерционностьp-n-перехода

- •3.6.1. Зарядная емкостьp-n-перехода

- •3.6.2. Диффузионная емкость

- •3.7. Пробой p-n-перехода

- •3.7.1. Тепловой пробой

- •3.7.2. Электрический пробой

- •3.8. Математическая модельp-n-перехода

- •3.9. Переходметалл – полупроводник

- •Контрольные вопросы и задания

- •Основные результаты третьей главы

- •4. Многопереходные электронные элементы

- •4.1. Полупроводниковые триоды (биполярные транзисторы)

- •4.2. Активный режим работы биполярного транзистора

- •4.3. Статические характеристики биполярного транзистора для активного режима

- •4.4. Инерционность биполярного транзистора

- •4.5. Пробой коллекторного перехода

- •4.7. Нелинейная модель биполярного транзистора

- •4.8. Линеаризованная модель биполярного транзистора

- •4.9. Ключевой режим биполярного транзистора

- •4.10. Полевые транзисторы

- •4.11. Полевые транзисторы с управляющимp-n-переходом

- •4.12. Полевые транзисторы с изолированным затвором

- •4.13. Ключевой режим работы полевых транзисторов

- •4.14. Тиристоры

- •4.15. Элементы оптоэлектроники

- •4.15.1. Управляемые источники излучения

- •4.15.2. Фотоприемники

- •Контрольные вопросы и задания

- •Основные результаты четвертой главы

- •5. Основы теории электронных усилителей

- •5.1. Общие положения

- •Контрольные вопросы и задания

- •5.2. Обратная связь в усилительных устройствах

- •5.2.1. Влияние обратной связи на коэффициент усиления.

- •5.2.2. Влияние обратной связи на нестабильность усилителя

- •5.2.3. Влияние обратной связи на нелинейные искажения и шумы усилителя

- •5.2.4. Влияние обратной связи на входное и выходное сопротивления усилителя

- •5.2.5. Устойчивость усилителей с обратной связью

- •5.2.6. Коррекция частотных характеристик для обеспечения устойчивости усилителя

- •Контрольные вопросы и задания

- •5.3. Принципы построения усилительных каскадов

- •5.3.1. Цепи задания и стабилизации режима покоя

- •5.3.2. Элементы связи усилительных устройств

- •К Рис. 5.34. Оптическая связь онтрольные вопросы и задания

- •5.4. Операционные усилители

- •5.4.1. Модели оу

- •5.4.2. Масштабирующий инвертирующий усилитель

- •5.4.3. Масштабирующий неинвертирующий усилитель

- •5.4.4. Суммирующий усилитель

- •5.4.5. Вычитающий усилитель

- •5.4.6. Интегрирующий усилитель

- •5.4.7. Нелинейные функциональные преобразователи сигналов

- •Контрольные вопросы и задания

- •5.5. Усилители мощности

- •5.5.1. Линейные усилители мощности

- •5.5.2. Усилители мощности ключевого типа

- •Контрольные вопросы и задания

- •Основные результаты пятой главы

- •6. Автогенераторы

- •Основные результаты шестой главы

- •7. Источники вторичного электропитания электронных устройств

- •7.1. Классическая схема вторичного источника (без преобразования частоты сети)

- •7.2. Функциональные элементы вторичных источников электропитания

- •7.2.1. Преобразователи переменного напряжения

- •7.2.2. Стабилизаторы постоянного напряжения

- •7.3. Вторичные источники с преобразованием частоты сети

- •Vd Схема упр.

- •Vd Схема упр. Ul

- •Контрольные вопросы и задания

- •Основные результаты седьмой главы

- •II. Основы цифровой электроники

- •1. Введение

- •2. Логические функции

- •2.1. Логические функции и способы их представления

- •2.2. Основы алгебры логики

- •2.2.1. Функция не

- •2.2.2. Функция или

- •2.2.3. Функция и

- •2.3. Логические элементы и-не, или-не

- •2.3.1. Элемент и-не (штрих Шеффера)

- •2.3.2. Элемент или-не (стрелка Пирса)

- •2.4. Синтез логических устройств

- •2.5. Выбор системы логических элементов

- •2.6. Минимизация логических функций

- •Контрольные вопросы и задания

- •3. Характеристики и параметры логических элементов, основы схемотехники

- •3.1. Логические уровни, нагрузочная способность

- •3.2. Логические элементы с тремя состояниями

- •3.3. Быстродействие логических элементов

- •3.4. Помехоустойчивость логических элементов

- •3.5. Число входов логических элементов

- •3.6. Специальные типы логических элементов. Логические элементы с открытым коллектором

- •3.6.1. Расширители числа входов

- •3.6.2. Схема согласования уровней

- •3.6.3. Логический элемент с разрешением по входу

- •Контрольные вопросы и задания

- •4. Цифровые устройства комбинационного типа

- •4.1. Преобразователи кодов, шифраторы, дешифраторы

- •4.2. Мультиплексоры

- •4.3. Сумматоры

- •4.4. Цифровые компараторы

- •Контрольные вопросы и задания

- •5. Последовательностные цифровые устройства

- •5.1. Триггеры

- •5.1.5. Триггер Шмитта

- •5.2. Цифровые счетчики импульсов и делители частоты следования

- •5.2.1. Двоичные счетчики

- •5.2.2. Недвоичные счетчики

- •5.3. Регистры

- •Контрольные вопросы и задания

- •6. Генераторы импульСныхСигналов

- •6.1. Автогенераторы прямоугольных импульсов (мультивибраторы)

- •6.2. Ждущий (заторможенный) режим генераторов

- •6.3. Интегральные таймеры

- •6.4. Генераторы линейно изменяющегося напряжения (тока)

- •Контрольные вопросы и задания

- •7. УстройствасОпРяжЕнияцифровых и аналоговых систем

- •7.1. Цифроаналоговые преобразователи

- •7.2. Аналого-цифровые преобразователи

- •7.2.1. Ацп последовательного приближения

- •7.2.2. Ацп параллельного типа

- •7.2.3. Ацп интегрирующего типа

- •Контрольные вопросы и задания

- •8. Введение в микропроцессорную технику

- •8.1. Арифметическо-логические устройства

- •8.2. Полупроводниковые запоминающие устройства

- •8.3. Программируемые логические интегральные матрицы

- •8.4. Интерфейсные устройства

- •Контрольные вопросы и задания

- •Приложение справочные данные интегральных схем

- •Литература

- •Оглавление

7.2.1. Ацп последовательного приближения

АЦП последовательного приближения – это АЦП прямого преобразования со средним быстродействием: число временных тактов одного преобразования равно числу разрядов. Структурная схема такого АЦП изображена на рис. 7.20.

Рис. 7.20. Структурная схема АЦП последовательного приближения

Рассмотрим

принцип работы такого АЦП при трехразрядном

ЦАП, у которого при опорном напряжении

![]() аналоговая «цена» старшего разряда

составляет

аналоговая «цена» старшего разряда

составляет![]() ,

среднего разряда –

,

среднего разряда –![]() и младшего разряда –

и младшего разряда –![]() .

.

В

Рис. 7.21. Диаграмма

напряжений АЦП в процессе уравновешивания

методом последовательного

приближения

![]() .

ЕслиU(n)>

.

ЕслиU(n)>![]() ,

то компаратор устанавливает на выходе

1. Схема управления в следующем такте

выставит код 110 и напряжение

,

то компаратор устанавливает на выходе

1. Схема управления в следующем такте

выставит код 110 и напряжение![]() +

+![]() .

Если это напряжение окажется большеU(n),

то по уровню 0 компаратора схема управления

убирает 1 из среднего разряда и

устанавливает 1 в младший разряд, т. е.

код 101. Поскольку последний разряд

задействован, то на этом преобразовании

заканчивается и код 101, эквивалентный

значению U(n),

с ошибкой квантования

.

Если это напряжение окажется большеU(n),

то по уровню 0 компаратора схема управления

убирает 1 из среднего разряда и

устанавливает 1 в младший разряд, т. е.

код 101. Поскольку последний разряд

задействован, то на этом преобразовании

заканчивается и код 101, эквивалентный

значению U(n),

с ошибкой квантования

![]() ;

записывается в выходной регистр.

Аналогичные операции проводятся с

каждым дискретным значениемU(n);

рис. 7.21.

;

записывается в выходной регистр.

Аналогичные операции проводятся с

каждым дискретным значениемU(n);

рис. 7.21.

Потенциальная точность рассмотренного АЦП определяется дискретностью и линейностью ЦАП, а также чувствительностью к смещению нулевого уровня компаратора. Быстродействие ограничивается временем выполнения одного такта, т. е. быстродействием ЦАП и компаратора, и числом разрядов.

7.2.2. Ацп параллельного типа

В таком АЦП анализ уровня выборки сигнала U(n) проводится одновременно по всему диапазону. Это означает, что для n-разрядного кода, когда число квантованных уровней (без учета нулевого) равно 2n–1, для одновременного анализа потребуется 2n–1 компараторов, каждый из которых «следит» за своим уровнем, для чего он снабжается соответствующим опорным источником (см. рис. 7.22).

Очевидным преимуществом параллельного АЦП является максимальное быстродействие – преобразование осуществляется за один такт. Очевиден и недостаток – большие аппаратурные затраты. Так, например, для достаточно «грубого» шестиразрядного варианта потребуется 63 компаратора, каждый из которых представляет достаточно сложную микросхему. На практике могут применяться и некоторые комбинированные АЦП, когда, например, два параллельных АЦП оцифровывают m старших разрядов n-разрядного кода. Полученный код формирует на выходе ЦАП «грубое» значение выходного сигнала, разность же между входным и грубым сигналами оцифровывается вторым параллельным АЦП, формирующим n–m младших разрядов.

Рис.

7.22. Структурная схема двухразрядного

параллельного ЦАП,

состояние для

![]() <U(n)<

<U(n)<![]()

Основные ограничения потенциальной точности АЦП прямого преобразования определяются параметрами входящих в их структуру ЦАП и шумами входного сигнала, включая и паразитные электромагнитные помехи промышленной частоты.

7.2.3. Ацп интегрирующего типа

В этих преобразователях с помощью интегрирования сигнала и сравнения результата интегрирования с опорным напряжением осуществляется преобразование постоянного напряжения U(n) в пропорциональный временной интервал, длительность которого точно определяется путем подсчета импульсов калиброванной частоты, заполняющих данный отрезок времени. Если время интегрирования выбрать равным периоду сетевой гармонической помехи, интеграл от которой за период равен нулю, то произойдет ее глубокое подавление. Усреднение за этот же период интеграла от более высокочастотных помех также проводит к их практическому исключению. Отсутствие в составе интегрирующего преобразователя ЦАП и подавление шумов позволяет реализовать очень высокую разрядность, не доступную для АЦП прямого преобразования. Естественной платой за это преимущество является снижение быстродействия.

Рассмотрим принцип действия интегрирующих АЦП на примере АЦП двойного интегрирования (рис. 7.23).

а б

Рис. 7.23. АЦП двойного интегрирования:

а – структурная схема; б – диаграммы сигналов на выходе интегратора и генератора

Схема работает в два такта. В первом на вход интегратора на время Т0 подается измеряемое напряжение U(n) и конденсатор С заряжается до напряжения, равного

,

,

где 0 – постоянная интегрирования.

Во

втором такте вход интегратора переключается

на опорное напряжение

![]() ,

имеющее противоположный входному

напряжению знак, – начинается разряд

конденсатора

,

имеющее противоположный входному

напряжению знак, – начинается разряд

конденсатора

,

,

где t – длительность разряда. Нуль компаратора фиксирует время TХ, полагая UС = 0 t = TХ – T0, получим

![]() .

.

С момента начала второго такта и до момента ТХ генератор G подает на счетчик последовательность калиброванных по частоте (с известным периодом Ti) импульсов. При известном числе импульсов m легко получить окончательное соотношение

![]() ,

,

в котором все входящие величины имеют высокую стабильность, что обеспечивает высокую точность преобразования. Необходимость задавать значения Т0, кратное периоду сетевой помехи, делает этот тип АЦП крайне медленным, пригодным для измерения практически только постоянных сигналов.

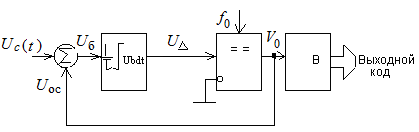

От этого недостатка свободны АЦП, построенные на принципе сигма-дельта-модуляции, сочетающем высокую точность АЦП двойного интегрирования с существенно большим быстродействием. Структурная схема такого АЦП приведена на рис. 7.24.

Рис. 7.24. Структурная схема АЦП на принципе сигма-дельта-модуляции

Свое название такой метод получил из-за наличия в структуре суммирующего устройства (сигма) и нуль-компаратора, определяющего знак приращения сигнала ошибки (дельта). Модулятор, по сути, представляет собой систему с отрицательной обратной связью дискретного типа, поскольку компаратор выдает сигнал только с периодом тактирующих импульсов, следующих с периодом Т0=1/f0. Частота дискретизации f0 выбирается во много раз больше частоты входного сигнала, так, чтобы в течение нескольких десятков периодов Т0 сигнал мог считаться постоянным. Выходной сигнал компаратора (V0 при U>0 и V0 при U<0) и является сигналом обратной связи. За счет большого усиления по петле обратной связи (обеспечиваемого компаратором) система стремится рассогласование Uб свести к нулю: Uб = UС(t) – UОС = 0. В процессе выполнения этого условия, происходящего за некоторое число периодов частоты дискретизации, на выходе компаратора генерируется определенная последовательность положительных и отрицательных импульсов. Как будет показано на примерах, анализ этих последовательностей, производимый вычислителем В, позволяет точно определить значение сигнала в некоторый момент времени UС(ti) и сформировать соответствующий этому значению код. Рассмотрим несколько примеров, для простоты полагая, что V0=1 В, а постоянная времени интегратора, выполняющего роль запоминающего устройства, выбрана из условия =Т0, так, что

.

.

Пусть значение сигнала за некоторый промежуток времени может считаться неизменным и равным 0,1 В. В табл. 7.1 приведены значения сигналов в характерных точках системы при ее работе.

Таблица 7.1

|

N такта |

U, В |

UОС, В |

N такта |

U, В |

UОС, В |

|

1 |

0,1 |

+1 |

12 |

0,2 |

+1 |

|

2 |

–0,8 |

–1 |

13 |

–0,7 |

–1 |

|

3 |

0,3 |

+1 |

14 |

0,4 |

+1 |

|

4 |

–,6 |

–1 |

15 |

–0,5 |

–1 |

|

5 |

0,5 |

+1 |

16 |

0,6 |

+1 |

|

6 |

–0,4 |

–1 |

17 |

–0,3 |

–1 |

|

7 |

0,7 |

+1 |

18 |

0,8 |

+1 |

|

8 |

–0,2 |

–1 |

19 |

–0,1 |

–1 |

|

9 |

0,9 |

+1 |

20 |

1,0 |

+1 |

|

10 |

0,0 |

+1 |

21 |

0,1 |

+1 |

|

11 |

–0,9 |

–1 |

22 |

–0,8 |

–1 |

Из таблицы видно, что значения сигналов в 1-м и 21-м, 2-м и 22-м тактах повторяются, что свидетельствует о периодичности, генерируемой компаратором последовательности с периодом в 20 тактов. Подсчет значений UОС за 20 тактов (например, со 2-го по 21-й), с учетом знаков, дает значение

UОС = +11 + (–9) = 2.

Разделив это число на число тактов за период, получим

![]() .

.

Для UС = 0,5 В получим следующие результаты (табл. 7.2).

Таблица 7.2

|

N такта |

U, В |

UОС, В |

|

1 |

0,5 |

+1 |

|

2 |

0,0 |

+1 |

|

3 |

–0,5 |

–1 |

|

4 |

1,0 |

–1 |

|

5 |

0,5 |

+1 |

|

6 |

0.0 |

+1 |

Теперь периодичность составляет 4 такта, значение

UОС

=

+3

+

(–1)

=

2,

![]() .

.

В теории дельта-сигма-модуляции показано, что для диапазона сигнала, укладывающегося в пределы V0 существует наибольший период, кратный всем возможным периодам при различных значениях сигнала, так что усреднение UОС за этот период будет давать точное значение любого сигнала, находящегося в промежутке 0V0. Таким образом, в дельта-сигма-модуляции происходит усреднение каждой временной выборки сигнала, что резко ослабляет влияние высокочастотных шумов и временные флуктуации параметров схемы. Поэтому рассмотренный принцип обладает в настоящее время максимальными потенциальными метрологическими возможностями. Серийно выпускаются дельта-сигма АЦП, имеющие погрешность от дискретности, соответствующей 24-м двоичным разрядам с нелинейностью 0,0015 %. Естественно, что эта разрядность реализуется для сравнительно низкочастотных сигналов ( 60 Гц). С повышением частоты разрядность резко снижается и для частоты 1 кГц составляет всего 12 разрядов.