- •«Национальный исследовательский

- •I. Основы АнАлоговой электроники

- •1. Задачи, решаемые электронной техникой, и элементы, необходимые для их решения

- •1.1. Электрические сигналы. Временное и спектральное представление

- •1.2. Усиление электрических сигналов

- •1.3. Модуляция сигналов

- •1.3.1. Амплитудная модуляция

- •1.3.2. Импульсно-кодовая модуляция

- •1.3.3. Широтно-импульсная модуляция

- •А б Рис. 1.19. Компаратор: а – схема; б – временные диаграммы при шим1.4. Фильтрация сигналов

- •1.5. Хранение и отображение информации

- •1.6. Преобразование электрической энергии

- •Контрольные вопросы и задания

- •Основные результаты первой главы

- •2. Математический аппарат описания электронных элементов

- •2.1. Описание нелинейных элементов

- •2.2. Линеаризация нелинейных уравнений

- •2.3. Частотный анализ линеаризованных цепей

- •2.4. Временной анализ линеаризованных цепей

- •Контрольные вопросы и задания

- •Основные результаты второй главы

- •3. Полупроводники – основа современной элементной базы электроники

- •3.1. Преимущества полупроводниковых элементов перед электровакуумными

- •3.2. Физические основы электропроводности полупроводников

- •3.3. Электропроводность беспримесного (собственного) полупроводника

- •3.4. Электропроводность примесных полупроводников

- •3.4.1. Донорная примесь

- •3.4.2. Акцепторная примесь

- •3.6. Инерционностьp-n-перехода

- •3.6.1. Зарядная емкостьp-n-перехода

- •3.6.2. Диффузионная емкость

- •3.7. Пробой p-n-перехода

- •3.7.1. Тепловой пробой

- •3.7.2. Электрический пробой

- •3.8. Математическая модельp-n-перехода

- •3.9. Переходметалл – полупроводник

- •Контрольные вопросы и задания

- •Основные результаты третьей главы

- •4. Многопереходные электронные элементы

- •4.1. Полупроводниковые триоды (биполярные транзисторы)

- •4.2. Активный режим работы биполярного транзистора

- •4.3. Статические характеристики биполярного транзистора для активного режима

- •4.4. Инерционность биполярного транзистора

- •4.5. Пробой коллекторного перехода

- •4.7. Нелинейная модель биполярного транзистора

- •4.8. Линеаризованная модель биполярного транзистора

- •4.9. Ключевой режим биполярного транзистора

- •4.10. Полевые транзисторы

- •4.11. Полевые транзисторы с управляющимp-n-переходом

- •4.12. Полевые транзисторы с изолированным затвором

- •4.13. Ключевой режим работы полевых транзисторов

- •4.14. Тиристоры

- •4.15. Элементы оптоэлектроники

- •4.15.1. Управляемые источники излучения

- •4.15.2. Фотоприемники

- •Контрольные вопросы и задания

- •Основные результаты четвертой главы

- •5. Основы теории электронных усилителей

- •5.1. Общие положения

- •Контрольные вопросы и задания

- •5.2. Обратная связь в усилительных устройствах

- •5.2.1. Влияние обратной связи на коэффициент усиления.

- •5.2.2. Влияние обратной связи на нестабильность усилителя

- •5.2.3. Влияние обратной связи на нелинейные искажения и шумы усилителя

- •5.2.4. Влияние обратной связи на входное и выходное сопротивления усилителя

- •5.2.5. Устойчивость усилителей с обратной связью

- •5.2.6. Коррекция частотных характеристик для обеспечения устойчивости усилителя

- •Контрольные вопросы и задания

- •5.3. Принципы построения усилительных каскадов

- •5.3.1. Цепи задания и стабилизации режима покоя

- •5.3.2. Элементы связи усилительных устройств

- •К Рис. 5.34. Оптическая связь онтрольные вопросы и задания

- •5.4. Операционные усилители

- •5.4.1. Модели оу

- •5.4.2. Масштабирующий инвертирующий усилитель

- •5.4.3. Масштабирующий неинвертирующий усилитель

- •5.4.4. Суммирующий усилитель

- •5.4.5. Вычитающий усилитель

- •5.4.6. Интегрирующий усилитель

- •5.4.7. Нелинейные функциональные преобразователи сигналов

- •Контрольные вопросы и задания

- •5.5. Усилители мощности

- •5.5.1. Линейные усилители мощности

- •5.5.2. Усилители мощности ключевого типа

- •Контрольные вопросы и задания

- •Основные результаты пятой главы

- •6. Автогенераторы

- •Основные результаты шестой главы

- •7. Источники вторичного электропитания электронных устройств

- •7.1. Классическая схема вторичного источника (без преобразования частоты сети)

- •7.2. Функциональные элементы вторичных источников электропитания

- •7.2.1. Преобразователи переменного напряжения

- •7.2.2. Стабилизаторы постоянного напряжения

- •7.3. Вторичные источники с преобразованием частоты сети

- •Vd Схема упр.

- •Vd Схема упр. Ul

- •Контрольные вопросы и задания

- •Основные результаты седьмой главы

- •II. Основы цифровой электроники

- •1. Введение

- •2. Логические функции

- •2.1. Логические функции и способы их представления

- •2.2. Основы алгебры логики

- •2.2.1. Функция не

- •2.2.2. Функция или

- •2.2.3. Функция и

- •2.3. Логические элементы и-не, или-не

- •2.3.1. Элемент и-не (штрих Шеффера)

- •2.3.2. Элемент или-не (стрелка Пирса)

- •2.4. Синтез логических устройств

- •2.5. Выбор системы логических элементов

- •2.6. Минимизация логических функций

- •Контрольные вопросы и задания

- •3. Характеристики и параметры логических элементов, основы схемотехники

- •3.1. Логические уровни, нагрузочная способность

- •3.2. Логические элементы с тремя состояниями

- •3.3. Быстродействие логических элементов

- •3.4. Помехоустойчивость логических элементов

- •3.5. Число входов логических элементов

- •3.6. Специальные типы логических элементов. Логические элементы с открытым коллектором

- •3.6.1. Расширители числа входов

- •3.6.2. Схема согласования уровней

- •3.6.3. Логический элемент с разрешением по входу

- •Контрольные вопросы и задания

- •4. Цифровые устройства комбинационного типа

- •4.1. Преобразователи кодов, шифраторы, дешифраторы

- •4.2. Мультиплексоры

- •4.3. Сумматоры

- •4.4. Цифровые компараторы

- •Контрольные вопросы и задания

- •5. Последовательностные цифровые устройства

- •5.1. Триггеры

- •5.1.5. Триггер Шмитта

- •5.2. Цифровые счетчики импульсов и делители частоты следования

- •5.2.1. Двоичные счетчики

- •5.2.2. Недвоичные счетчики

- •5.3. Регистры

- •Контрольные вопросы и задания

- •6. Генераторы импульСныхСигналов

- •6.1. Автогенераторы прямоугольных импульсов (мультивибраторы)

- •6.2. Ждущий (заторможенный) режим генераторов

- •6.3. Интегральные таймеры

- •6.4. Генераторы линейно изменяющегося напряжения (тока)

- •Контрольные вопросы и задания

- •7. УстройствасОпРяжЕнияцифровых и аналоговых систем

- •7.1. Цифроаналоговые преобразователи

- •7.2. Аналого-цифровые преобразователи

- •7.2.1. Ацп последовательного приближения

- •7.2.2. Ацп параллельного типа

- •7.2.3. Ацп интегрирующего типа

- •Контрольные вопросы и задания

- •8. Введение в микропроцессорную технику

- •8.1. Арифметическо-логические устройства

- •8.2. Полупроводниковые запоминающие устройства

- •8.3. Программируемые логические интегральные матрицы

- •8.4. Интерфейсные устройства

- •Контрольные вопросы и задания

- •Приложение справочные данные интегральных схем

- •Литература

- •Оглавление

4.7. Нелинейная модель биполярного транзистора

Нелинейные модели, используемые в современных компьютерных моделирующих программах, с высокой точностью отражают все свойства биполярного транзистора (управляемость, инерционность, пробой переходов, температурные зависимости) и содержат несколько десятков параметров. Результаты моделирования обладают близкой к 100 % достоверностью, что практически исключает необходимость в натурном испытании.

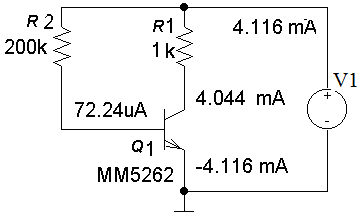

На рис. 4.11 приведены результаты расчета режима покоя для двух значений температуры, полученные с использованием моделирующей программы.

а б

Рис. 4.11. Результаты компьютерного моделирования транзисторного нелинейного устройства: а – для t = 27 C; б – для t = 100 C

4.8. Линеаризованная модель биполярного транзистора

Используя формальную запись нелинейных зависимостей

Iк= F(Iб, Uкэ);

Uбэ= F(Iб, Uкэ) (4.7)

и разлагая (4.7) в ряд Тейлора относительно некоторого режима покоя

Iб0, Iк0, Uкэ0, Uбэ0,

получаем линеаризованное уравнение

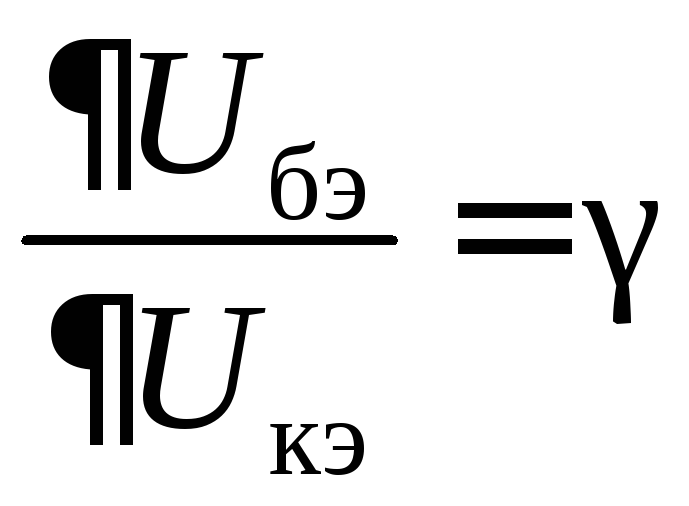

![]() ,

,

![]() ,

,

или, вводя обозначения,

![]() ,

,

,

,

,

,

;

;

![]() ,

,

![]() .

(4.8)

.

(4.8)

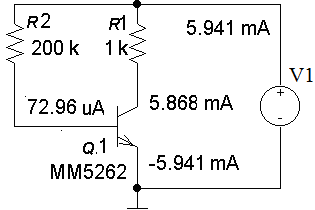

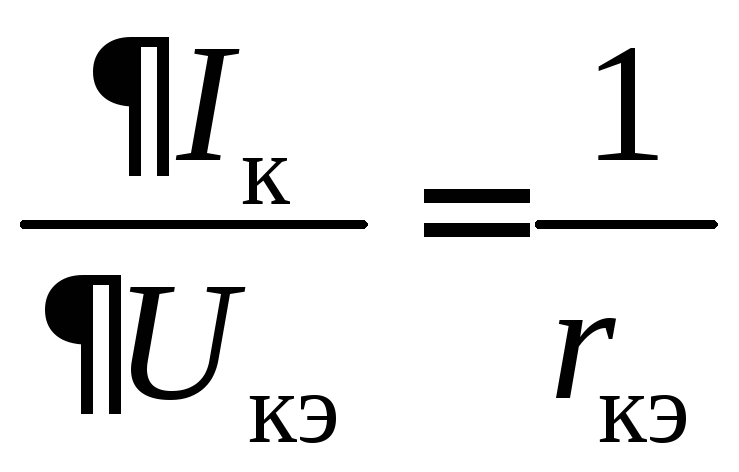

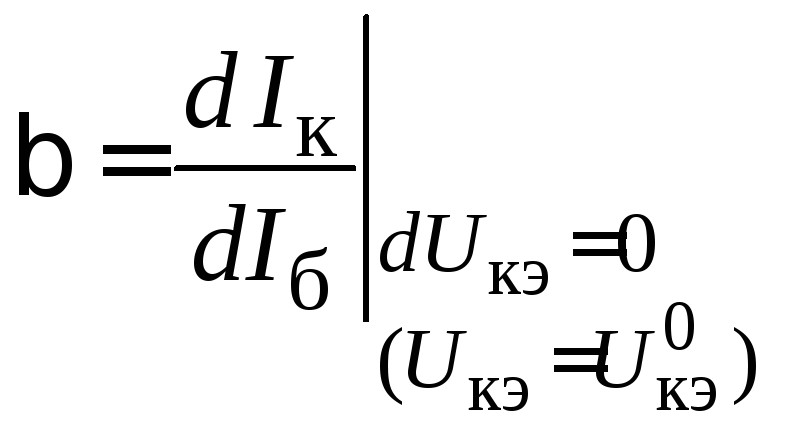

Физический смысл коэффициентов линеаризованного уравнения (4.8) вытекает из математических соотношений:

–дифференциальный

коэффициент усиления тока базы;

–дифференциальный

коэффициент усиления тока базы;

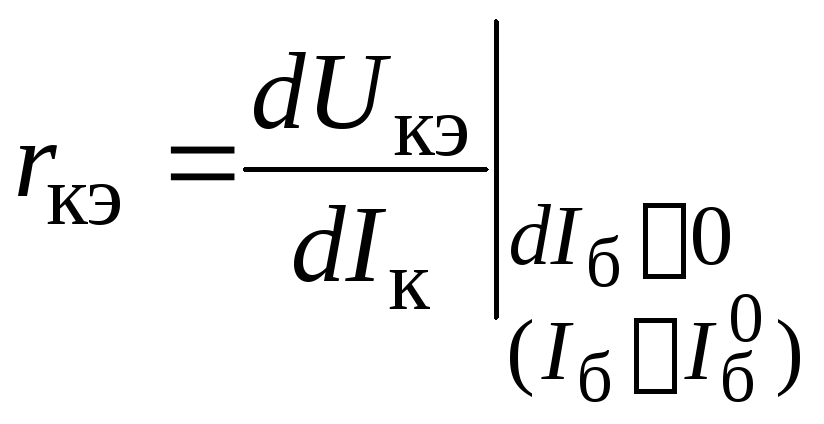

–дифференциальное

выходное (внутреннее) сопротивление;

–дифференциальное

выходное (внутреннее) сопротивление;

![]() –дифференциальное

входное сопротивление;

–дифференциальное

входное сопротивление;

–коэффициент

обратной связи по напряжению.

–коэффициент

обратной связи по напряжению.

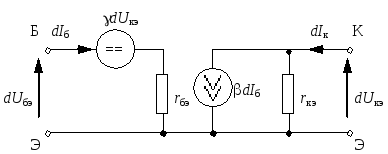

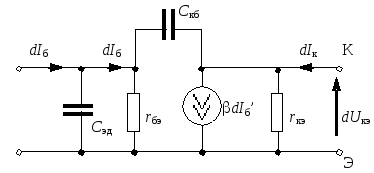

Уравнениям (4.8) соответствует электрическая схема, которая и является линеаризованной моделью биполярного транзистора (рис. 4.12).

Рис. 4.12. Линеаризованная электрическая модель биполярного транзистора

Параметры линеаризованной модели зависят от режима покоя, поэтому в справочных данных они приводятся для конкретного режима и для другого режима должны быть пересчитаны, определены экспериментально или графически по ВАХ.

В технической литературе уравнения (4.8) часто приводятся в системе h-параметров (из теории электрических четырехполюсников):

![]() ,

,

![]() . (4.9)

. (4.9)

Из (4.8) и (4.9) очевидны значения и смысл h-параметров.

Инерционность биполярного транзистора в активном режиме можно определить введением диффузионной емкости открытого эмиттерного перехода Сэд и зарядной емкости коллекторного перехода Скз (см. рис. 4.13), где для упрощения принято = 0.

Рис. 4.13. Линеаризованная модель биполярного транзистора, учитывающая инерционность

Следует еще раз подчеркнуть, что практическое использование даже линеаризованных моделей для ручного расчета приводит к достаточно сложным аналитическим выражениям, поэтому следует рекомендовать в качестве основного способа анализа – цифровое моделирование.

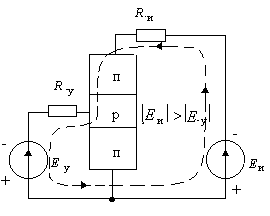

4.9. Ключевой режим биполярного транзистора

Рис.

4.14. Потеря управляемости

ключа на

биполярном транзисторе

а б

а б

Рис. 4.15. Варианты ключей знакопеременного сигнала:

а – на двух транзисторах с отсекающими диодами; б – с транзистором, включенным в диагональ диодного моста

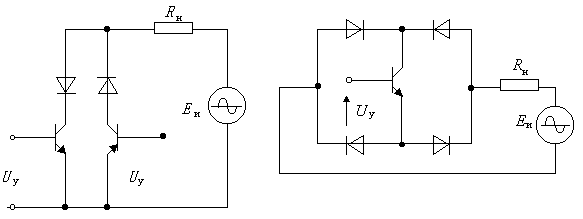

При работе с однополярным источником коммутируемая нагрузка может быть включена или последовательно, или параллельно с ключевым элементом (рис. 4.16).

а б

Рис. 4.16. Схема последовательного (а) и параллельного (б) ключа

Очевидно, что наличие дополнительного (балластного сопротивления) Rбв параллельном ключе усиливает потери энергии. Поэтому в преобразовательной технике используются только последовательные ключи, а в информационной электронике из-за удобства подключения нагрузки (источник управляющего сигнала, нагрузка и источник питания имеют общую точку)–параллельные ключи.

Минимальным сопротивлением в открытом состоянии обладает транзистор в режиме насыщения (оба перехода открыты). Кроме того, в режиме насыщения напряжение на замкнутом ключе практически не зависит от вариаций усиления транзистора по току, что очень важно при массовом производстве однотипных ключевых элементов, как это имеет место в цифровой электронике.

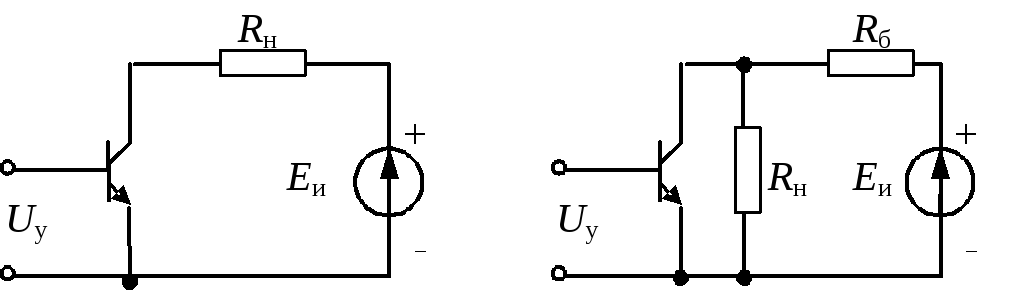

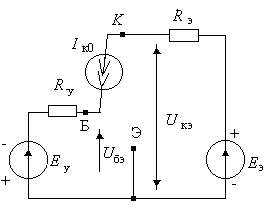

Как и в активном режиме, режим насыщения удобнее характеризовать соотношением токов базы коллектора. Учитывая, что параллельный ключ на основе теоремы об эквивалентном генераторе может быть приведен к схеме последовательного, далее будет рассмотрена обобщенная схема последовательного ключа (рис. 4.17).

а б

Рис. 4.17. Замена параллельного ключа (а) эквивалентным последовательным (б)

Полагая, что сопротивление насыщенного транзистора много меньше эквивалентного сопротивления нагрузки –

rн << Rэ,

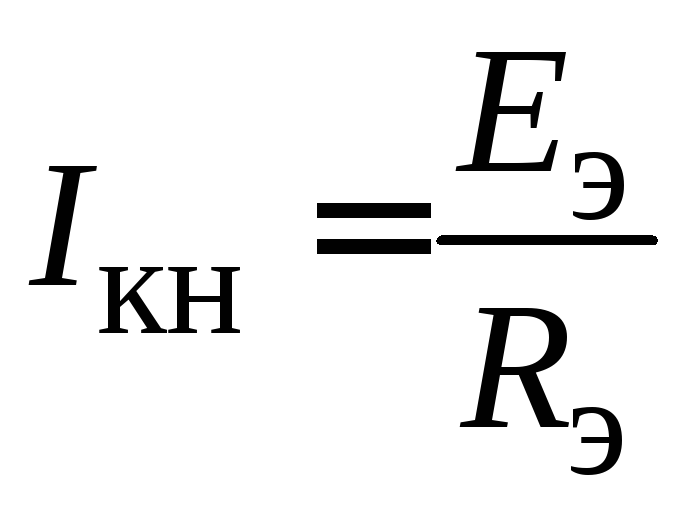

можно считать, что в режиме насыщения ток коллектора, достигающий своего максимального значения, равен

. (4.10)

. (4.10)

В активном режиме имело бы место соотношение

ВIб Iкн.

Переход в режим насыщения наступает при условии

ВIб>Iкн. (4.11)

Соотношения (4.9) и (4.10) являются основными для расчета элементов управления, обеспечивающих насыщенный режим.

Рис.

4.18. Упрощенная модель

насыщенного

транзистора

Из-за разницы в площадях переходов имеет место неравенство

Iэо<< Iко,

что позволяет для расчетов в режиме отсечки использовать упрощенную модель (см. рис. 4.19).

Рис. 4.19. Упрощенная

модель

транзистора в режиме отсечки

U=Еэ – Rэ Iко Еэ.

Условием запирания является неравенство (для n-p-n-транзистора)Uбэ<0,Uбэ>>т, которое сводится к неравенству

Еу>IкоRу. (4.12)

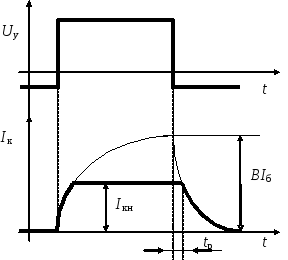

Рис.

4.20. Задержка выключения

транзистора

на время рассасывания

избыточных

носителей в базе tp

Рис.

4.20. Задержка выключения

транзистора

на время рассасывания

избыточных

носителей в базе tp

Из-за того что при насыщении заряды в базу поступают как со стороны коллектора, так и со стороны эмиттера, и в базе накапливается большой избыточный заряд неосновных носителей. При запирании, пока этот заряд «рассасывается», транзистор оказывается неуправляемым, поэтому в переходном процессе насыщенного ключа имеется характерный отрезок времени (время рассасывания tр), рис. 4.20. Длительность времени рассасывания существенно ограничивает скорость переключения цифровых ключей, и тем больше, чем сильнее выполняется условие насыщения (4.11). Поэтому в цифровой электронике используются различные способы, предотвращающие глубокое насыщение.

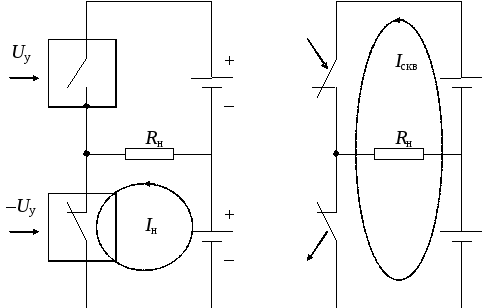

В силовой электронике при построении преобразователей используются схемы последовательного соединения двух ключей, находящихся в противоположных состояниях. Однако за счет процесса рассасывания создается ситуация, когда ранее запертый транзистор уже открылся, а ранее открытый и насыщенный еще находится в стадии рассасывания. В результате через оба транзистора, оказавшиеся одновременно открытыми на некоторое время, течет ничем не ограниченный так называемый сквозной ток, который существенно ухудшает КПД преобразователя и может вывести активные элементы из строя (рис. 4.21).

а б

Рис. 4.21. Статическое состояние ключевых элементов (а), состояние при выходе из насыщения ранее открытого транзистора (б)

На практике для исключения эффекта сквозного тока используют временную задержку открывания ранее запертого транзистора на момент времени рассасывания насыщенного транзистора.