- •«Национальный исследовательский

- •I. Основы АнАлоговой электроники

- •1. Задачи, решаемые электронной техникой, и элементы, необходимые для их решения

- •1.1. Электрические сигналы. Временное и спектральное представление

- •1.2. Усиление электрических сигналов

- •1.3. Модуляция сигналов

- •1.3.1. Амплитудная модуляция

- •1.3.2. Импульсно-кодовая модуляция

- •1.3.3. Широтно-импульсная модуляция

- •А б Рис. 1.19. Компаратор: а – схема; б – временные диаграммы при шим1.4. Фильтрация сигналов

- •1.5. Хранение и отображение информации

- •1.6. Преобразование электрической энергии

- •Контрольные вопросы и задания

- •Основные результаты первой главы

- •2. Математический аппарат описания электронных элементов

- •2.1. Описание нелинейных элементов

- •2.2. Линеаризация нелинейных уравнений

- •2.3. Частотный анализ линеаризованных цепей

- •2.4. Временной анализ линеаризованных цепей

- •Контрольные вопросы и задания

- •Основные результаты второй главы

- •3. Полупроводники – основа современной элементной базы электроники

- •3.1. Преимущества полупроводниковых элементов перед электровакуумными

- •3.2. Физические основы электропроводности полупроводников

- •3.3. Электропроводность беспримесного (собственного) полупроводника

- •3.4. Электропроводность примесных полупроводников

- •3.4.1. Донорная примесь

- •3.4.2. Акцепторная примесь

- •3.6. Инерционностьp-n-перехода

- •3.6.1. Зарядная емкостьp-n-перехода

- •3.6.2. Диффузионная емкость

- •3.7. Пробой p-n-перехода

- •3.7.1. Тепловой пробой

- •3.7.2. Электрический пробой

- •3.8. Математическая модельp-n-перехода

- •3.9. Переходметалл – полупроводник

- •Контрольные вопросы и задания

- •Основные результаты третьей главы

- •4. Многопереходные электронные элементы

- •4.1. Полупроводниковые триоды (биполярные транзисторы)

- •4.2. Активный режим работы биполярного транзистора

- •4.3. Статические характеристики биполярного транзистора для активного режима

- •4.4. Инерционность биполярного транзистора

- •4.5. Пробой коллекторного перехода

- •4.7. Нелинейная модель биполярного транзистора

- •4.8. Линеаризованная модель биполярного транзистора

- •4.9. Ключевой режим биполярного транзистора

- •4.10. Полевые транзисторы

- •4.11. Полевые транзисторы с управляющимp-n-переходом

- •4.12. Полевые транзисторы с изолированным затвором

- •4.13. Ключевой режим работы полевых транзисторов

- •4.14. Тиристоры

- •4.15. Элементы оптоэлектроники

- •4.15.1. Управляемые источники излучения

- •4.15.2. Фотоприемники

- •Контрольные вопросы и задания

- •Основные результаты четвертой главы

- •5. Основы теории электронных усилителей

- •5.1. Общие положения

- •Контрольные вопросы и задания

- •5.2. Обратная связь в усилительных устройствах

- •5.2.1. Влияние обратной связи на коэффициент усиления.

- •5.2.2. Влияние обратной связи на нестабильность усилителя

- •5.2.3. Влияние обратной связи на нелинейные искажения и шумы усилителя

- •5.2.4. Влияние обратной связи на входное и выходное сопротивления усилителя

- •5.2.5. Устойчивость усилителей с обратной связью

- •5.2.6. Коррекция частотных характеристик для обеспечения устойчивости усилителя

- •Контрольные вопросы и задания

- •5.3. Принципы построения усилительных каскадов

- •5.3.1. Цепи задания и стабилизации режима покоя

- •5.3.2. Элементы связи усилительных устройств

- •К Рис. 5.34. Оптическая связь онтрольные вопросы и задания

- •5.4. Операционные усилители

- •5.4.1. Модели оу

- •5.4.2. Масштабирующий инвертирующий усилитель

- •5.4.3. Масштабирующий неинвертирующий усилитель

- •5.4.4. Суммирующий усилитель

- •5.4.5. Вычитающий усилитель

- •5.4.6. Интегрирующий усилитель

- •5.4.7. Нелинейные функциональные преобразователи сигналов

- •Контрольные вопросы и задания

- •5.5. Усилители мощности

- •5.5.1. Линейные усилители мощности

- •5.5.2. Усилители мощности ключевого типа

- •Контрольные вопросы и задания

- •Основные результаты пятой главы

- •6. Автогенераторы

- •Основные результаты шестой главы

- •7. Источники вторичного электропитания электронных устройств

- •7.1. Классическая схема вторичного источника (без преобразования частоты сети)

- •7.2. Функциональные элементы вторичных источников электропитания

- •7.2.1. Преобразователи переменного напряжения

- •7.2.2. Стабилизаторы постоянного напряжения

- •7.3. Вторичные источники с преобразованием частоты сети

- •Vd Схема упр.

- •Vd Схема упр. Ul

- •Контрольные вопросы и задания

- •Основные результаты седьмой главы

- •II. Основы цифровой электроники

- •1. Введение

- •2. Логические функции

- •2.1. Логические функции и способы их представления

- •2.2. Основы алгебры логики

- •2.2.1. Функция не

- •2.2.2. Функция или

- •2.2.3. Функция и

- •2.3. Логические элементы и-не, или-не

- •2.3.1. Элемент и-не (штрих Шеффера)

- •2.3.2. Элемент или-не (стрелка Пирса)

- •2.4. Синтез логических устройств

- •2.5. Выбор системы логических элементов

- •2.6. Минимизация логических функций

- •Контрольные вопросы и задания

- •3. Характеристики и параметры логических элементов, основы схемотехники

- •3.1. Логические уровни, нагрузочная способность

- •3.2. Логические элементы с тремя состояниями

- •3.3. Быстродействие логических элементов

- •3.4. Помехоустойчивость логических элементов

- •3.5. Число входов логических элементов

- •3.6. Специальные типы логических элементов. Логические элементы с открытым коллектором

- •3.6.1. Расширители числа входов

- •3.6.2. Схема согласования уровней

- •3.6.3. Логический элемент с разрешением по входу

- •Контрольные вопросы и задания

- •4. Цифровые устройства комбинационного типа

- •4.1. Преобразователи кодов, шифраторы, дешифраторы

- •4.2. Мультиплексоры

- •4.3. Сумматоры

- •4.4. Цифровые компараторы

- •Контрольные вопросы и задания

- •5. Последовательностные цифровые устройства

- •5.1. Триггеры

- •5.1.5. Триггер Шмитта

- •5.2. Цифровые счетчики импульсов и делители частоты следования

- •5.2.1. Двоичные счетчики

- •5.2.2. Недвоичные счетчики

- •5.3. Регистры

- •Контрольные вопросы и задания

- •6. Генераторы импульСныхСигналов

- •6.1. Автогенераторы прямоугольных импульсов (мультивибраторы)

- •6.2. Ждущий (заторможенный) режим генераторов

- •6.3. Интегральные таймеры

- •6.4. Генераторы линейно изменяющегося напряжения (тока)

- •Контрольные вопросы и задания

- •7. УстройствасОпРяжЕнияцифровых и аналоговых систем

- •7.1. Цифроаналоговые преобразователи

- •7.2. Аналого-цифровые преобразователи

- •7.2.1. Ацп последовательного приближения

- •7.2.2. Ацп параллельного типа

- •7.2.3. Ацп интегрирующего типа

- •Контрольные вопросы и задания

- •8. Введение в микропроцессорную технику

- •8.1. Арифметическо-логические устройства

- •8.2. Полупроводниковые запоминающие устройства

- •8.3. Программируемые логические интегральные матрицы

- •8.4. Интерфейсные устройства

- •Контрольные вопросы и задания

- •Приложение справочные данные интегральных схем

- •Литература

- •Оглавление

Контрольные вопросы и задания

Найдите по справочнику дешифратор К555ИД7. Разберитесь с его работой по таблице состояний.

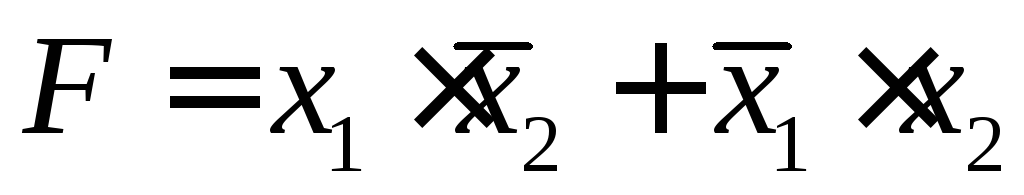

Найдите по справочнику мультиплексор К531КП2. Разберитесь с его работой по таблице состояний. Используя этот мультиплексор, постройте устройство, выполняющее следующую логическую функцию:

.

.

5. Последовательностные цифровые устройства

Состояние выходов последовательностных устройств определяется не только состоянием входов в данный момент времени, но и предыдущим состоянием выходов. Таким образом, последовательностные устройства обладают «памятью». Рассмотрим наиболее характерные последовательностные устройства.

5.1. Триггеры

Триггеры–

цифровые устройства с двумя выходами

(прямымQи инверсным

![]() ),

состояние которых, однажды установленное,

может сохраняться сколь угодно долго.

Изменение исходного состояния производится

с помощью входных сигналов по правилу

работы каждого типа триггера. Таким

образом, триггер может хранить заложенный

в нем 1 бит информации.

),

состояние которых, однажды установленное,

может сохраняться сколь угодно долго.

Изменение исходного состояния производится

с помощью входных сигналов по правилу

работы каждого типа триггера. Таким

образом, триггер может хранить заложенный

в нем 1 бит информации.

О

Рис. 5.1. Обобщенная

схема триггера

![]()

![]()

![]() = 0

илиQ = 0,

= 0

илиQ = 0,![]() =1),

и комбинационная схема (KC),

преобразующая поступающие сигналы в

сигналы управления БЯ. Комбинационная

схема содержит информационные входы

(X0Xn),

входы синхронизации

=1),

и комбинационная схема (KC),

преобразующая поступающие сигналы в

сигналы управления БЯ. Комбинационная

схема содержит информационные входы

(X0Xn),

входы синхронизации![]() и входы разрешения

и входы разрешения![]() .

.

В

принципе можно синтезировать большое

число триггерных структур с различным

законом функционирования. Однако в

цифровой электронике нашли применение

4 типа триггеров: RC-триггер,

D-триггер,

JK-триггер,

T-триггер.

Информационные входы этих триггеров

имеют следующие обозначения:

![]() (Set

– установка) – вход для раздельной

установки триггера в состояние «1» (Q=1,

(Set

– установка) – вход для раздельной

установки триггера в состояние «1» (Q=1,

![]() =0);

R

(Reset

– сброс) – вход для раздельной установки

триггера в состояние «0» (Q = 0,

=0);

R

(Reset

– сброс) – вход для раздельной установки

триггера в состояние «0» (Q = 0,

![]() = 1);

D (Delay

– задержка) – вход для установки триггера

в состояние «1» или «0»; J

(Jerk

– внезапное выключение) – вход для

раздельной установки триггера в состояние

«1»; K

(Kill

– внезапное отключение) – вход для

раздельной установки в состояние «0»;

T (Toggle

– релаксатор) – счетный вход триггера;

V (Valre

– клапан, вентиль) – управляющий вход

для разрешения приема информации либо

тактовых импульсов; C

(Clock

– первичный источник синхронизации) –

разрешает запись информации в триггер.

= 1);

D (Delay

– задержка) – вход для установки триггера

в состояние «1» или «0»; J

(Jerk

– внезапное выключение) – вход для

раздельной установки триггера в состояние

«1»; K

(Kill

– внезапное отключение) – вход для

раздельной установки в состояние «0»;

T (Toggle

– релаксатор) – счетный вход триггера;

V (Valre

– клапан, вентиль) – управляющий вход

для разрешения приема информации либо

тактовых импульсов; C

(Clock

– первичный источник синхронизации) –

разрешает запись информации в триггер.

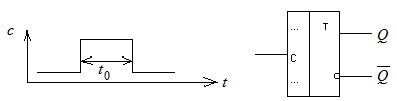

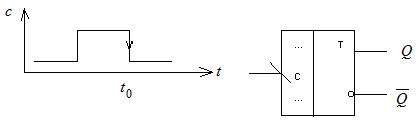

По способу восприятия входных сигналов триггеры могут быть асинхронными (нетактируемыми) и синхронными (тактируемыми). Асинхронные триггеры воспринимают информацию в любой момент времени, а синхронные – только при наличии разрешающего сигнала на специальном тактовом C-входе. Синхронизация ограничивает время приема триггером входных сигналов, а следовательно, уменьшает вероятность, при появления помехи на сигнальных входах, ложного срабатывания триггера. Другими словами, синхронизация повышает помехоустойчивость, которая является важным параметром любого цифрового устройства, т. к. замена в результате помехи хотя бы одного элемента двоичного кода приведет к полному искажению информации.

Синхронизация

может быть статическая – уровнем

(высоким, низким) или динамическая –

перепадом на C-входе

(фронтом, срезом). Условные обозначения

способов синхронизации представлены

на рис. 5.2, где С

– синхроимпульс,

![]() – промежутки времени, в течение которых

триггер воспринимает входную информацию.

– промежутки времени, в течение которых

триггер воспринимает входную информацию.

По виду выходных сигналов триггеры разделяют на статические и динамические. Статические – триггеры, у которых выходные сигналы в устойчивых состояниях остаются неизменными во времени. В динамических триггерах выходные сигналы представляют последовательность импульсов.

По способу запоминания информации могут быть триггеры с логической и физической организацией памяти. Первые выполняются на логических элементах, во вторых используются нелинейные свойства материалов или нелинейные характеристики компонентов.

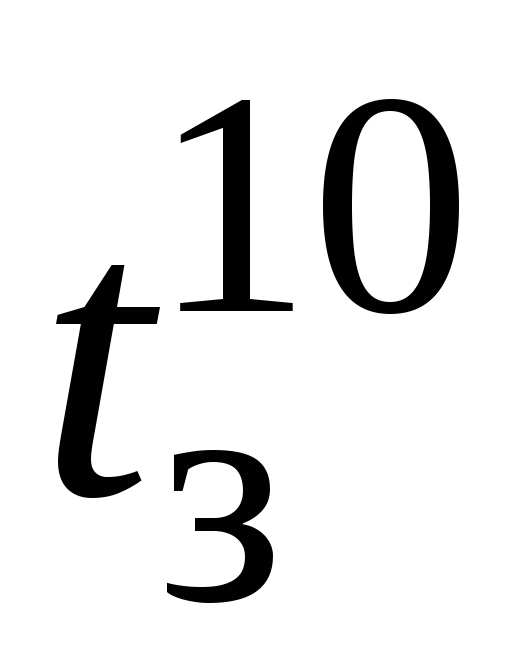

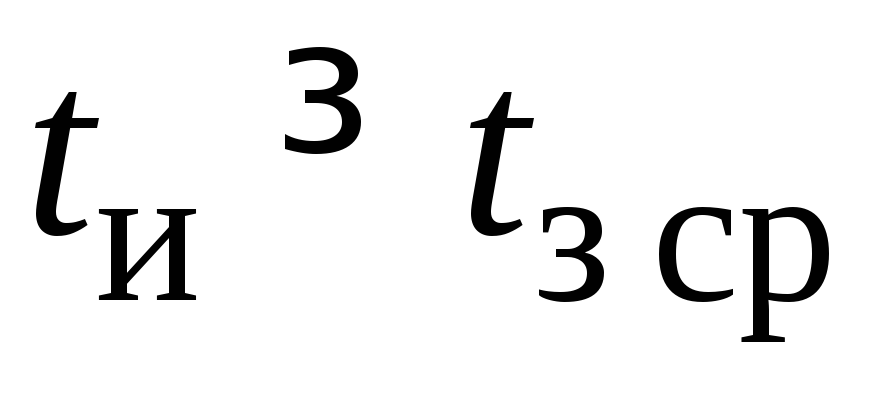

Характеристики триггеров определяются прежде всего параметрами логических элементов, на которых выполнен триггер. Специфическими параметрами триггера являются:

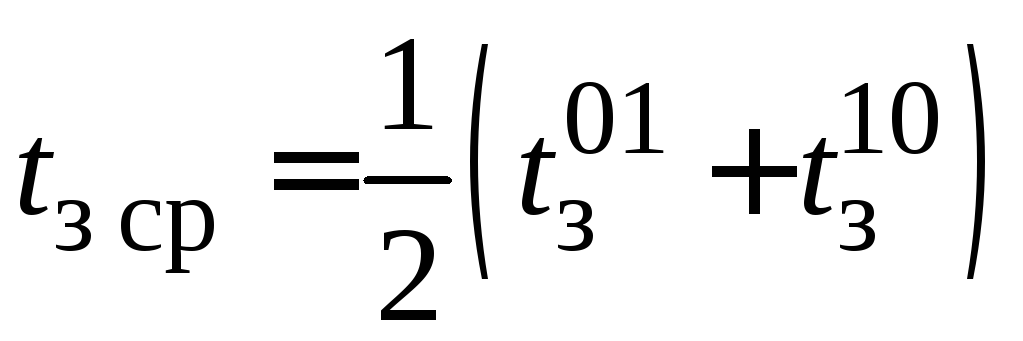

время задержки переключения триггера

,

, ,

, ,

которое определяется количеством

элементов от информационного (тактового)

входа до выхода. Минимальная длительность

входного сигнала

,

которое определяется количеством

элементов от информационного (тактового)

входа до выхода. Минимальная длительность

входного сигнала ;

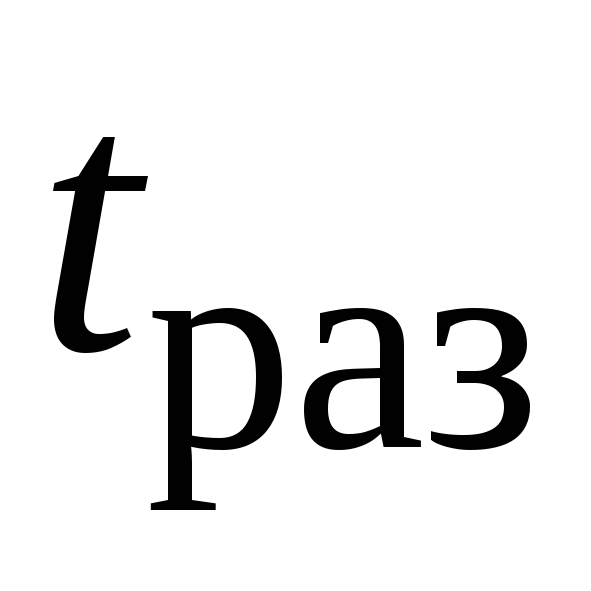

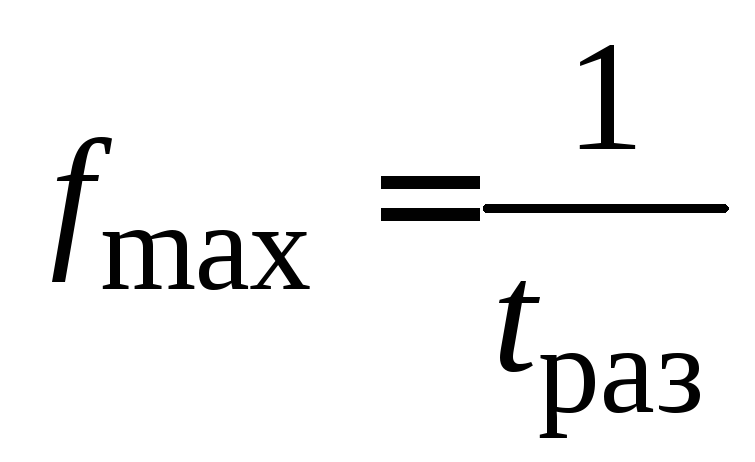

;разрешающее время триггера

– наименьший интервал времени между

входными сигналами минимальной

длительности, вызывающими бесперебойное

переключение триггера;

– наименьший интервал времени между

входными сигналами минимальной

длительности, вызывающими бесперебойное

переключение триггера;максимальная частота переключения триггера

.

.

Обычно рабочую частоту принимают в 1,5 раза меньше максимальной.

а

б

в

Рис. 5.2. Способы синхронизации и условные обозначения триггеров:

а – высоким уровнем синхроимпульса; б – фронтом синхроимпульса;

в – срезом синхроимпульса

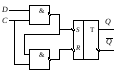

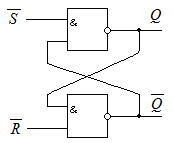

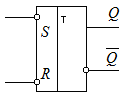

5.1.1.RS-триггер

RS-триггер может

быть построен на логических элементах

ИЛИ-НЕ, И-НЕ. На рис. 5.3 приведена схемаRS-триггера на элементах ИЛИ-НЕ. Как

видно из схемы, логические элементы

замкнуты в кольцо (

Рис.

5.3. Схема RS-триггера

на элементах ИЛИ-НЕ

|

Таблица 5.1 | ||||

|

R |

S |

Qn |

Qn+1 |

Вид сигнала |

|

0 |

0 |

1 |

1 |

хранение |

|

0 |

0 |

0 |

0 | |

|

0 |

1 |

1 |

1 |

уст. 1 |

|

0 |

1 |

0 |

1 | |

|

1 |

0 |

1 |

0 |

уст. 0 |

|

1 |

0 |

0 |

0 | |

|

1 |

1 |

1 |

X |

запрет |

|

1 |

1 |

0 |

X | |

![]() .

.

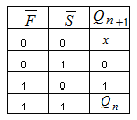

Если это уравнение перевести в базис И-НЕ –

![]()

– и построить структурную схему, то получим RS-триггер с инверсными входами (рис. 5.4).

а б в

Рис. 5.4. RS-триггер с инверсными входами:

а – электрическая схема; б – таблица переходов; в – условное обозначение

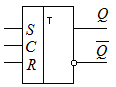

На основе этого триггера можно продемонстрировать схему триггера с синхронизацией уровня синхроимпульса (рис. 5.5).

а б

Рис. 5.5. Схема RS-триггера с синхронизацией высоким уровнем синхроимпульса (а); условное обозначение (б)

При С = 0 на выходах входных элементов И-НЕ фиксируются высокие уровни, которые удерживают инверсныйRS-триггер в исходном состоянии. Таким образом, блокируется прием входной информации. ПриС = 1 легко убедиться, что схема ведет себя какRS-триггер с прямыми входами.

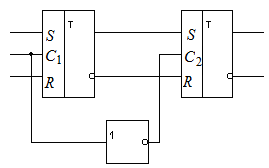

Организовать режим синхронизации перепадом синхроимпульса можно путем последовательного включения двух триггеров, тактируемых уровнем (рис. 5.6), такая структура называется двухступенчатой.

а б

Рис. 5.6. Схема RS-триггера, тактируемого срезом синхроимпульса (а);

условное обозначение (б)

При С1 = 1 входной триггер воспринимает входную информацию, а выходной блокирован (С2 = 0). В момент С1 = 0 (срез синхроимпульса) входной триггер блокируется, а выходной разблокируется (С2 = 1) и воспримет информацию, которая зафиксировалась во входном триггере в момент его блокировки.

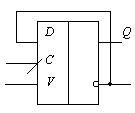

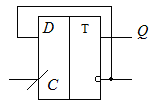

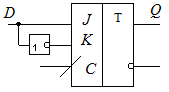

5.1.2.D-триггер

D-триггер – это синхронный триггер с одним информационным входом, предназначенным для задержки логического сигнала. Часто поэтому D-триггер называют триггером-задержкой. D-триггер повторяет значение сигнала, которое было установлено на входе триггера в предшествующий момент с задержкой максимум на один период (такт) синхроимпульса. Схема синхронизируемого уровнем D-триггера приведена на рис. 5.7. Уравнение, описывающее работу D-триггера,

![]() ,

,

при Cn = 1, Qn+1 = Dn+1 – повторяет входной сигнал, при C = 0, Qn+1=Qn – режим хранения. С использованием двухступенчатой структуры строятся D-триггеры, тактируемые срезом импульса. В таких триггерах часто делается еще один вход – вход разрешения V. В этом случае при V=1 структура работает как синхронный D-триггер, а при V=0 находится в режиме хранения (рис. 5.8).

|

|

|

|

Рис. 5.7. Триггер, тактируемый уровнем по V входу DV-триггера

|

Рис. 5.8. Триггер, тактируемый уровнем по V входу DV-триггера

|

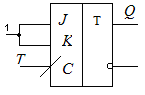

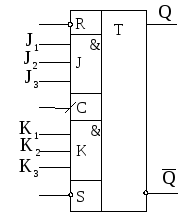

5.1.3.JK-триггер

JK-триггер

–

это триггер с раздельными установочными

входами (JS,

KR).

Схема JK-триггера

приведена на рис 5.9. В отличие от

RS-триггера

(см. рис. 5.5) в JK-триггере

введены дополнительные связи выходов

со входами через элементы И-НЕ. Это

привело к тому, что при комбинации

J = K = 1

триггер меняет свое состояние на

противоположное, такая комбинация не

является запрещенной. Работа JK-триггера

отражена в таблице переключений (см.

табл. 5.2) и описывается логическим

уравнением

J C S Q![]() .

Если взять элементы И-НЕ трехвходовые

и третьи входы объединить (см. пунктир

на рис. 5.9), то получится синхронизируемый

уровнем JK-триггер.

Как и другие типы триггеров по

двухступенчатой структуре строятся

JK-триггеры,

синхронизируемые срезом,

ф

.

Если взять элементы И-НЕ трехвходовые

и третьи входы объединить (см. пунктир

на рис. 5.9), то получится синхронизируемый

уровнем JK-триггер.

Как и другие типы триггеров по

двухступенчатой структуре строятся

JK-триггеры,

синхронизируемые срезом,

ф

K![]()

![]()

Таблица

5.2

0

0

1

0

1

0

1

0

1

1

Рис.

5.9. Схема JK-триггера

![]()

![]()

![]()

![]()

![]()

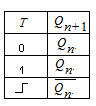

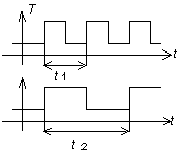

5.1.4.T-триггер

T-триггер

имеет один информационный вход,

переключение осуществляется перепадом

входного сигнала. Таблицы состояний,

графическое изображение, временные

диаграммы приведены на рис. 5.10. Уравнение,

описывающее работу T-триггера,

–

![]() .

Как видно из временных диаграмм,T-триггер

осуществляет деление частоты следования

входных импульсов в два раза

.

Как видно из временных диаграмм,T-триггер

осуществляет деление частоты следования

входных импульсов в два раза

![]() ,

что определяет применение в ряде

устройств.

,

что определяет применение в ряде

устройств.

а б в

Рис. 5.10. Асинхронный Т-триггер:

а – таблица состояний; б – условное обозначение; в – временная диаграмма сигналов

а б

Рис.

5.11. Триггеры Рис. 5.12.

Универсальный

со

счетным запуском

JK-триггер

в качестве

D-триггера

J1

J2

![]() соединен со входомD,

то с приходом тактового импульса Qn+1=Qn,

а в JK-триггере

при J=K=1

будет изменяться состояние выхода на

противоположное, и число импульсов на

выходе будет в два раза меньше, т. е.

такие структуры работают как T-триггеры.

На рис. 5.12 показана возможность

использования JK-триггера

в качестве D-триггера.

Таким образом, JK-триггер

является универсальным.

соединен со входомD,

то с приходом тактового импульса Qn+1=Qn,

а в JK-триггере

при J=K=1

будет изменяться состояние выхода на

противоположное, и число импульсов на

выходе будет в два раза меньше, т. е.

такие структуры работают как T-триггеры.

На рис. 5.12 показана возможность

использования JK-триггера

в качестве D-триггера.

Таким образом, JK-триггер

является универсальным.

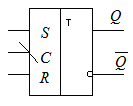

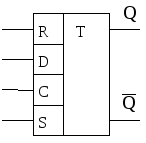

В серийных триггерах

для расширения их возможностей, кроме

информационных и синхронизирующих

входов, делаются установочные входы

(R,

S),

они позволяют делать предварительную

установку 0 или 1 на выходе

![]() ,

причем, как правило, эти входы являются

приоритетными. Кроме этого, реально

действующий информационный вход в

структуре триггера может быть конъюнкцией,

дизъюнкцией или какой-либо функцией

нескольких логических переменных,

действующих на информационных входах,

например:J=J1

J2

J3;

K=K1

K2

K3

и т. п. Обозначение таких триггеров

представлены на рис. 5.13.

,

причем, как правило, эти входы являются

приоритетными. Кроме этого, реально

действующий информационный вход в

структуре триггера может быть конъюнкцией,

дизъюнкцией или какой-либо функцией

нескольких логических переменных,

действующих на информационных входах,

например:J=J1

J2

J3;

K=K1

K2

K3

и т. п. Обозначение таких триггеров

представлены на рис. 5.13.

R D C S R C J T K

J23

K1

K2

K3 T

![]()

![]()

![]()

![]()

![]()

а б

Рис. 5.13 Триггеры с установочными входами:

а – D-триггер; б – универсальный JK-триггер