- •2.Косвенный переход

- •Дескрипторы

- •Основные характеристики тестов

- •Надёжность тестирования –

- •Однородное ранжирование

- •Ранжирование по методу Хаффмана

- •Формы представления чисел

- •Представление чисел с учетом знака

- •4.1. Сложение с плавающей точкой

- •4.2. Умножение мантисс чисел с плавающей точкой

- •Сложение чисел

- •Система команд

- •Интегральный таймер

- •Программируемый адаптер последовательного интерфейса

- •Схемы управления и защиты памяти

- •Разрядность обрабатываемых данных - 8; 16; 32

- •Разрядность обрабатываемых данных - 8; 16; 32

- •80486Dx – 32 разрядный процессор 80486 с встроенным сопроцессором

- •80486Sx -- 32 разрядный процессор 80486 без сопроцессора

- •80486Dx2 – частота cpu увеличена в 2 раза по сравнению с шиной.

- •80486Dx4 -- частота cpu увеличена в 2,5 (3) раза по сравнению с шиной.

- •Для увеличения объёма convention memory осуществляют перемещение dos, резидентных программ и драйверов в расширенную память.

- •Существуют две системы нумерации секторов на диске:

- •Pause [сообщение] -- приостановка выполнения bat-файла и выдача сообщения

- •73. Управление дисками и каталогами в ms-dos.

- •Триггеры с управлением по фронту

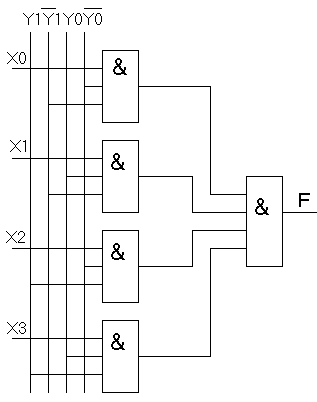

- •Приведена схема мультиплексора 4 в 1

- •После заполнения таблицы можно перейти к синтезу комбинационной схемы r- го вычислителя I – го разряда регистра.

- •2.1.2. Комбинаторная мера.

- •2.1.3. Аддитивная мера Хартли.

- •2.2.3. Условная энтропия.

- •2.2.4. Энтропия и информация.

- •3.2. Выбор частоты отсчётов при дискретизации.

- •3.3. Квантование по уровню.

- •Теорема 1

- •Теорема 2

- •4.4. Оптимальное кодирование.

- •Например: Дан восьмибуквенный первичный алфавит, известны безусловные вероятности для символов первичного алфавита.

- •4.6.2. Циклические коды.

- •1. Семантический разрыв между архитектурой эвм и уровнем решаемых задач

- •1.1. Физическая и виртуальная эвм

- •1.2. Семантический разрыв между физической и виртуальной эвм

- •1.3. Уменьшение семантического разрыва

- •1.4. Векторная обработка данных

- •2. Основы горизонтальной и вертикальной обработки информации

- •2.1. Характеристика горизонтальной и вертикальной технологий

- •2.2. Вертикальные операции и устройства

- •2.2.1. Операция вертикального сложения.

- •2.2.2. Операция деления количества единиц.

- •2.2.3. Операция упорядочения единиц.

- •2.2.4. Примеры выполнения вертикальных операций.

- •3. Использование матричного параллелизма в архитектуре эвм

- •3.1. Матричный параллелизм на системном уровне

- •3.1.1. Однородные матричные процессоры.

- •3.1.2. Периферийные матричные процессоры.

- •3.2. Матричный параллелизм на схемном уровне

- •3.2.1. Параллельные сдвигатели.

- •3.2.2. Параллельные сумматоры.

- •3.2.3. Матричные умножители

- •3.2.4. Матричные делители.

- •№114 Матричные системы

- •№117 Многомашинные системы

- •№121 Стандарт скоростной оптической магистрали fddi.

- •152. Принцип управления по хранимой микропрограмме. Операционно-адресная структура микрокоманды.

- •Основная задача свв – организация обменом информации между оп эвм и пу.

- •К основным функциям свв относят следующие:

- •166. Формирование речевых сообщений по правилам и по образцам. Способы сжатия информации в устройствах ввода-вывода речевых сообщений.

Приведена схема мультиплексора 4 в 1

С уществуют

мультиплексоры с третьим состоянием

на выходе, с их помощью можно производить

наращивание размерности мультиплексора

за счёт параллельного включения выходов

и использования адресных разрядов для

перевода мультиплексора в 3- е со

уществуют

мультиплексоры с третьим состоянием

на выходе, с их помощью можно производить

наращивание размерности мультиплексора

за счёт параллельного включения выходов

и использования адресных разрядов для

перевода мультиплексора в 3- е со

стояние.

Функция, выполняемая мультиплексором 2n1, по структуре полностью совпадает с СДНФ представления функций n переменных. Из этого следует, что любую переключательную функцию n переменных можно реализовать на мультиплексоре 2n1, подав на входы константы 0 или 1.

Пусть необходимо реализовать функцию F(x1,x2,x3,x4)=x1x2x3+x1x2x3+x2x3x4+x2x3x4+x1x3x4+x1x2x4 .

Таблица переходов:

|

X1X2X3X4 |

F |

Подкл. вход |

|

0 0 0 0 |

0 0 |

|

|

0 0 0 1 |

В1 | |

|

0 0 1 0 |

1 0 |

|

|

0 0 0 1 |

В2 | |

|

0 1 0 0 |

1 1 |

|

|

0 1 0 1 |

В3 | |

|

0 1 1 0 |

0 0 |

|

|

0 1 1 1 |

В4 | |

|

1 0 0 0 |

0 1 |

|

|

1 0 0 1 |

В5 | |

|

1 0 1 0 |

1 1 |

|

|

1 0 1 1 |

В6 | |

|

1 1 0 0 |

1 1 |

|

|

1 1 0 1 |

В7 | |

|

1 1 1 0 |

1 0 |

|

|

1 1 1 1 |

В8 |

В результате получим схему:

№ 88 Регистры

Регистрами наз. устройства, выполняющие функции фиксации, хранения и передачи информации. Информация хранится в регистре в виде кодового слова. Регистр состоит из разрядных схем, число которых соответствует разрядности обрабатываемых слов. В каждом разряде есть триггер и чаще всего ЛЭ. Регистр выполняет ряд МО над словами.

К 1 – й группе МО относятся МО, кот. связаны с приёмом слов, т.е. установка регистра в 0 или 1, либо приём слова.

Ко 2 – й группе относятся МО, связанные с выдачей слов в том или ином коде.

К 3 – й группе МО, относят МО, связанные с выполнением поразрядных логических операций над словами.

К 4 – й группе отнесём МО, связанные со сдвигом слов в разрядной сетке. Сдвиг либо вправо или влево, или циклический. Преобразование параллельного кода в последовательный код или наоборот.

Регистры можно классифицировать по ряду признаков:

по способу приёма и выдачи информации:

а) параллельные (статические)

б) последовательные (сдвиговые)

в) параллельно – последовательные

В регистрах типа а) приём и выдача слов производится по всем разрядам одновременно, их основная функция – хранение слов. В них могут выполняться также поразрядные операции над словами.

В регистрах типа б) слово принимается и выдаётся поразрядно. В них тактирующие сигналы перемещают записанное слово по разрядной сетке. Такие регистры могут быть нереверсивными либо реверсивными.

В регистрах типа в) слово записывается параллельно, а выдаётся последовательно или наоборот.

по количеству каналов передачи данных:

а) парофазные б) однофазные

В парофазных информация передаётся каждый бит по двум каналам, т.е. каждый разряд передаётся в виде прямого и инверсного значения переменной.

В однофазных – передаётся по одному каналу либо прямое либо инверсное значение.

по способу тактирования:

а) однотактные б) двух- или многотактные

Однотактные управляются одной последовательностью СИ. У двух- и многотактных каналов синхронизации два и больше, причём сдвинутые по фазе.

№89 Синтез МФР

Под МФР подразумевается регистр, способный выполнять некоторое множество МО над входными словами, а также, над словами, которые хранились в регистре до начала выполнения МО. В каждом маш. такте. регистр может выполнять только одну МО либо ни одной.

Кроме стандартного набора МО для обычного регистра, в МФР используются и другие МО, предусматривающие предварительную обработку (арифметическую и логическую) входных данных.

Для синтеза множество всех МО можно разбить на несколько подмножеств. Например, на подмножество МО в результате которых происходят изменения регистров. И подмножество в результате выполнения которых изменения в регистрах не происходят, но осуществляется передача в выходные шины кодов, которые зависят от содержимого регистров.

Т.о., МФР – это автомат с памятью, у которого входными являются переменные и множество МО, а выходными – множество выходных шин и признаки. Для синтеза такого автомата проводится его декомпозиция, крайним случаем которой является разбиение данного автомата на элементарные одноразрядные автоматы.

Для физической реализации некоторого сегмента достаточно рассмотреть синтез только одного разряда сегмента, для остальных разрядов решения тиражируются. Аналогично поступают и остальными сегментами.

Методика разбиения на сегменты основана на том, что поочерёдно рассматривается каждая МО, выполняемая МФР или шиной, при этом выявляются разряды регистра, которые выполняют одну и ту же функцию. Затем рассматривается вся совокупность МО и производится пересечение исходных сегментов: при этом образуются новые сегменты, которые также составляют разрядное поле МФР либо шины.

Регистр можно определить как электронный узел, состоящий из множества триггеров: в то же время это – автомат, предназначенный для выполнения некоторого набора МО. Регистры бывают синхронные и асинхронные.

СИ указывает, в какой момент времени необходимо выполнить операцию, тогда как управляющий сигнал показывает, что конкретно должен выполнить регистр.

Для синтеза КС, реализующей функцию возбуждения триггера, необходимо располагать следующей информацией:

описание МО

элементная база (тип триггера, логический базис и т.п.)

Далее составляются таблицы со столбцами вида:

с именем входных переменных

с именем переменной Q(t+1), значение которой будет запомнено данным триггером в момент t+1

с именем переменных (функций возбуждений), соответствующих информационным входам триггера.