- •Введение

- •1. Основы алгебры логики

- •1.1. Задание функций алгебры логики

- •1.2. Операции алгебры логики

- •1.2.1. Операция отрицание

- •1.2.3. Операция конъюнкция

- •1.2.4. Операция стрелка Пирса

- •1.2.5. Операция штрих Шеффера

- •1.2.6. Операция исключающее ИЛИ

- •1.2.7. Операция сложение по модулю два

- •1.2.8. Операция эквиваленция

- •1.2.9. Операция импликация

- •1.2.10. Операция запрет

- •1.2.11. Другие операции

- •1.3. Функционально полные системы

- •1.4. Свойства операций алгебры логики

- •1.4.1. Свойства операции отрицание

- •1.4.2. Свойства операций конъюнкция и дизъюнкция

- •1.4.3. Свойства операций штрих Шеффера и стрелка Пирса

- •1.4.4. Свойства остальных операций

- •1.5. Аналитическая запись функций алгебры логики

- •1.5.1. Дизъюнктивные нормальные формы

- •1.5.2. Конъюнктивные нормальные формы

- •1.6. Частично заданные функции

- •1.7. Упражнения

- •2. Логические элементы

- •3. МИНИМИЗАЦИЯ ФУНКЦИЙ АЛГЕБРЫ ЛОГИКИ

- •3.1. Метод Квайна

- •3.1.1. Алгоритм метода Квайна

- •3.1.2. Модернизация Мак-Класки метода Квайна

- •3.1.3. Модернизация Нельсона метода Квайна

- •3.1.4. Минимизация частично заданных функций методом Квайна

- •3.1.5. Упражнения

- •3.2. Метод карт Карно

- •3.2.1. Построение карт Карно

- •3.2.2. Минимизация с помощью карт Карно

- •3.2.3. Минимизация частично заданных функций картами Карно

- •3.2.4. Нахождение МКНФ

- •3.2.5. Упражнения

- •3.3. Совместная минимизация функций алгебры логики

- •3.3.1. Совместная минимизация методом общих простых импликант

- •3.3.2. Совместная минимизация методом доопределения частично заданных функций

- •3.3.3. Упражнения

- •4. Комбинационные схемы

- •4.1. Преобразователи кодов

- •4.1.1. Синтез преобразователей кодов

- •4.1.2. Схемы управления 7-сегментными индикаторами

- •4.1.3. Упражнения

- •4.2. Дешифраторы и шифраторы

- •4.2.1. Схемотехника построения дешифраторов

- •4.2.2. Схемотехника построения шифраторов

- •4.2.3. Применение дешифраторов и шифраторов

- •4.2.4. Упражнения

- •4.3. Мультиплексоры и демультиплексоры

- •4.3.1. Мультиплексоры

- •4.3.2. Синтез функций на мультиплексорах

- •4.3.3. Демультиплексоры

- •4.3.4. Упражнения

- •4.4. Сумматоры и схемы сравнения

- •4.4.1. Сумматоры

- •4.4.2. Схемы сравнения

- •4.4.3. Упражнения

- •5. Экспериментальная часть

- •5.1. Синтез и анализ схем с помощью лабораторного макета

- •5.1.1. Описание макета

- •5.1.2. Порядок синтеза и анализа схем

- •5.2. Синтез и анализ цифровых схем в Micro-Cap

- •5.2.1. Описание программы Micro-Cap

- •5.2.2. Синтез схем с помощью Micro-Cap

- •5.2.3. Анализ цифровых схем с помощью Micro-Cap

- •5.2.4. Порядок выполнения работы в Micro-Cap

- •5.3. Примерные задания лабораторных работ

- •6. Библиографический Список

Цифровая схемотехника

6. Построить схему дешифратора для 7-сегментного индикатора, отображающего не цифры, а буквы латинского алфавита: A, b, c, d, E, F, H, L, P, U. на двух дешифраторах 3-8 и элементах И-НЕ.

7.Составить таблицу истинности для приоритетного шифратора 8-3 с инверсными входами и выходами.

8.Построить схему шифратора 16-4 на двух шифраторах 8-3 с инверсными входами.

9.Построить схему шифратора 32-5 на шифраторах 8-3.

10.Построить схему преобразования кода Джонсона в двоичный код на дешифраторе и шифраторе.

11.Построить схему преобразования кода Грея в код Джонсона на дешифраторе и шифраторе.

4.3. Мультиплексоры и демультиплексоры

4.3.1. Мультиплексоры

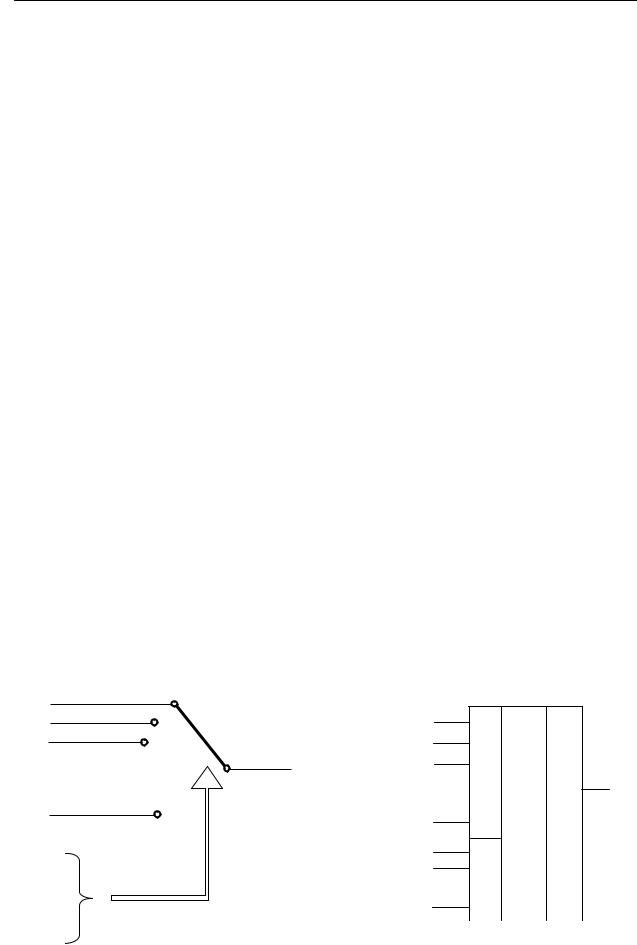

Мультиплексор – устройство, предназначенное для коммутации одного из нескольких входных сигналов на один выход. Мультиплексор является электронным аналогом механического переключателя, имеющего несколько входов и один выход (рис. 4.14а). Каждый из этих входов (обычно их обозначают D0 … Dn-1 и называют информационными входами) имеет свой номер (или адрес). Для выбора входного сигнала используются специальные адресные входы (a… ak-1), таким образом, с помощью k адресных входов можно выбрать один из n = 2k информационных входов и подключить его к выходу Q.

На рис. 4.14б приведено обозначение мультиплексора на схемах. Кроме информационных и адресных входов, мультиплексор может иметь прямой или инверсный вход разрешения (его обозначают V или C) и инверсный выход. Вместо надписи MUX в центральном поле прямоугольника может быть MS.

D0 |

|

|

|

D1 |

|

D0 |

MUX |

D2 |

|

D1 |

|

|

Q |

D2 |

|

|

|

|

|

… |

|

… |

Q |

Dn-1 |

|

Dn-1 |

|

|

|

|

|

a0 |

|

a0 |

|

|

a1 |

|

|

|

|

|

|

a1 |

|

… |

|

… |

|

ak-1 |

|

ak-1 |

а) |

|

б) |

|

|

||

|

|

Рис. 4.14 |

|

80

Комбинационные схемы

Мультиплексоры называют по числу имеющихся у них информационных входов. 2-входовый мультиплексор (рис. 4.15а) имеет один адресный вход. Если на него подан сигнал 0, то к выходу Q подключается вход D0 , а если 1 – вход D1 . В таблице истинности, описывающей работу мультиплексора, в столбцы аргументов обычно записывают адресные входы и вход разрешения, если он есть у данного мультиплексора, а в столбец выходной функции пишут имена входов, присоединенных при данном значении аргументов к выходу (табл. 4.11).

По таблице, описывающей работу мультиплексора, легко записать его функцию выхода:

Q = aD0 V aD1 |

(4.6) |

В одной микросхеме обычно размещают четыре таких мультиплексора. Они имеют общий адресный вход, который обозначают Ā/B. Информационные входы тоже обозначают по-другому: входы D0 этих четырех мультиплексоров называют соответственно A1 A2 A3 A4, а входы D1 – B1 B2 B3 B4 (рис. 4.15б). Если на адресный вход Ā/B подать 0, то к выходу Qi (где i = 1 ÷ 4) подключается вход Ai , а если 1 – вход Bi (табл. 4.12). Мультиплексор имеет инверсный вход разрешения, т.е., чтобы на выходах появились нужные сигналы, на него необходимо подать сигнал 0.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Табл. 4.11 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

Q |

|

|

||

|

|

|

|

|

|

|

|

|

|

A1 |

MUX |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

D0 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

A2 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

A3 |

|

Q1 |

|

|

|

1 |

|

|

D1 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D0 |

MUX |

|

|

|

|

|

|

|

A4 |

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

B1 |

|

Q3 |

|

|

|

|

|

|

Табл. 4.12 |

||||||

|

D1 |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

B2 |

|

Q4 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

a |

|

|

|

|

|

|

|

|

B3 |

|

|

|

|

V |

|

Ā/B |

|

Qi |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

B4 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

Ai |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

0 |

|

1 |

|

Bi |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

A/B |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

1 |

|

* |

|

0 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

б) |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Рис. 4.15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

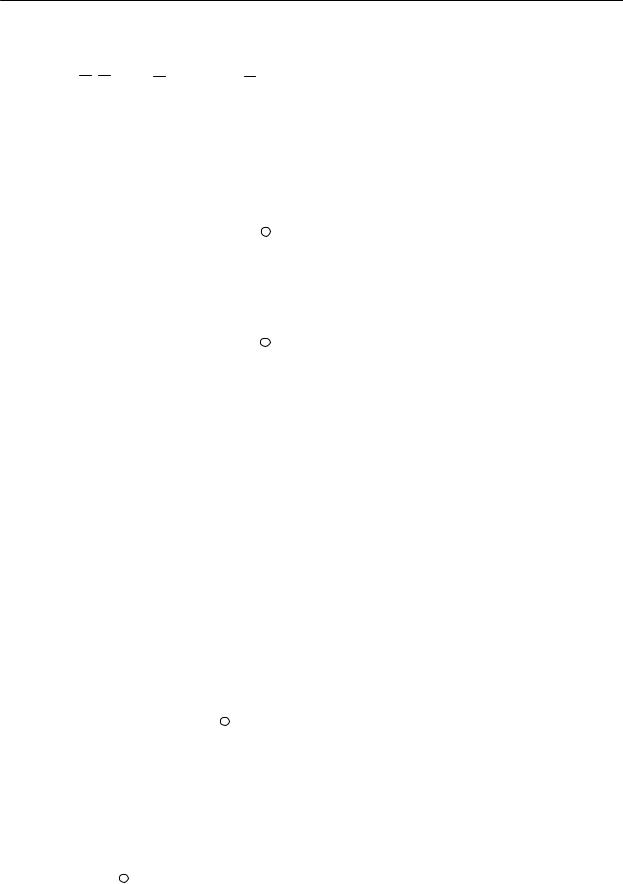

4-входовый мультиплексор (рис. 4.16а) имеет два адресных входа. В одной микросхеме обычно размещают два таких мультиплексора (рис. 4.16б). Они имеют общие адресные входы, которые обозначают a0 и a1 (где a0 – младший адресный вход). Подавая на адресные входы различные сигналы, можно подключить к выходам соответствующие

81

Цифровая схемотехника

информационные входы (см. табл. 4.13). Оба мультиплексора имеют вход разрешения. Функцию выхода также легко записать:

Q = a1a0D0 V a1a0D1 V a1a0D2 V a1a0D3 |

|

|

(4.7) |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Табл. 4.13 |

|||

|

|

|

|

|

|

|

|

D0 |

|

MUX |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

a1 |

|

a0 |

|

Q |

|

|

|

|

|

|

|

|

|

D2 |

|

|

Q |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

|

D0 |

||

|

D0 |

MUX |

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

|

D1 |

|||

|

D1 |

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D2 |

|

Q |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

|

D2 |

|

|

|

|

|

|

D0 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

1 |

|

D3 |

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

D2 |

|

|

Q |

|

|

1 |

* |

|

* |

|

0 |

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

a1 |

|

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

|

б) |

|

|

|

|

|

|

|||||

|

|

|

|

Рис. 4.16 |

|

|

|

|

|

|

|

|

|

|

|

||||

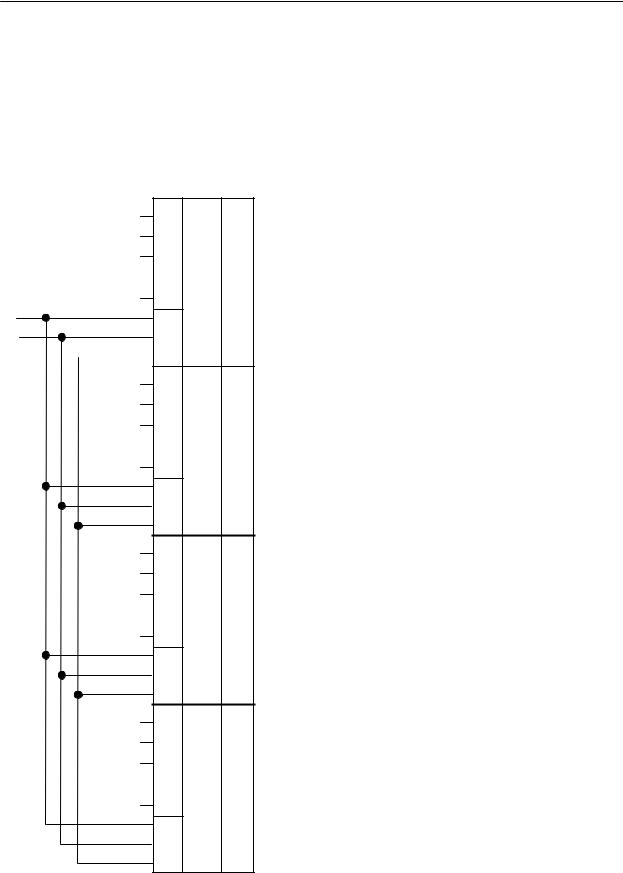

Следующий по сложности – 8-входовый мультиплексор с тремя адресными входами (рис. 4.18). Если на вход разрешения подан сигнал 0, к выходу Q подключается один из информационных входов D0 D7 в зависимости от сигналов на адресных входах (табл. 4.14).

|

|

|

|

|

|

|

|

|

|

|

Табл. 4.14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MUX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

a2 |

a1 |

a0 |

Q |

|

||

|

|

|

|

|

|

|||||||

|

|

D1 |

|

|

|

|

0 |

0 |

0 |

0 |

D0 |

|

|

|

|

|

|

|

|

||||||

|

|

D2 |

|

|

|

|

|

|||||

|

|

|

|

|

|

0 |

0 |

0 |

1 |

D1 |

|

|

|

|

|

|

|

|

|

||||||

|

|

D3 |

|

Q |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

0 |

0 |

1 |

0 |

D2 |

|

|||||

|

|

D4 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

0 |

0 |

1 |

1 |

D3 |

|

|

|

|

D5 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

|

|

D6 |

|

|

|

|

0 |

1 |

0 |

0 |

D4 |

|

|

|

|

|

|

|

|

||||||

|

|

D7 |

|

|

|

|

0 |

1 |

0 |

1 |

D5 |

|

|

|

|

|

|

|

|

||||||

|

|

a0 |

|

|

|

|

|

|||||

|

|

|

|

|

|

0 |

1 |

1 |

0 |

D6 |

|

|

|

|

|

|

|

|

|

||||||

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

D7 |

|

||

|

|

|

|

|

|

|

||||||

|

|

a2 |

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

* |

* |

* |

0 |

|

|

|

|

C |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.17

По таблице истинности мультиплексора запишем функцию выхода с учетом входа разрешения:

82

Комбинационные схемы

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q = C (a2a1a0D0 V |

a2a1a0D1 V a2a1a0D2 V a2a1a0D3 V |

(4.8) |

||||||||||||||||||||

|

|

a2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

a1a0D4 V a2a1a0D5 V a2a1a0D6 V a2a1a0D7 ) |

|

|||||||||||||||||||||

Мультиплексоры большего размера строятся чаще всего из описанных выше мультиплексоров меньшего размера. Например, для построения 32-входового мультиплексора нужно взять четыре 8- входовых и правильно скоммутировать их выходы (рис. 4.18).

D0

D1

D2

D7

a0 a1

a2

D8

D9

D10

D15

D16

D17

D18

D23

D24

D25

D26

D31

D0 MUX

D1

D2

…Q

D7 a0 a1

a2 D1

D0 MUX

D1

D2

…Q

D7 a0 a1

a2 D2

D0 MUX

D1

D2

…Q

D7 a0 a1

a2 D3

D0 MUX

D1

D2

…Q

D7 a0 a1

a2 D4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

MUX |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

D1 |

|

|

|

Q |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

D2 |

|

Q |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a3 |

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

a4 |

|

|

a1 |

D5 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.18

У 32-входового мультиплексора должно быть 5 адресных входов. Три из них, например, a0, a1, a2, подаем параллельно на адресные входы мультиплексоров D1 – D4, поэтому они будут работать синхронно.

83