- •1. СТАНОВЛЕНИЕ ТЕОРИИ АВТОМАТОВ

- •1.1. Взаимосвязь теории автоматов и других

- •1.2. Подходы к определению конечного автомата

- •1.3. Сущность метода "черного ящика"

- •1.4. Основные задачи теории автоматов

- •2. ФОРМАЛЬНАЯ КЛАССИФИКАЦИЯ АБСТРАКТНЫХ АВТОМАТОВ И ИХ МАТЕМАТИЧЕСКИЕ МОДЕЛИ

- •2.1. Словесные определения автоматов

- •2.2. Формальное определение абстрактного автомата

- •2.3. Формальная классификация автоматов

- •2.4. Математические модели автоматов

- •2.4.1. Модель Мили

- •2.4.2. Модель Мура

- •2.4.3. Модель совмещенного автомата (С-автомата)

- •2.4.4. Модель микропрограммного автомата

- •3. СТРУКТУРНЫЕ МОДЕЛИ ПЕРВОГО УРОВНЯ АБСТРАКТНЫХ АВТОМАТОВ

- •3.1. Структурная модель автомата Мили

- •3.2. Структурная модель автомата Мура

- •3.3. Структурная модель С-автомата

- •3.4. Структурная модель микропрограммного автомата

- •4. СПОСОБЫ ЗАДАНИЯ АБСТРАКТНЫХ И СТРУКТУРНЫХ АВТОМАТОВ

- •4.1. Начальные языки

- •4.1.1. Язык регулярных выражений алгебры событий

- •4.1.2. Язык логических схем

- •4.1.3. Язык граф – схем алгоритмов

- •4.2. Автоматные языки

- •4.2.1. Таблицы переходов и выходов

- •4.2.2. Матрицы переходов и выходов

- •4.2.3. Граф автомата

- •4.3.2. Язык временных диаграмм

- •5. Минимизация абстрактных автоматов

- •6. МАТЕМАТИЧЕСКИЕ ОСНОВЫ АЛГЕБРЫ ЛОГИКИ

- •6.1. Формальное определение алгебры логики

- •6.2. Аксиомы, теоремы и законы алгебры логики

- •6.2.1. Аксиомы алгебры логики

- •6.2.2. Теоремы алгебры логики

- •6.2.3. Законы алгебры логики

- •6.3. Основные понятия и определения

- •6.4. Формы представления логических функций

- •6.4.1. Словесная форма представления логических функций

- •6.4.2. Табличная форма представления логических функций

- •6.4.3. Аналитическая форма представления логических функций

- •7. Минимизация логических функций

- •7.1. Методы минимизации логических функций на основе прямых аналитических преобразований СДНФ

- •7.2. Метод испытания импликант

- •7.3. Визуальные методы минимизации логических функций

- •7.3.2. Метод минимизации частично определенных логических функций с помощью карт Карно

- •7.4. Машинно-ориентированные методы минимизации логических функций

- •7.5. Групповая минимизация системы логических функций

- •8. ФУНКЦИОНАЛЬНО ПОЛНЫЕ СИСТЕМЫ ЭЛЕМЕНТАРНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ

- •9. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •9.1. Программируемые логические матрицы

- •10. КОНЕЧНЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ

- •11. СИНТЕЗ И АНАЛИЗ ТИПОВЫХ КОМБИНАЦИОННЫХ АВТОМАТОВ

- •11.1. Шифратор (coder) и его синтез

- •11.2. Дешифратор и его синтез

- •11.3. Мультиплексор и его синтез

- •11.4. Синтез демультиплексора (распределителя)

- •12. Элементарные автоматы с памятью и их синтез

- •12.1. Понятие функционально полной системы элементарных автоматов

- •12.2. Разновидности триггеров

- •12.3. Обобщённая характеристика триггеров

- •12.4. Синтез однотактного асинхронного RS-триггера

- •12.4.1. Синхронный однотактный RS-триггер

- •12.5. Синхронный однотактный D-триггер

- •12.6.1. Принцип построения двухтактного триггера

- •12.6.2. Однотактный Т-триггер

- •12.6.3. Двухтактные Т-триггеры

- •12.7. Двухтактный JK-триггер

- •12.8. Двухтактные RS-триггеры и D-триггеры

- •Рис. 12.28. Синхронный двухтактный RS-триггер

- •Рис. 12.30. УГО синхронного двухтактного RS-триггера

- •БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- •Учебное издание

12.5. Синхронный однотактный D-триггер

Одним из способов устранения недостатка RSтриггеров – наличие запрещенных кодовых комбинаций входных сигналов - является построение еще одной разновидности триггерных схем, которая получила название D-триггер. Для управления синхронным однотактным RSтриггером необходимо три входных сигнала (два - информационных; один - управляющий). D-триггеры имеют один информационный D-вход и один управляющий вход – С. В D-триггерах запрещенные комбинации исключаются путем соединения через инвертор S и R входов синхронного RSтриггера. При этом на информационные входы RS-триггера никогда не поступают одинаковые сигналы, то есть исключаются запрещенные кодовые комбинации (S=R=1), а режим хранения (S=R=0) реализуется путем подачи на вход C нулевого уровня сигнала [25].

Значение сигнала на выходе Q D-триггера в момент времени (t+1) равно занчению сигнала на входе D в предыдещий момент врмени t. Таким образом, входной сигнал передается на выход с задержкой на один такт, то есть Qt +1 = Dt . Поэтому D-триггер называют триггером задержки.

Асинхронный D-триггер не применяется, так как его выход просто повторяет входной сигнал после окончания режима состязаний.

Синхронный D-триггер функционирует в соответствии с таблицей 12.6.

Из табл. 12.6 видно, что при отсутствии сигнала синхронизации (С=0) состояние триггера остается неизменным.

Для синтеза синхронного D-триггера воспользуемся асинхронным RS-триггером. Как видно из табл. 12.6, сигнал на входе D должен воздействовать на триггер только в том случае, когда имеется единичный уровень сигнала С. Следовательно, как и в случае синхронного RS-триггера, на

161

входе D-триггера должны быть двухвходовые элементы И, пропускающие сигнал с входа D при С=1.

Таблица 12.6

C |

D |

Q |

Q+ |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Рассмотри правую часть табл. 12.6. Переход триггера в состояние единицы должен происходить, когда на входах воздействуют сигналы С=1 и D=1. Значит, при таком сочетании сигналов на входе S асинхронного RS-триггера должен быть нуль, то есть S = C * D . Переход триггера в состояние нуля должен происходить, когда на входах имеется

комбинация C=1, D=0. Значит, на входе R асинхронного RSтриггера при таком сочетании сигналов также должен быть

нуль, то есть R =C * D . Поскольку сигнал на входе S формируется в момент, когда С=1, и соответствует инверсному значению D, его можно использовать для

формировнаия сигнала R , то есть R = C * S . Это же рассуждение можно получить и чисто формально с помощью алгебры логики:

R = C * S = C *C * D = C *(C D) = CC CD = CD

162

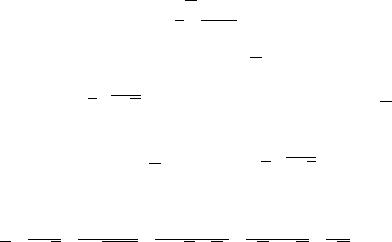

Следовательно, D-триггер может быть синтезирован на основе асинхронного RS-триггера [27], так как показано на рис. 12.13.

Уравнение однотактного асинхронного RS-триггера в элементном базисе И-НЕ имеет вид:

Q+ = S * R *Q

Если в этом уравнении произвести соответствующие нашим

рассуждениям |

замены переменных, |

то есть |

|

= |

|

, |

|||||||||||||||||||||||

S |

C * D |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

=C * |

|

, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

D |

то |

получим уравнение для однотактного |

|||||||||||||||||||||||||

синхронного D-триггера (12.7). |

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

Q+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= |

|

|

|

|

*C * |

|

|

*Q |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

C * D |

D |

(12.7) |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

& |

|

|

|

& |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

& |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 12.13. Синтезированный на основе RS-триггера

однотактный синхронный D-триггер

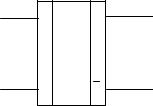

На рис. 12.14 представлено УГО однотактного синхронного D-триггера.

163

D T

Q

Q

C Q

Рис. 12.14. УГО однотактного синхронного D-триггера

Если на входе С синхронного D-триггера постоянно будет присутствовать логическая единица, то, принято говорить, что D-триггер становится «прозрачным». Этим хотят подчеркнуть то обстоятельство, что сигнал на выходе Q будет повторять значение сигнала на входе D.

12.6.Синтез Т-триггера

12.6.1.Принцип построения двухтактного триггера

Рассмотренные разновидности однотактных триггерных схем не позволяют реализовать так называемый режим счета (деление) входной тактовой частотой. Но именно данный режим работы триггерных схем является очень важным при построении различных вычислительных устройств.

При построении триггерных схем из обычных радиоэлектронных компонентов режим счета легко реализуется, так как очень просто построить дифференциирующие RC-цепи с требуемой постоянной времени, способной формировать очень короткие сигналы управления триггером. Однако в интегральной схемотехнике реализовывать дифференциирующую RCцепь экономически не выгодно. Именно данное обстоятельство потребовало построения специальных двухтактных триггерных схем.

Рассмотрим два сигнала на временной диаграмме.

164

a |

|

|

|

|

|

|

|

а= |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

t |

в |

|||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в=а |

||

в |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 12.15. Временная диаграмма сигналов a и в

Данные сигналы можно трактовать как различные сигналы, а можно понимать как один и тот же безинверсный и инверсный сигналы.

Данная особенность положена в основу работы двухтактных триггерных схем.

В [26] рассмотрен принцип построения двухтактного триггера, который называют также триггером типа MS (от англ. master, slave, что переводят обычно как «ведущий», «ведомый»). Его упрощенная структурная схема приведена на рис. 12.16. В схеме имеются два одноступенчатых триггера (ведущий M, ведомый S) и два электронных ключа (Кл1 и

Кл2).

Входные |

|

|

|

|

|

|

|

|

информа- |

|

|

|

|

|

|

Выходные |

|

ционные |

|

|

|

|

|

|

||

сигналы |

|

|

|

|

|

|

|

сигналы |

Кл1 |

|

М |

|

Кл2 |

S |

|||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

Рис. 12.16. Структурная схема двухтактного триггера

Временная диаграмма сигнала синхронизации, поясняющая работу триггера, приведена на рис. 12.17.

165

С |

|

|

|

|

||

|

|

|

b |

|

с |

|

|

|

|

|

|||

|

|

a |

|

|

d |

|

|

|

|

|

|||

0 |

|

|

|

|

|

t |

|

|

|

||||

|

ta |

tb |

|

tc td |

||

|

|

|

||||

Рис. 12.17. Временная диаграмма сигнала синхронизации

Рассмотрим ряд временных интервалов указанной диаграммы:

t < ta - ведущий триггер отключен от информационных

входов, ведомый триггер подключен к ведущему;

ta ≤ t ≤ tb - ведущий триггер отключен от информацион-

ных входов, ведомый триггер отключен от ведущего;

tb < t < tc - ведущий триггер подключен к информа-

ционным входам, ведомый триггер отключен от ведущего. В ведущий триггер записывается информация;

tc ≤ t ≤ td - ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

td < t - ведущий триггер отключен от информационных

входов, ведомый триггер подключен к ведущему; информация из ведущего триггера переписывается в ведомый. Это происходит сразу после момента времени td и означает, что фактически двухступенчатый триггер срабатывает при изменении сигнала синхронизации от 1 к 0. При этом выходные сигналы определяются теми входными информационными сигналами, которые имели место непосредственно перед отрицательным фронтом сигнала синхронизации.

166