- •1. СТАНОВЛЕНИЕ ТЕОРИИ АВТОМАТОВ

- •1.1. Взаимосвязь теории автоматов и других

- •1.2. Подходы к определению конечного автомата

- •1.3. Сущность метода "черного ящика"

- •1.4. Основные задачи теории автоматов

- •2. ФОРМАЛЬНАЯ КЛАССИФИКАЦИЯ АБСТРАКТНЫХ АВТОМАТОВ И ИХ МАТЕМАТИЧЕСКИЕ МОДЕЛИ

- •2.1. Словесные определения автоматов

- •2.2. Формальное определение абстрактного автомата

- •2.3. Формальная классификация автоматов

- •2.4. Математические модели автоматов

- •2.4.1. Модель Мили

- •2.4.2. Модель Мура

- •2.4.3. Модель совмещенного автомата (С-автомата)

- •2.4.4. Модель микропрограммного автомата

- •3. СТРУКТУРНЫЕ МОДЕЛИ ПЕРВОГО УРОВНЯ АБСТРАКТНЫХ АВТОМАТОВ

- •3.1. Структурная модель автомата Мили

- •3.2. Структурная модель автомата Мура

- •3.3. Структурная модель С-автомата

- •3.4. Структурная модель микропрограммного автомата

- •4. СПОСОБЫ ЗАДАНИЯ АБСТРАКТНЫХ И СТРУКТУРНЫХ АВТОМАТОВ

- •4.1. Начальные языки

- •4.1.1. Язык регулярных выражений алгебры событий

- •4.1.2. Язык логических схем

- •4.1.3. Язык граф – схем алгоритмов

- •4.2. Автоматные языки

- •4.2.1. Таблицы переходов и выходов

- •4.2.2. Матрицы переходов и выходов

- •4.2.3. Граф автомата

- •4.3.2. Язык временных диаграмм

- •5. Минимизация абстрактных автоматов

- •6. МАТЕМАТИЧЕСКИЕ ОСНОВЫ АЛГЕБРЫ ЛОГИКИ

- •6.1. Формальное определение алгебры логики

- •6.2. Аксиомы, теоремы и законы алгебры логики

- •6.2.1. Аксиомы алгебры логики

- •6.2.2. Теоремы алгебры логики

- •6.2.3. Законы алгебры логики

- •6.3. Основные понятия и определения

- •6.4. Формы представления логических функций

- •6.4.1. Словесная форма представления логических функций

- •6.4.2. Табличная форма представления логических функций

- •6.4.3. Аналитическая форма представления логических функций

- •7. Минимизация логических функций

- •7.1. Методы минимизации логических функций на основе прямых аналитических преобразований СДНФ

- •7.2. Метод испытания импликант

- •7.3. Визуальные методы минимизации логических функций

- •7.3.2. Метод минимизации частично определенных логических функций с помощью карт Карно

- •7.4. Машинно-ориентированные методы минимизации логических функций

- •7.5. Групповая минимизация системы логических функций

- •8. ФУНКЦИОНАЛЬНО ПОЛНЫЕ СИСТЕМЫ ЭЛЕМЕНТАРНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ

- •9. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •9.1. Программируемые логические матрицы

- •10. КОНЕЧНЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ

- •11. СИНТЕЗ И АНАЛИЗ ТИПОВЫХ КОМБИНАЦИОННЫХ АВТОМАТОВ

- •11.1. Шифратор (coder) и его синтез

- •11.2. Дешифратор и его синтез

- •11.3. Мультиплексор и его синтез

- •11.4. Синтез демультиплексора (распределителя)

- •12. Элементарные автоматы с памятью и их синтез

- •12.1. Понятие функционально полной системы элементарных автоматов

- •12.2. Разновидности триггеров

- •12.3. Обобщённая характеристика триггеров

- •12.4. Синтез однотактного асинхронного RS-триггера

- •12.4.1. Синхронный однотактный RS-триггер

- •12.5. Синхронный однотактный D-триггер

- •12.6.1. Принцип построения двухтактного триггера

- •12.6.2. Однотактный Т-триггер

- •12.6.3. Двухтактные Т-триггеры

- •12.7. Двухтактный JK-триггер

- •12.8. Двухтактные RS-триггеры и D-триггеры

- •Рис. 12.28. Синхронный двухтактный RS-триггер

- •Рис. 12.30. УГО синхронного двухтактного RS-триггера

- •БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- •Учебное издание

11. СИНТЕЗ И АНАЛИЗ ТИПОВЫХ КОМБИНАЦИОННЫХ АВТОМАТОВ

Комбинационным автоматом (автоматом без памяти) называется автомат, у которого множество состояний состоит

из одного элемента, т.е. A =1. Для такого автомата характерно

то, что функция переходов у него отсутствует. По этой причине выходной сигнал автомата без памяти зависит от комбинации логических значений входных переменных. Именно поэтому автомат называют комбинационным или автоматом без памяти.

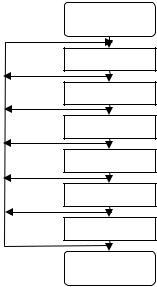

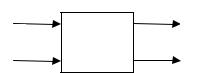

Комбинационный автомат называют также nkполюсником. Это обусловлено тем, что на уровне черного ящика автомат рассматривают как устройство имеющее n- входов и k-выходов. Если k=1, то автомат называется одновыходным, если k>1, то автомат называется многовыходным или k-выходным. Для различных комбинационных автоматов существуют и различные соотношения между n и k. Процедуру синтеза комбинационных автоматов можно охарактеризовать схемой алгоритма, представленной на рис. 11.1.

Каждый из блоков этой схемы представляет собой определенный этап синтеза комбинационного автомата:

1-ый – начало синтеза комбинационного автомата; 2-ой – на этом этапе комбинационный автомат пред-

ставляют на уровне черного ящика; 3-ий – словесное описание работы автомата;

4-ый – задание работы автомата в виде таблицы истинности; в случае необходимости происходит доопределение таблицы истинности;

5-ый – аналитическое описание работы автомата в виде СДНФ или СКНФ;

6-ой – минимизация аналитического описания работы автомата;

7-ой – синтез логической схемы автомата в заданном элементном базисе;

131

8-ой – конец синтеза комбинационного автомата.

В общем случае процесс синтеза комбинационного автомата является итерационным процессом, о чем свидетельствует наличие обратной связи в схеме алгоритма.

Рассмотрим типовые комбинационные автоматы и их синтез.

Начало

2

3

4

5

6

7

Конец

Рис. 11.1. Схема алгоритма, характеризующая процедуру синтеза комбинационного автомата

11.1. Шифратор (coder) и его синтез

Шифратор – это устройство, осуществляющее преобразование входного кода “1 из n” в k-разрядный позиционный выходной код.

Код “1 из n” часто называют унитарным кодом.

Если число входов шифратора равно 2n , то число выходов, очевидно, должно быть равным n, то есть числу разр я-

132

дов двоичного кода, которым можно закодировать 2n различных комбинаций.

Если в качестве позиционного кода использовать двоичный код, то между n и k должно иметь место следующее соотношение:

n = 2k , тогда k = ]log2 n[= int(log2 n + 0,5) , (11.1)

где ]x[- означает ближайшее целое, не меньше x. Рассчитаем по соотношению (11.1) значения k при n=2,3,4,5,6,7:

n |

k |

2 |

1 |

3 |

2 |

4 |

2 |

5 |

3 |

6 |

3 |

7 |

3 |

Синтезируем шифратор, преобразующий 10-ти разрядный унитарный код в двоичный код.

“1 из 10”→ 2k

1.Начало.

2.Представим шифратор на уровне черного ящика с детализацией его до входов и выходов.

x0 |

Шф. |

y0 |

|

… |

… |

||

|

|||

x9 |

|

y3 |

Рис. 11.2. Представление шифратора на уровне черного ящика

сдетализацией его до входов и выходов

3.При воздействии на вход шифратора каждого в отдельности входного сигнала, на его выходе должен формиро-

133

ваться соответствующий данному входному сигналу двоичный код.

4. Работа шифратора описывается четырьмя функциями y0, y1, y2, y3 , каждая из которых равна 1 на некоторых наборах, номер которых соответствует номеру входа шифратора. Составим таблицу истинности, отражающую закон функционирования шифратора (табл. 11.1).

Таблица 11.1

x9 |

x8 |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

y0 |

y1 |

y2 |

y3 |

№ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

од |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

1 |

|

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

1 |

|

|

0 |

0 |

1 |

0 |

2 |

|

|

|

|

|

|

1 |

|

|

|

0 |

0 |

1 |

1 |

3 |

|

|

|

|

|

1 |

|

|

|

|

0 |

1 |

0 |

0 |

4 |

|

|

|

|

1 |

|

|

|

|

|

0 |

1 |

0 |

1 |

5 |

|

|

|

1 |

|

|

|

|

|

|

0 |

1 |

1 |

0 |

6 |

|

|

1 |

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

7 |

|

1 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

8 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

9 |

5-6. Воспользовавшись табл. 11.1, |

составим СДНФ функ- |

ций выхода шифратора. |

|

y0 = x1 + x3 + x5 + x7 + x9 |

|

y1 = x2 + x3 + x6 + x7 |

(11.2) |

y2 = x4 + x5 + x6 + x7 |

|

y3 = x8 + x9 |

|

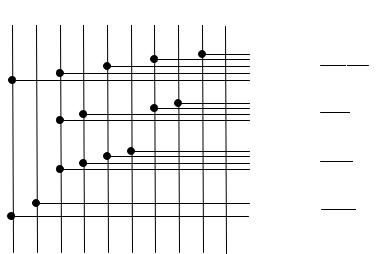

7. Синтезируем шифратор в элементном базисе И, ИЛИ, НЕ (рис. 11.3). Функции (11.2) реализуются четырьмя дизъ-

134

юнкторами, на выходах которых формируется четырехразрядный двоичный код.

x9 x8 x7 x6 x5 x4 x3 x2 x1 x0

|

|

y0 |

|

1 |

|||

|

|

||

|

|

y1 |

|

|

|

||

1 |

|||

|

|

||

|

|

y2 |

|

|

|

||

1 |

|||

|

|

||

|

|

|

|

y3 |

|

1 |

||

|

||

|

|

Рис. 11.3. Схема шифратора на 10 входов

8. Конец.

На рис. 11.3 аргумент x0 не входит ни в одну из логических функций и шина x0 остается незадействованной в схеме. Действительно, входному сигналу x0 должен соответствовать код “0000”, который сформируется на выходе шифратора, если все остальные аргументы будут равны 0.

Шифраторы широко применяются в системах управления технологическими процессами (“1” – включено и ”0” - выключено). Их применяют также для зашифровки адресов ячеек запоминающих устройств, высвечивания букв и цифр на мониторах, приоритетные шифраторы применяются при работе ЭВМ и других устройств, когда решается задача определения приоритетного претендента на обслуживание (высший приоритет – наибольший номер входа, низший – наименьший) [27].

135