- •0.Вступ

- •1. Математичні основи цифрової техніки

- •1.1 Відображення інформації у цифровій техніці

- •1.2 Перетворення числової інформації

- •1.3 Двійкова арифметика

- •1.4 Основні поняття та закони бульової алгебри

- •1.5 Властивості логічних функцій

- •1.6 Форми зображення логічних функцій

- •1.7 Мінімізація логічних функцій

- •1.8 Структурна реалізація логічних функцій

- •1.9Загальні відомості про цифрові автомати

- •1.10 Різновиди цифрових автоматів та особливості їх функціонування

- •1.11Загальні питання синтезу цифрових автоматів

- •2.Схемотехніка цифрових елементів

- •2.1 Види цифрових сигналів, та способи їх передачі

- •2.2 Класифікація цифрових елементів

- •2.3Основні характеристики та параметри цифрових мікросхем

- •2.4 Порівняльні характеристики цифрових мікросхем

- •2.5Схеми логічних елементів

- •2.6 Елементи з розширеними функціональними можливостями

- •2.6.1 Cинтезовані логічні елементи

- •2.6.2Логічні елементи з відкритим колектором

- •2.6.3Тристановий драйвер

- •2.7 Інтерфейсні мікросхеми

- •2.8Узгоджувачі рівнів

- •2.9 Завадостійкість цифрових пристроїв

- •2.10 Імпульсні схеми на цифрових елементах

- •2.10.1 Формувачі

- •2.10.2Генератори

- •3.Пристрої для перетворення цифрової інформації

- •3.1Шифратори та дешифратори

- •3.2Мультиплексори та демультиплексори

- •3.3Синтез комбінаційних пристроїв на дешифраторах

- •3.4Синтез комбінаційних пристроїв на мультиплексорах

- •3.5Перетворювачі кодів

- •3.6Арифметичні пристрої

- •3.6.1Арифметичні суматори

- •3.6.2Цифрові компаратори

- •3.6.3Арифметико-логічні пристрої

- •3.6.4Програмовані логічні матриці

- •Контрольні запитання по розділу

- •4.Послідовнісні пристрої

- •4.1Особливості функціонування послідовнісних пристроїв

- •4.2Особливості синтезу послідовнісних пристроїв

- •4.3Тригер – найпростіший зaпам’ятовувальний пристрій

- •4.3.1Загальна структура та класифікація тригерів

- •4.3.2Рiзновиди тригерів

- •4.4 Регістри

- •4.4.1 Регістри пам’яті

- •4.4.2Регістри зсуву

- •4.5 Лічильники

- •4.5.1 Класифікація лічильників

- •4.5.2Лічильники з послідовним переносом

- •4.5.3Реверсивні лічильники

- •4.5.4Лічильники з довільним модулем лічби

- •4.5.5Кільцеві лічильники та лічильники Джонсона

- •4.6Контрольні запитання по розділу

- •5.Інтегральні запам'ятовувальні пристрої

- •5.1Загальні відомості

- •5.2Оперативні запам'ятовуючі пристрої

- •5.2.1Статичні запам'ятовувачі віс озп

- •5.2.2Динамічні запам'ятовувачі віс озп

- •5.2.3Принцип побудови і структура віс озп

- •5.3 Принцип побудови і структура пзп

- •5.4Електрично перепрограмовувані пзп

3.6.2Цифрові компаратори

Це арифметичні пристрої, що призначені для порівняння величин двох чисел, що подані у двійковому (двійково-десятковому) коді1. Найпростіший компаратор виявляє лише факт рівності або нерівності двох поданих на його входи n-розрядних чисел (операндів) А і В і формує на виході однобітовий сигнал. рівності (1) або нерівності (0) цих чисел. Слід зауважити відмінність цих пристроїв від аналогових компараторів, які порівнюють рівні напруг на їх входах, і за принципом дії є модифікованими операційними підсилювачами. Тому надалі розлядатимемо тільки цифрові компаратори.

Рівність, зокрема, двох однорозрядних операндів a і b визначається логічною операцією рівнозначності (див.у табл. 1.5 функцію f9):

![]()

![]()

![]()

тобто логічною операцією виняткове АБО-НЕ, яка реалізується суматором-інвертором за модулем 2. Синтез однорозрядного компаратора рівності досить просто здійснюється у довільному базисі.

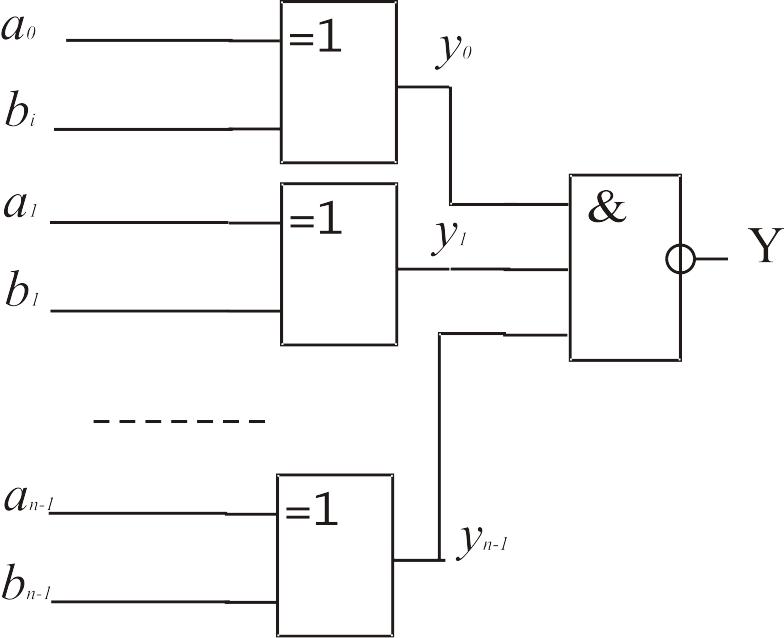

Порозрядну рівиість n -розрядних операндів найпростіше реалізувати за допомогою суматорів-інверторів за модулем 2 і кон’юнкторів, як це показано на рис. 3.13. Такий компаратор рівності порівнює окремі розряди n -розрядних чисел за формулою:

![]() ( 3.0 )

( 3.0 )

Аналогічний результат одержується й при синтезі компаратора у базисі суматорів за модулем 2 та диз’юнктора. Якшо застосувати закои дуальності, вихідна функція такого компаратора описуватиметься виразом

![]() (

3.0)

(

3.0)

Компаратори порівняння n-розрядних

чисел можна будувати за двома принципами

логічним та

арифметичним. Перший принцип (логічний)

базується на синтезі за таблицею

істинності, другий (арифметичний)

на с

Рис. 3.39

Визначник A=B

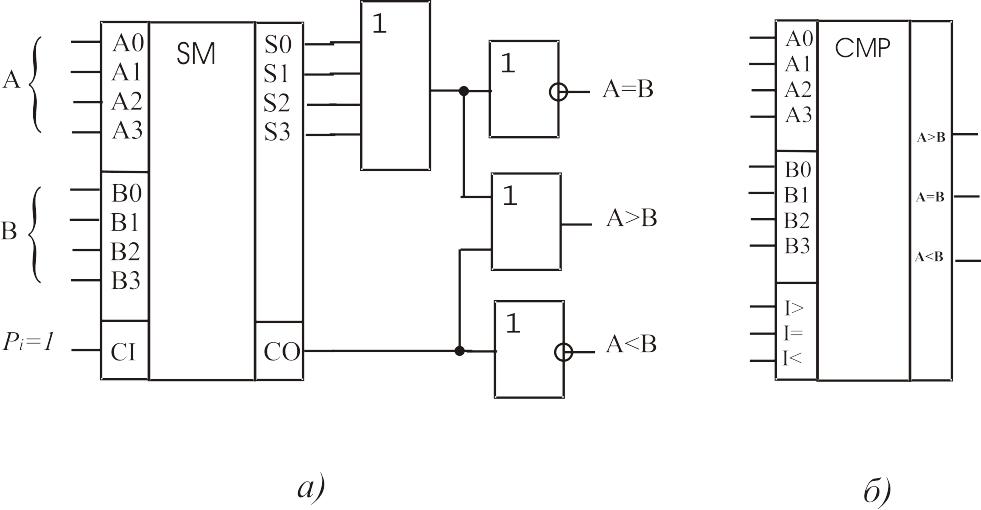

Промисловість випускає цифрові багаторозрядні компаратори як окремі вироби. Це в основному мікросхеми чотирирозрядних компараторів ТТЛШ К555СП1, 531СП1 і КМОН 564ИП2, 561ИП2, які мають, вбудовані інвертори для операнда В і додаткові три входи аналізу І>(А>B), I=(A=B), І<(А<В) (див. рис. 3.14.б). Останні призначені для утворення схеми нарощування розрядності операндів, тобто для каскадування послідовним або пірамідальним способом під’єднання однотипних мікросхем.

Рис. 3.40 Арифметичний принцип порівняння та позначення цифрового компаратора

3.6.3Арифметико-логічні пристрої

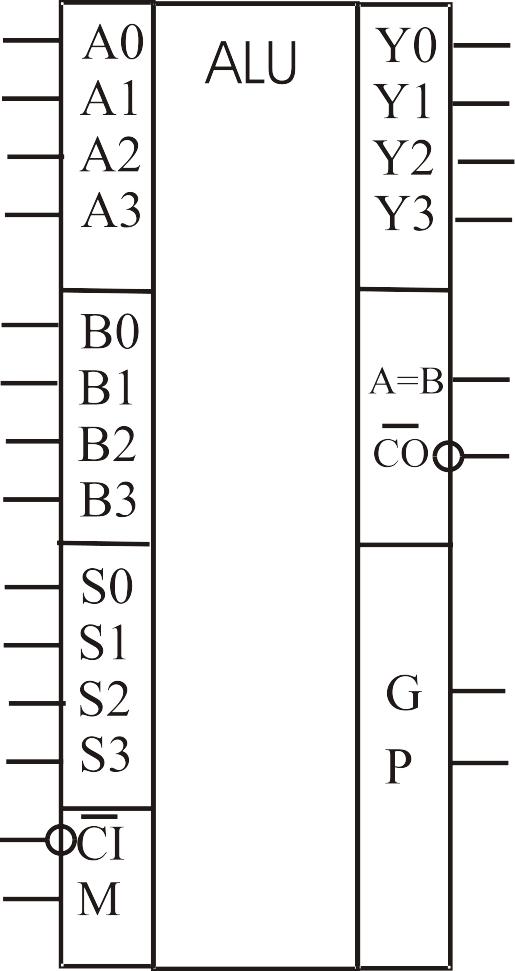

Дня виконання над оперендами А і B як арифметичних, так і логічних операцій доцільно застосовувати мікросхеми універсальних арифметично-логічних пристроїв (АЛП), які можна знайти у складі серій ТТЛ і КМОН. Найчастіше вони мають чотирирозрядні входи операндів А і В і придатні для нарощування їх розрядності. Для виконання тих чи інших логічних або арифметичних операцій служать спеціальні керуючі входи. Подаючи на них чотирирозрядний код і задавши тип операції (арифметичної чи логічної), можна виконати за допомогою мікросхеми одну з 16 арифметичних або одну з 16 логічних операцій. Через широкі функціональні можливості мікросхеми АЛП входять до складу мікропроцесорів ЕОМ. У комплекті з АЛП випускають ще мікросхему, яка являє собою тракт групового переносу ддя виконання прискореного підсумовування багаторозрядних чисел. Самі АЛП при цьому відіграють роль чотирирозрядних груп, оскільки в основному промисловістю випускаються чотирирозрядні АЛП. До таких мікросхем АЛП належать із серій ТТЛ КІ55ИП3 (із схемою прискореного переносу К155ИП4), із серій КМОН 564ИП3 (відповідно 564ИП4). Для виконання більш складних за алгоритмом арифметичних та логічних операцій застосовують мікропроцесорні ВІС.

Рис. 3.41 Позначення ІС арифметико-логічного пристрою

Мікросхеми АЛП (К155ИП3 і 564ИП3) це комбінаційні логічні схеми, що можуть виконувати арифметичні та логічні операції над чотирирозрядними операндами А і B з урахуванням або без урахування переносу Pi. На рис.3.15 зображене умовне схемне позначення мікросхеми АЛП* К564ИП3, яка функціонує згідно з табл. 3.5 (для випадку активних високих рівнів ([34]. АЛП для слів мав чотири пари входів А0-А3 і В0-В3 і чотири виходи Y0 –Y3, на яких фіксується результат арифметичної (при М=0) або логічної (при М=1) операції. Потрібну операцію (арифметичну чи логічну) вибирають за допомогою коду на входах S0 – S3.

Таблиця 3.14 Режими функціонування АЛУ типу К564ИП3

S3 |

S2 |

S1 |

S0 |

M=1 |

M=0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

1 |

|

|

0 |

0 |

1 |

0 |

|

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

|

|

0 |

1 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

|

|

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

|

|

1 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

0 |

|

|

1 |

1 |

1 |

1 |

|

|