- •Лабораторна робота 1 Знайомство з аналоговою комп’ютерною лабораторією схемотехніки

- •2. Порядок роботи:

- •2.1. Робота з мультиметром

- •2.2. Робота з генератором та осцилографом

- •Лабораторна робота 2 Методи та обладнання для дослідження частотних характеристик електричних кіл

- •2. Порядок роботи:

- •Лабораторна робота 3 Дослідження перехідних процесів у електричних колах постійного струму

- •2. Порядок роботи:

- •Лабораторна робота 4 Дослідження діодних випрямлячів змінного струму

- •2. Порядок роботи

- •Т аблиця 4.1

- •2. Порядок роботи

- •Т аблиця 5.1

- •Т аблиця 5.2.

- •Дослідження польового транзистора

- •Т аблиця 5.3

- •Т аблиця 5.4

- •Дослідження однокаскадних підсилювачів

- •Р ис. 5.6. Схема дослідження однокаскадного підсилювача на біполярному транзисторі т аблиця 5.5

- •Дослідження двокаскадного підсилювача

- •Лабораторна робота 6 Дослідження операційних підсилювачів і генераторів на їх основі

- •2. Порядок роботи

- •Т аблиця 6.1

- •Лабораторна робота 7 Ключовий режим роботи транзисторів. Логічні інвертори

- •Р ис. 7.1. Схема дослідження ключового режиму бінарного транзистора

- •Т аблиця 7.1 т аблиця 7.2

- •Т аблиця 7.4

- •Т аблиця 7.5

- •Т аблиця 7.6

- •Т аблиця 7.7

- •Лабораторна робота 8 Схемотехніка базових логічних елементів

- •2. Порядок роботи

- •Р ис. 8.4. Логічна схема “nand” у логіці кмоп

- •Лабораторна робота 9 Алгебра логіки та еквівалентні перетворювання логічних схем

- •2. Порядок роботи Дослідження базових логічних функцій і елементів

- •Дослідження похідних логічних функцій

- •Дослідження логічних схем

- •Лабораторна робота 10 Тригери та їх застосування у схемах бінарних лічильників

- •2. Порядок роботи: Дослідження схем тригерів

- •Дослідження бінарних лічильних схем

- •2. Порядок роботи

- •Дослідження елементів запам’ятовуючих пристроїв

- •Т аблиця 12.1

- •Дослідження дешифраторів

- •Дослідження транскодера

- •Т аблиця 12.2. Дослідження демультиплексора

- •Дослідження мультиплексора

Лабораторна робота 10 Тригери та їх застосування у схемах бінарних лічильників

1. Мета роботи: ознайомитись з принципами побудови та функціонуванням базових тригерів; опанувати методами складання схем двійкових лічильників з різними коефіцієнтами перерахунку.

2. Порядок роботи: Дослідження схем тригерів

2.1.

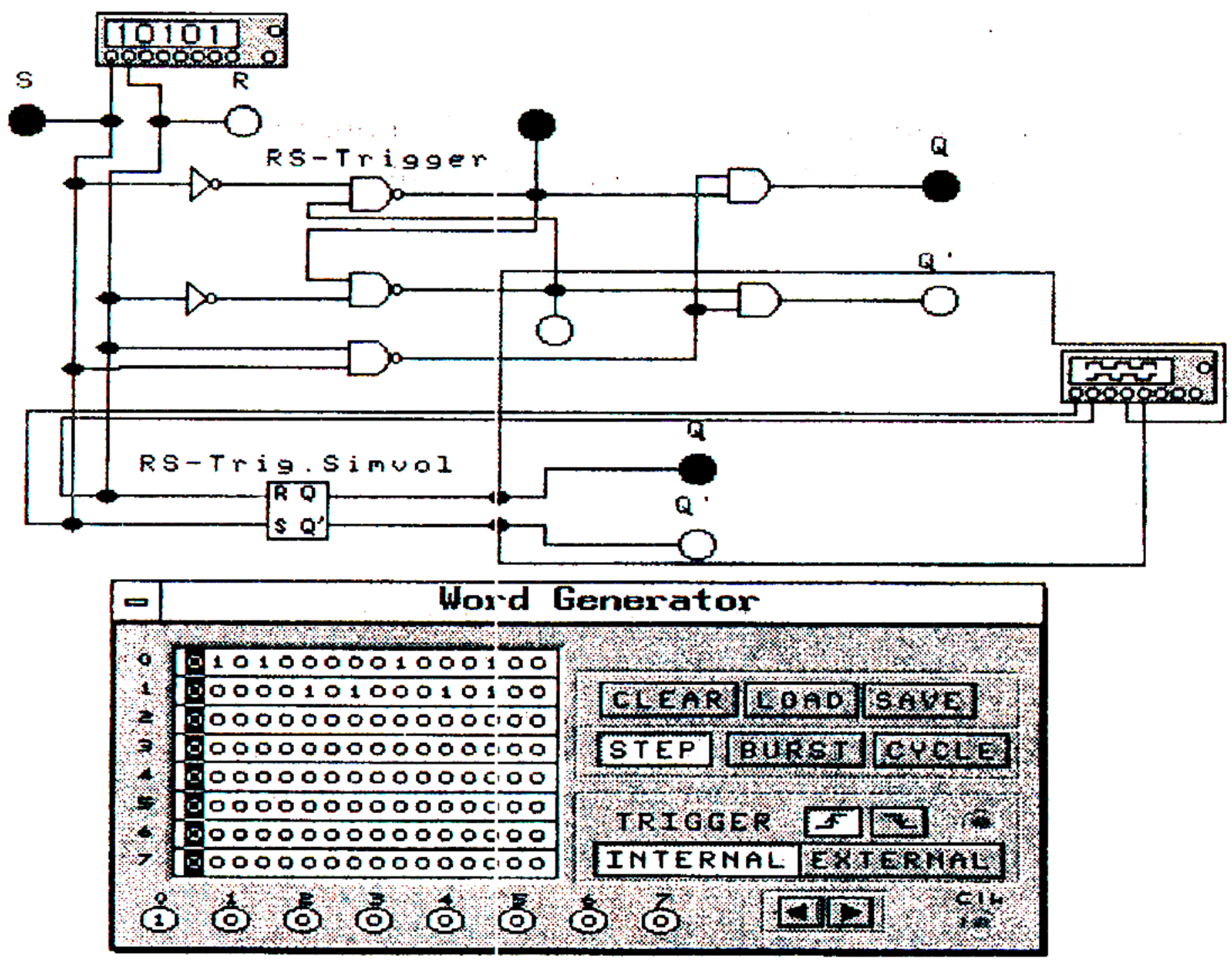

Зібрати схему досліджень RS-тригера

(Рис.

10.1).

2.1.

Зібрати схему досліджень RS-тригера

(Рис.

10.1).

Рис. 10.1. Схема дослідження RS-тригера та його умовне позначення

2.2. Запрограмувати генератор бінарних слів (див. Рис. 10.1). Відкрити лицеву панель аналізатора логічних рівнів (багатоканального осцилографа) і накреслити осцилограми напруг на входах R- і S- тригера, а також на його прямому (Q) та інверсному (Q’) виходах (у лабораторії цей осцилограф має назву “Analisateur logique”). Визначити, який із входів встановлює тригер у стан “1” чи у стан “0”? Визначити також, на якому фронті вхідного сигналу (зростаючому або спадаючому) здійснюється зміна станів тригера? Який ефект викликає подача логічної “1” на вхід S, якщо тригер знаходиться у стані “1”, а також подача логічної “1” на вхід R, якщо тригер знаходиться у стані “0”? Пояснити роль схем збігання “AND” на виходах тригера.

2.3.

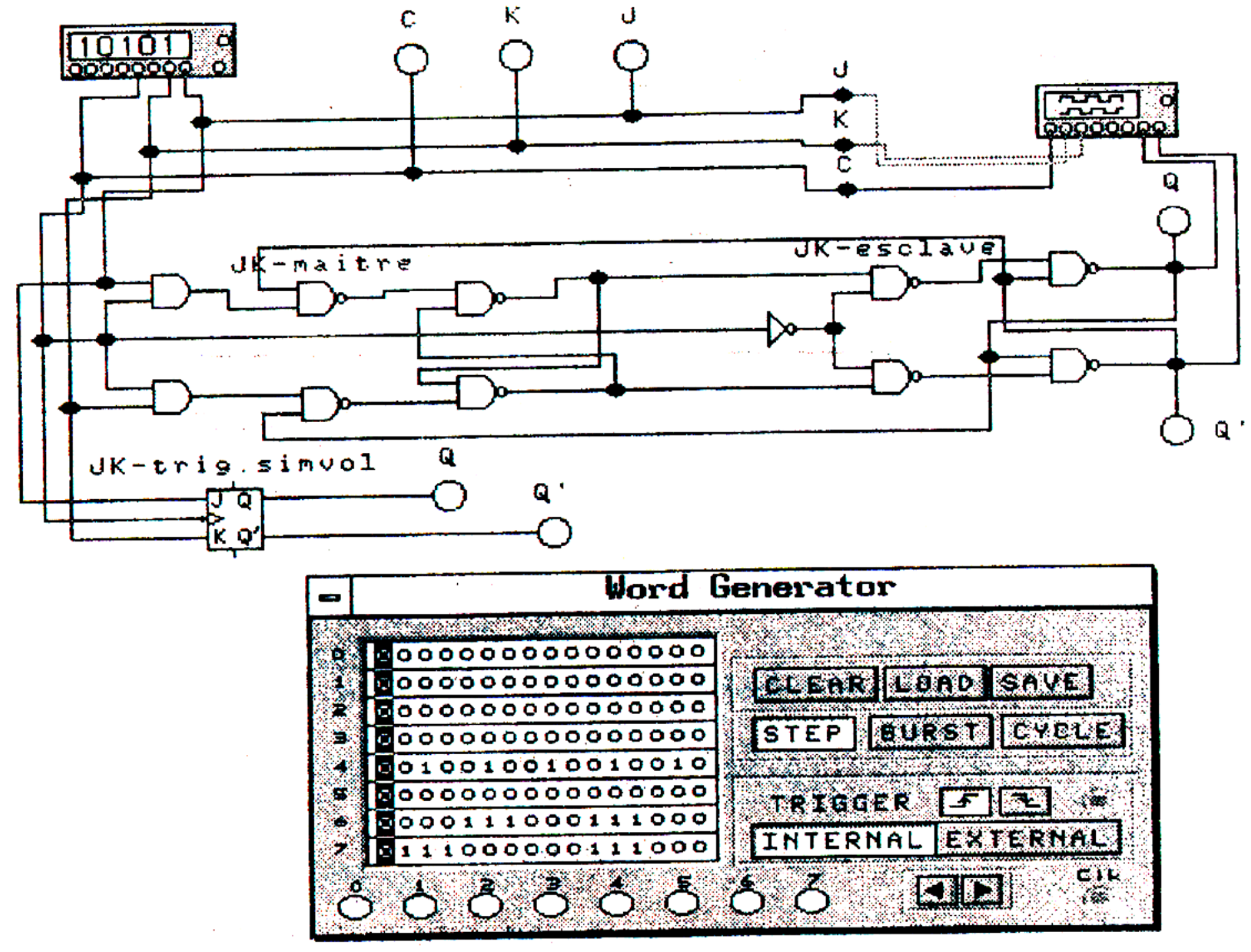

Зібрати схему досліджень двокаскадного

JK-тригера

(тригер “maitreesclave”)

(Рис.

10.2).

2.3.

Зібрати схему досліджень двокаскадного

JK-тригера

(тригер “maitreesclave”)

(Рис.

10.2).

Рис. 10.2. Схема дослідження JK-тригера та його умовне позначення

2.4. Повторити дії згідно п.2.2. для JK-тригера. Визначити, яка відмінність у роботі JK-тригера стосовно RS-тригера, враховуючи необхідність подачі на вхід JK-тригера синхронізуючого імпульсу “C”? Визначити також, при якому фронті імпульсу “C” здійснюється зміна станів двокаскадного JK-тригера і чому?

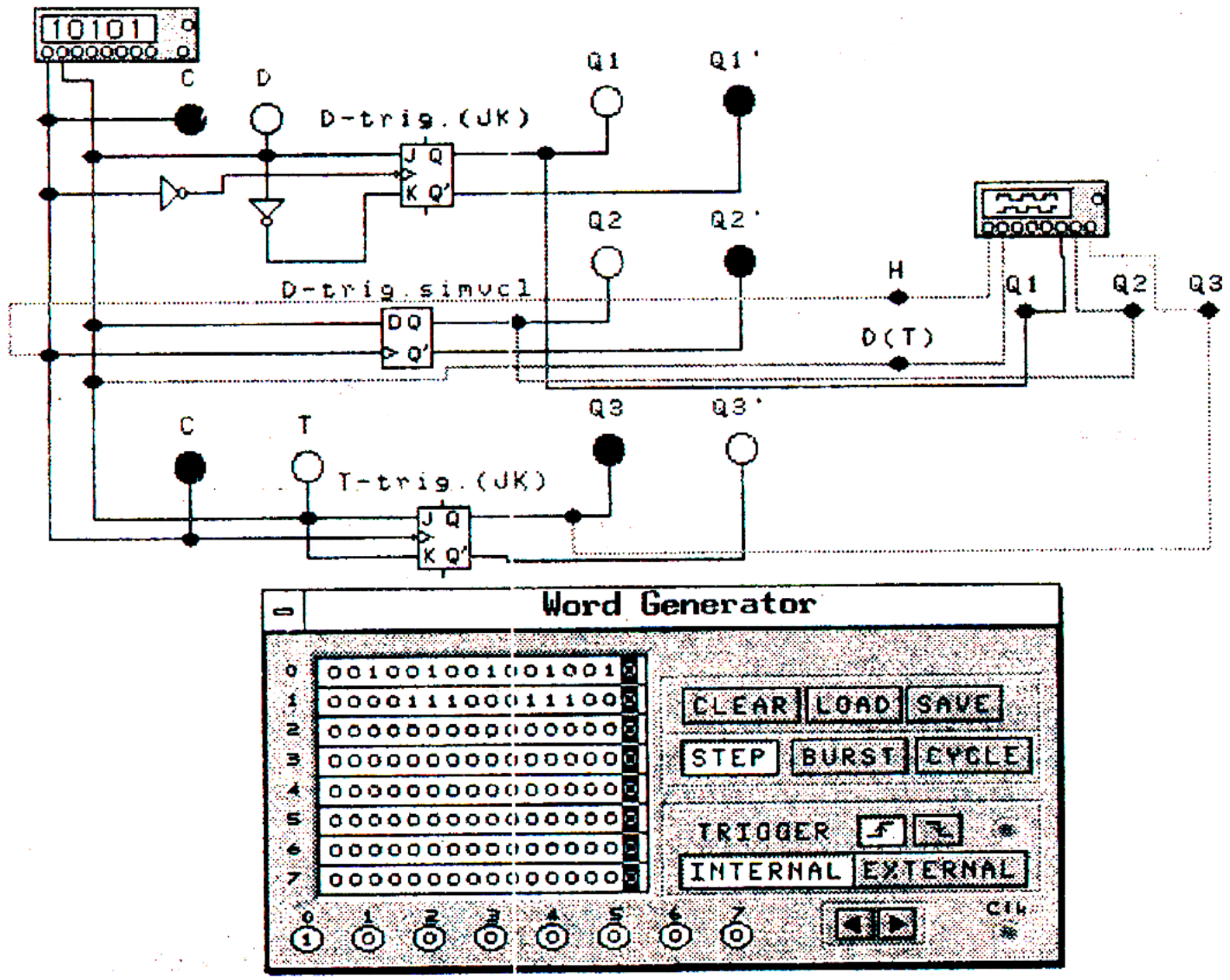

2.5. Використовуючи схему стандартного JK-тригера, що знаходиться в магазині лабораторії, реалізувати схеми D- і T-тригерів (Рис. 10.3.).

2.6. Повторити дії згідно п. 2.2. для D- і T-тригерів. Визначити, яка відмінність в роботі D- і T-тригерів стосовно RS- і JK-тригерів? Визначити також, при якому фронті імпульсу “C” здійснюється зміна станів D- і T-тригерів? Довести, що D-тригер змінює свій стан від зростаючого фронту імпульсу “C” і його стан завжди відповідає логічному рівні на його вході D. T-тригер змінює свій стан від кожного вхідного імпульсу “C”, але лише за наявності логічного рівня “1” на його вході T, що зветься “Enable” (дозволяння). Такий режим роботи T-тригера часто зветься лічильним режимом роботи. Зазначимо, що при логічному рівні “0” на вході T-тригер зберігає останній стан, в якому він був встановлений раніше.

Рис. 10.3. Схеми дослідження й умовні позначення D- і Т-тригерів

Дослідження бінарних лічильних схем

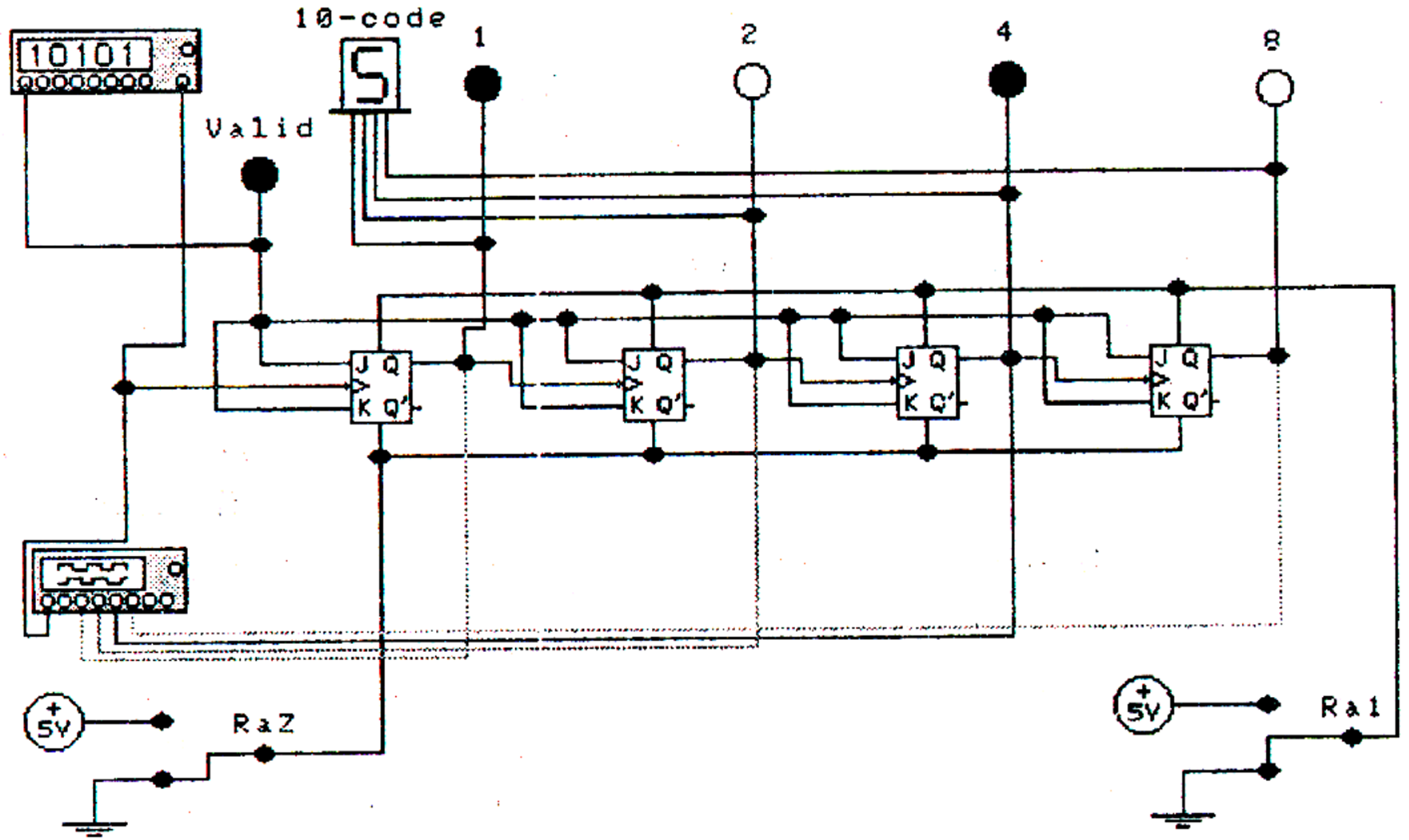

2 .7.

Зібрати схему підсумовуючого двійкового

(бінарного) лічильника на 4 двійкових

розряди (Рис.

10.4).

У запропонованій схемі крім звичайної

двійкової інформації станів кожного

тригера застосована десяткова індикація

станів лічильника, що дає змогу порівнювати

двійкову та десяткову інформації. У

схемі також застосовані входи попередньої

установки тригерів в стан “1” або “0”

(Ra1

або

RaZ

відповідно).

.7.

Зібрати схему підсумовуючого двійкового

(бінарного) лічильника на 4 двійкових

розряди (Рис.

10.4).

У запропонованій схемі крім звичайної

двійкової інформації станів кожного

тригера застосована десяткова індикація

станів лічильника, що дає змогу порівнювати

двійкову та десяткову інформації. У

схемі також застосовані входи попередньої

установки тригерів в стан “1” або “0”

(Ra1

або

RaZ

відповідно).

Рис. 10.4. Схема дослідження бінарного лічильника імпульсів

2.8. Після програмування генератора слів (Рис. 10.4.) встановити початковий стан лічильника “0,0,0,0” шляхом подачі “1” на його вхід RaZ, потім перевірити роботу схеми за наявності та за відсутності дозволяючого сигналу на вході “Valide”, що відповідає сигналу “Enable” у схемах T-тригера. Після чергової зміни станів лічильника щоразу перевіряти показання двійкової та десяткової інформації станів та їх відповідність кількості поданих на його вхід імпульсів. Визначити максимальну ємність 4-розрядного лічильника. Як вона зміниться при послідовному підключенні ще двох тригерів? Чому в підсумовуючому лічильнику чергова зміна стану наступного тригера відбувається при зміні стану попереднього саме з “1” на “0”?

2.9. Активізувати лицеву панель осцилографа і отримати осцилограми змін напруги на прямих виходах кожного тригера і на їх інверсних виходах. Пояснити відповідність та розбіжність сигналів на прямих та інверсних виходах.

2.10. При будь-якому стані лічильника, що відрізняється від стану “1,1,1,1”, подати логічну “1” на вхід Ra1 і перевірити ефект дії цього сигналу.

2.11. Входи C другого, третього та четвертого тригерів відключити від прямих виходів попередніх і підключити їх до відповідних інверсних виходів. Після виконання робіт, що передбачені п.2.8. і 2.9., довести, що отримана схема є схемою віднімаючого лічильника. На відміну від попередньої схеми перед початком підрахунку імпульсів цю схему слід встановити в попередній стан “1,1,1,1” з використанням входу Ra1. Пояснити, яким чином забезпечується у віднімаючому лічильнику чергова зміна стану наступного тригера при зміні стану попереднього саме з “0” на “1”?

2.12. Відкрити

файл “revcompt.cd3”,

що дає змогу перевірити роботу лічильника

в реверсивному режимі (Рис.

10.5).

2.12. Відкрити

файл “revcompt.cd3”,

що дає змогу перевірити роботу лічильника

в реверсивному режимі (Рис.

10.5).

Рис. 10.5. Схема реверсивного лічильника імпульсів

2.13. Накреслити схему, пояснити призначення кожної з логічних схем “І” та “АБО”. Змінюючи послідовно стан перемикача “Operation” з “+” на “–“, перевірити роботу схеми в режимах додавання або віднімання кількості вхідних імпульсів.

Примітка: перед початком кожної операції встановлювати відповідний початковий стан лічильника: “0,0,0,0” при додаванні і навпаки – при відніманні.

14. Відкрити файл “99compt.cd3”, що моделює схему “bcdcnt” (Рис. 10.6), яка дає змогу здійснювати підсумовування імпульсів у двійково-десятковому коді, коли кожен десятковий розряд зображений у двійковому коді. Це можливо лише при реалізації двійкового лічильника з ємністю 10 (від 0 до 9).

Рис. 10.6. Схема двійково-десяткового лічильника

2.15. Активізувати схему і перевірити її роботу в режимах “CYCLE” і “STEP”. Накреслити схему одної декади і пояснити призначення кожного елемента схеми. Збільшити ємність лічильника до 999.

2.16. Застосовуючи принцип аналогії, зібрати схему перерахунку секундних імпульсів у хвилині (тобто реалізувати лічильник з коефіцієнтом перерахунку, що дорівнює 60). Застосовуючи десяткові індикатори, довести коректність роботи схеми підрахунку секунд.

2.17. Скласти схему підсумовуючого лічильника з паралельним переносом його станів розрядів (Рис. 10.7). Після реалізації режиму “STEP” генератору слів простежити алгоритм роботи лічильної схеми, використовуючи для цього індикатори логічних рівнів та відповідні показання цифрового індикатора, що має бути підключеним до виходів схеми.

Рис. 10.7. Схема дослідження роботи двійкового лічильника з паралельним переносом

Відкрити лицеву панель осцилографа і зняти осцилограми напруг на вході лічильника, на шині “Valid”, а також на кожному розрядному виході.

Пояснити:

вплив рівня сигналу “Valid” на роботу схеми;

відмінність в алгоритмах роботи асинхронного послідовного лічильника й лічильника з паралельним переносом;

чому лічильна схема не працює, якщо перед початком роботи вона встановлена у стан, що відповідає числовому еквівалентові, більшому за 9? У зв’язку з цим пояснити необхідність застосування входу “RaZ”.

Розрахувати максимальну частоту вхідних імпульсів для 8-розрядних лічильників обох типів, якщо інтервал часу зміни стану тригера становить 1·10-6 s, а швидкодія одної логічної схеми – у середньому 1·10-7 s.

3. Зміст звіту

Зміст має містити:

Мету роботи;

схеми кожного з розглянутих тригерів, їх умовні позначення і осцилограми, що доводять принцип їх функціонування;

схеми всіх розглянутих лічильників і осцилограми, що доводять принцип їх функціонування.

Лабораторна робота 11

Регістри для запам’ятовування та перетворювання бінарних кодів.

Елементи запам’ятовуючих пристроїв

1. Мета роботи: ознайомитись з принципами побудови та функціонуванням запам’ятовуючих та перетворюючих регістрів; опанувати методами запису в регістр і видачі з нього інформації в паралельному та послідовному двійкових кодах.