Binary inputs in the 'X' state translate to analog voltages halfway between the analog voltage for the '0' state and the '1' state.

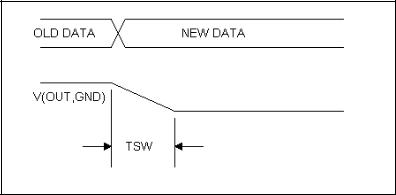

Following a change on one or more of the binary inputs, the analog output changes linearly from the old state to the new state over the specified TSW time as shown in the timing diagram below.

Figure 23-3 DAC timing diagram

See the sample circuit AD16 for an example of the use of this type of device.

Model statement form

.MODEL <timing model name> UDAC ([model parameters])

Example

.MODEL DAC1 UDAC (TSWMN=5ns TSWTY=15ns TSWMX=25ns)

Parameter |

Description |

Units |

|

|

|

TSWMN |

Switching time: min data change to stable analog out |

sec |

|

|

|

TSWTY |

Switching time: typ data change to stable analog out |

sec |

|

|

|

TSWMX |

Switching time: max data change to stable analog out |

sec |

|

|

|

Table 23-18 DAC timing model parameters

Behavioral primitives

Behavioral primitives are devices for simplifying the modeling of complex digital parts. They come in three varieties:

Logic expressions

These devices let you describe digital behavior with Boolean logic expressions.

Pin-to-pin delays

These delays let you describe rules governing the propagation delays between pins. The rules are logic expressions based upon the behavior of input pins.

Constraints

These devices let you check for timing constraints and issue warning messages when the constraints are violated. Timing constraints include pulse width, pulse frequency, setup time, hold time, and a general user-defined type.

These devices are used extensively in the Digital library to model commercial logic family parts, so it is not necessary to master their use in order to benefit from them. It is possible to use the digital logic family parts without ever learning about the behavioral primitives. However, if you want to model a part that is not in the library, you will find these primitives to be of great value and well worth the time spent learning them.

548 Chapter 23: Digital Devices

Logic expression

The logic expression primitive provides a means for describing complex digital behavior. It lets you define the behavior of outputs with standard Boolean algebra, using as variables, input states, temporary states, and output states.

SPICE format

U<name> LOGICEXP(<no. of inputs>,<no. of outputs>) +<digital power node> <digital ground node>

+<first input node>...<last input node> +<first output node>...<last output node> +<timing model name>

+<I/O model name> +[MNTYMXDLY=<delay select value>] +[IO_LEVEL=<interface subckt select value>] + LOGIC:<logic assignments>*

Schematic format

Logic expressions are usually found in the text file libraries. They are not often used directly as schematic components, although they can be. For this reason, only a few sample logic expression components are included in the Component library.

PART attribute <name>

Example

U10

TIMING MODEL attribute <timing model name>

Example

DLOGIC

I/O MODEL attribute <I/O model name>

Example

IO_STD

LOGIC attribute

LOGIC:{<logic expression>}

This attribute is a full LOGIC statement or, more commonly, the name of a LOGIC statement defined with a .define statement in the text area. Note that the 'LOGIC:' keyword must precede the {<logic expression>}.

Examples

LOFEXP1 ; must be defined by a .define in the text area LOGIC: C= {A | B & C } ; note the mandatory use of the 'LOGIC:' keyword

LOGIC: TEMP11 = {IN1 ^ IN2 & IN3 ^ IN4 }

LOGIC: TEMP12 = {IN1 ^ IN2 | IN3 ^ IN4 }

LOGIC: OUT1 = { TEMP11 & TEMP12 }

MNTYMXDLY attribute <delay select value>

Example 1

IO_LEVEL attribute <interface subckt select value>

Example 0

POWER NODE attribute <digital power node>

Example

$G_DPWR

GROUND NODE attribute <digital ground node>

Example

$G_DGND

550 Chapter 23: Digital Devices

Special Component editor fields

Pins <input pins, output pins>

The Component editor has a special 'Pins' field for these devices. You don't edit the fields directly. Instead, you click in the Shape/Pin Display and add an input or an output pin. This is how you define the names and the locations of the pins used by the logic expression device.

Note that these devices are used mainly for modeling commercial parts, and are found principally in subcircuits in the Digital library text files. Because they can have a variable number of inputs and outputs, there are an infinite number of pin combinations, and since a component in the Component library requires the specification of pin placements, placing all possible logic expression primitives in the library is clearly impossible. Accordingly, only a few such devices are found in the library, and these are mainly for illustration. These devices are really targeted for use in the subcircuits of the Digital Library section. While you can use them directly in schematics, their real power derives from their use in commercial part models, which can be readily placed and used in schematics.

Format definitions

LOGIC:

Marks the start of a group of one or more <logic assignments>. A <logic assignment> is one of the following forms:

<temporary value> = {<logic expression>} <output node name> = {<logic expression>}

<temporary value>

Any use of a name which is not in the list of the pin names for the device, automatically creates a temporary value which may be used in other <logic assignments>. The use of temporary values substantially simplifies and improves the readability of logic expressions, thus reducing errors.

<output node name>

This is one of the output node names. Assignment to an <output node name> causes the result of the <logic expression> evaluation to be scheduled after the appropriate delay from the timing model, to the output node.

<logic expression>

This is a C-like, infix-notation expression which generates one of the five valid digital logic levels { 0, 1, R, F, X }. The expression must be enclosed in curly braces {...}. The <logic expression> may use the continuation character (+) to span more than one line.

Logic expression operators and their precedence are as follows:

Operator |

Definition |

Precedence |

|

|

|

~ |

Unary negation |

1 |

|

|

|

& |

AND |

2 |

|

|

|

^ |

Exclusive OR |

3 |

|

|

|

| |

OR |

4 |

|

|

|

Table 23-19 Logic expression operators

Operands are one of the following: <input nodes>

Previously assigned <temporary values> Previously assigned <output nodes>

Constants: '0, '1, 'R, 'F, and 'X. Note that the mandatory single quote (') is a part of the constant name.

Parentheses may be freely used to group expressions.

Timing model format

The timing model is identical to the standard gate primitive UGATE format:

.MODEL <timing model name> UGATE ([model parameters])

Simulation behavior

The LOGIC statement is evaluated when any input or output pin changes state. Each <logic assignment> is evaluated in the order listed within the LOGIC statement. Expressions have no delay. Any <output node name> that changes is scheduled with the appropriate delay from the timing model. Note that usually the timing model delays are set to zero. Instead, delay is modeled by having the outputs drive the inputs of a pin-to-pin delay device. These devices provide logical control of delay based upon inputs that make implementing data sheet delays easy. Internal feedback is forbidden. This means a <logic assignment> should only use previously assigned <temporary values> or <output nodes>.

552 Chapter 23: Digital Devices

Here is an example of a logic expression used in the Digital Library to model the 7483A full adder.

*-----7483A ------

*4-Bit Binary Full Adders With Fast Carry

*The TTL Logic Data Book, 1988, TI Pages 2-257 - 2-261 U1LOG LOGICEXP(9,5) DPWR DGND

+C0 A1 A2 A3 A4 B1 B2 B3 B4

+S1_O S2_O S3_O S4_O C4_O

+ |

D0_GATE IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} |

+ |

|

+LOGIC:

+c0bar = {~C0}

+nor1 = {~(A1 | B1)}

+nand1 = {~(A1 & B1)}

+nor2 = {~(A2 | B2)}

+nand2 = {~(A2 & B2)}

+nor3 = {~(A3 | B3)}

+nand3 = {~(A3 & B3)}

+nor4 = {~(A4 | B4)}

+nand4 = {~(A4 & B4)}

+C4_O = {~(nor4 | (nor3 & nand4) | (nor2 & nand4 & nand3) |

+(nor1 & nand4 & nand3 & nand2) |

+(nand4 & nand3 & nand2 & nand1 & c0bar))}

+S4_O = {(nand4 & (~nor4)) ^ (~(nor3 | (nor2 & nand3)

+| (nor1 & nand3 & nand2) |

+(nand3 & nand2 & nand1 & c0bar)))}

+S3_O = {(nand3 & (~nor3)) ^ (~(nor2 | (nor1 &

+nand2) | (nand2 & nand1 & c0bar)))}

+S2_O = {(nand2 & (~nor2)) ^ (~(nor1 | (nand1 &

+c0bar)))}

+S1_O = {(nand1 & (~nor1)) ^ C0}

This shows just the logic expression portion of the 7483A model. Complete models for commercial digital devices like the 7483A may include logic expressions, pin-to-pin delays, constraint devices, and other logic primitives like gates and flip-flops. These are all housed in a subcircuit using the commercial part name, like 7483A.

Pin-to-pin delay

The PINDLY primitive provides a way of modeling complex conditional pin delays. Conceptually, it can be pictured as a set of channels, where the delay through each is controlled by a set of user-defined rules. Rules assign a delay to a particular channel based upon activity at the pins. A typical rule might say:

OUT1 = {CHANGED(REF1,0) & TRN_LH, DELAY(10NS,15NS,18NS)}

This means, "If the REF1 pin changed in the last 0 seconds, and the channel node OUT1 is making a low to high transition, then the delay for the OUT1 channel is min=10ns, typ=15ns, max=18ns."

PINDLY primitives are typically used within a subckt between the logic expression outputs and the subckt outputs. That is, the inputs to a PINDLY are usually the outputs of a logic expression. The outputs of a PINDLY are usually the outputs of the subcircuit which embodies the full digital model of the part.

A PINDLY may use multiple conditional rules to determine the delay on each channel. Reference and enable pin states may be used in the rule logic.

SPICE format

U<name> PINDLY(<no. of paths>,<no. of enables>,<no. of refs>) +<digital power node> <digital ground node>

+<first input node>...<last input node> +<first enable node>...<last enable node>

+<first reference node>...<last reference node> +<first output node>...<last output node> +<I/O model name> +[MNTYMXDLY=<delay select value>] +[IO_LEVEL=<interface subckt select value>] +[BOOLEAN:<boolean assignments>*] +[PINDLY:<delay assignments>*]

+[TRISTATE: ENABLE LO | HI <enable node> <delay assignments>*] +[SETUP_HOLD:<setup_hold specifications>]

+[WIDTH:<width specifications>] +[FREQ:<freq specifications>] +[GENERAL:<general specifications>]

554 Chapter 23: Digital Devices

Schematic format

PINDLYs are most commonly found in the text file libraries. They are not often used directly as schematic components, although they can be. For this reason, only a few token PINDLY components are found in the Component library.

PART attribute <name>

Example

P20

PINDELAY attribute [BOOLEAN:<boolean assignments>*] +[PINDLY:<delay assignments>*]

+[TRISTATE: ENABLE LO | HI <enable node> <delay assignments>*]

This attribute is a full PINDELAY statement or, more commonly, the name of a PINDELAY statement defined with a .define statement in the text area or in a file referenced by a .lib statement in the schematic.

Examples

CARRY_DELAYS ; defined with a .define statement in the text area

PINDLY: OUT1= { (DELAY (10NS,20NS,30NS)) }

PINDLY: BIT2= { CASE (CHANGED(REF1,O),DELAY (10NS,20NS,30NS)) }

BOOLEAN: +READY={CHANGED_LH(GATE,0)} +LOW={CHANGED_LH(SEC,0)} +PINDLY: BIT2 = { CASE (READY & LOW), + DELAY (10NS,20NS,30NS)) }

I/O MODEL attribute <I/O model name>

Example

IO_STD

MNTYMXDLY attribute <delay select value>

555

Example 1

IO_LEVEL attribute <interface subckt select value>

Example 0

POWER NODE attribute <digital power node>

Example

$G_DPWR

GROUND NODE attribute <digital ground node>

Example

$G_DGND

Special Component editor pin fields

Pins <paths, enable pins, reference pins>

The Component editor has a special Pins field for PINDLY devices. You don't edit these fields directly. Instead, you click in the Shape/Pin Display and add a path, enable pin, or a reference pin. Paths have two pins, with an arrow between them. The arrow is drawn from the path input to the path output. This defines the names and locations of the pins that the PINDLY device uses.

PINDLY devices are used mainly for modeling commercial parts, and are found principally in subcircuits in the Digital Library text files. Because they can have an infinite number of pin combinations, and since a component in the Component library requires the specification of pin placements, placing all possible PINDLY devices in the library is clearly impossible. Only a few such devices are found in the library, and these are mainly for illustration. These devices are really targeted for use in text file subcircuits. While you can use them directly in schematics, their real power derives from their use in commercial part models.

556 Chapter 23: Digital Devices