Parts from the Digital Primitives section need the I/O and Timing model information to be specified when the part is placed in the schematic. Digital Library section parts are modeled as subcircuits and have the requisite I/O and Timing model information predefined in a subckt located in a DIGXXXX.LIB text file library. The models are linked to their I/O and timing models as follows:

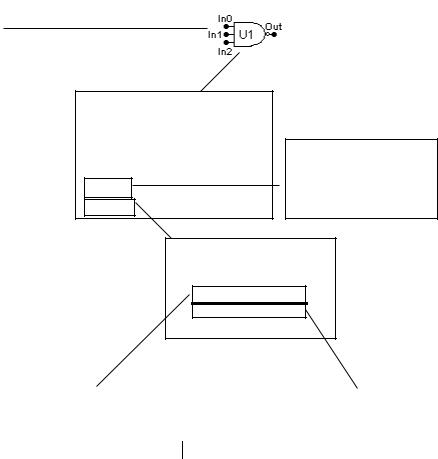

7410 schematic part

The 7410 SUBCKT and TIMING models are in the DIG000.LIB referenced by the implicit .LIB NOM.LIB statement.

The I/O model statement, the ATOD and DTOA interface circuits, and the O and N model statements are found in the DIGIO.LIB referenced by the implicit .LIB NOM.LIB statement.

SUBCIRCUIT

.SUBCKT 7410 1A 1B 1C 1Y

...

U1 NAND(3) DPWR DGND

+1A 1B 1C 1Y

+DLY_10 +IO_STD

TIMING MODEL

.MODEL DLY_10 UGATE(

+TPLHMN=11NS...

+TPHLMX=15NS)

I/O MODEL

.MODEL IO_STD UIO(...

+AtoD1="AtoD_STD" ...

+DtoA1="DtoA_STD"...

+DIGPOWER="DIGIFPWR")

ATOD INTERFACE CIRCUIT |

|

DTOA INTERFACE CIRCUIT |

.SUBCKT AtoD_STD... |

|

.SUBCKT DtoA_STD... |

... |

|

|

|

|

... |

|

|

|

O1 IN DGND |

DO74 ... |

|

N1 IN DGND DPWR |

DN74... |

|

... |

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIGITAL OUTPUT (O DEVICE) |

|

DIGITAL INPUT (N DEVICE) |

.MODEL STATEMENT |

|

.MODELSTATEMENT |

.MODEL DO74 DOUTPUT( |

|

.MODEL DN74 DINPUT( |

+S0NAME = "X" S0VLO =0.8... |

|

+S0NAME = "0" S0TSW=3.3NS |

|

|

|

Figure 23-1 Digital Model References

Primitives

Digital primitives are as follows:

Primitive Class |

Type |

Description |

|

|

|

Standard Gates |

BUF |

Buffer |

|

|

|

|

INV |

Inverter |

|

|

|

|

AND |

AND gate |

|

|

|

|

NAND |

NAND gate |

|

|

|

|

OR |

OR gate |

|

|

|

|

NOR |

NOR gate |

|

|

|

|

XOR |

Exclusive OR |

|

|

|

|

NXOR |

Exclusive NOR |

|

|

|

|

BUFA |

Buffer array |

|

|

|

|

INVA |

Inverter array |

|

|

|

|

ANDA |

AND gate array |

|

|

|

|

NANDA |

NAND gate array |

|

|

|

|

ORA |

OR gate array |

|

|

|

|

NORA |

NOR gate array |

|

|

|

|

XORA |

Exclusive OR gate array |

|

|

|

|

NXORA |

Exclusive NOR gate array |

|

|

|

|

AO |

AND-OR compound gate |

|

|

|

|

OA |

OR-AND compound gate |

|

|

|

|

AOI |

AND-NOR compound gate |

|

|

|

|

OAI |

OR-NAND compound gate |

|

|

|

Table 23-3A Digital primitives

508 Chapter 23: Digital Devices

Primitive Class |

Type |

Description |

|

|

|

Tri-state Gates |

BUF3 |

Buffer |

|

|

|

|

INV3 |

Inverter |

|

|

|

|

AND3 |

AND gate |

|

|

|

|

NAND3 |

NAND gate |

|

|

|

|

OR3 |

OR gate |

|

|

|

|

NOR3 |

NOR gate |

|

|

|

|

XOR3 |

Exclusive OR |

|

|

|

|

NXOR3 |

Exclusive NOR |

|

|

|

|

BUF3A |

Buffer array |

|

|

|

|

INV3A |

Inverter array |

|

|

|

|

AND3A |

AND gate array |

|

|

|

|

NAND3A |

NAND gate array |

|

|

|

|

OR3A |

OR gate array |

|

|

|

|

NOR3A |

NOR gate array |

|

|

|

|

XOR3A |

Exclusive OR array |

|

|

|

|

NXOR3A |

Exclusive NOR array |

|

|

|

Flip-flops / Latches |

JKFF |

JK negative-edge triggered |

|

|

|

|

DFF |

D positive-edge triggered |

|

|

|

|

SRFF |

SR gated latch |

|

|

|

|

DLTCH |

D gated latch |

|

|

|

Table 23-3B Digital primitives (continued)

Primitive Class |

Type |

Description |

|

|

|

Pullups / Pulldowns |

PULLUP |

Pullup resistor array |

|

|

|

|

PULLDN |

Pulldown resistor array |

|

|

|

Delay Lines |

DLYLINE |

Non-inertial delay line |

|

|

|

Programmable Logic |

PLAND |

AND array |

Arrays |

|

|

|

PLOR |

OR array |

|

|

|

|

PLXOR |

Exclusive OR array |

|

|

|

|

PLNXOR |

Exclusive NOR array |

|

|

|

|

PLNAND |

NAND array |

|

|

|

|

PLNOR |

NOR array |

|

|

|

|

PLANDC |

AND array plus complement |

|

|

|

|

PLORC |

OR array plus complement |

|

|

|

|

PLXORC |

XOR array plus complement |

|

|

|

|

PLNANDC |

NAND array plus complement |

|

|

|

|

PLNORC |

NOR array plus complement |

|

|

|

|

PLNXORC |

NXOR array plus complement |

|

|

|

Multi-bit Converters |

ADC |

Multi-bit ATOD converter |

|

|

|

|

DAC |

Multi-bit DTOA converter |

|

|

|

Behavioral Models |

LOGICEXP |

Logic expression |

|

|

|

|

PINDLY |

Pin-to-pin delay |

|

|

|

|

CONSTRAINT |

Constraint checker |

|

|

|

|

|

|

Table 23-3C Digital primitives (continued)

510 Chapter 23: Digital Devices

Gates

Two types of gates are provided:

Standard gates: Their outputs are always enabled. The output impedance is:

Output State |

Impedance |

0 |

DRVL (from I/O model) |

1 |

DRVH (from I/O model) |

Tri-state gates: Their outputs are enabled by an enable pin. The output impedance depends upon the enable state:

Enable state |

Output State |

Impedance |

1 |

0 |

DRVL (from I/O model) |

1 |

1 |

DRVH (from I/O model) |

0 |

Z |

DIGDRVZ |

DIGDRVZ is the impedance which corresponds to the Z state. It is specified in the Global Settings dialog box or by a .OPTIONS statement. DRVH and DRVL come from the I/O model.

Gates come in two forms, simple and arrays. Simple gates have one or more inputs, but only one output. Arrays contain one or more simple gates, with one output per simple gate. Note that arrays of gates are available for use only in SPICE text circuits or SPICE text subckt libraries. Schematic gates are always simple.

The usual Boolean rules apply to these gates. If an input state is X, the output is calculated for an input of 1 and an input of 0. If the output state differs for these two calculations, then the output is X. This avoids propagating pessimistic X states. This definition of the X state results in the following identities:

0 AND X = 0 |

0 NOR X = X |

1 AND X = X |

1 NOR X = 0 |

0 NAND X = 1 |

1 XOR X = X |

1 NAND X = X |

0 XOR X = X |

0 OR X = X |

|

1 OR X = 1 |

|

Standard gates

SPICE format

U<name> <gate type>[(<parameters>)*] +<digital power node> <digital ground node> +<input node>* <output node>*

+<timing model name> <I/O model name> +[MNTYMXDLY=<delay select value>] +[IO_LEVEL=<interface subckt select value>]

Examples:

A 5 input NOR gate:

U1 NOR(5) $G_DPWR $G_DGND IN1 IN2 IN3 IN4 IN5 OUT

D0_GATE IO_STD MNTYMXDLY=0 IO_LEVEL=2

A 3 gate NAND array with 2 inputs per gate:

U17 NANDA(2,3) $G_DPWR $G_DGND 1A 1B 2A 2B 3A 3B O1 O2 O3 DLY1 IO_ACT

An AND-OR compound gate having 2 input gates with 3 inputs per gate: UCMPD AO(3,2) $G_DPWR $G_DGND i1a i1b i1c i2a i2b i2c out dlymod io_hc_oc MNTYMXDLY=3

Schematic format

PART attribute <name>

Example

U1

TIMING MODEL attribute <timing model name>

Example 74LS

I/O MODEL attribute <I/O model name>

Example

IO_STD

512 Chapter 23: Digital Devices

MNTYMXDLY attribute <delay select value>

Example 2

IO_LEVEL attribute <interface subckt select value>

Example 1

POWER NODE attribute <digital power node>

Example

$G_DPWR

GROUND NODE attribute <digital ground node>

Example

$G_DGND

Model statement form

.MODEL <timing model name> UGATE ([model parameters])

Example

.MODEL TOR UGATE ( TPLHMN=3ns TPLHTY=5ns TPLHMX=7ns

+ TPHLMN=4ns TPHLTY=6ns TPHLMX=7ns )

The standard gate types and their parameters are shown in Table 23-4. The table uses the standard syntax:

in |

one input node |

in* |

one or more input nodes |

out |

one output node |

out* |

one or more output nodes |

The phrase <# of inputs> means the number of inputs per gate. The phrase <# of gates> means the number of gates in the array.

513

Type |

Parameters |

Nodes |

Description |

|

|

|

|

BUF |

|

in, out |

Buffer |

|

|

|

|

INV |

|

in, out |

Inverter |

|

|

|

|

AND |

<no. of inputs> |

in*, out |

AND gate |

|

|

|

|

NAND |

<no. of inputs> |

in*, out |

NAND gate |

|

|

|

|

OR |

<no. of inputs> |

in*, out |

OR gate |

|

|

|

|

NOR |

<no. of inputs> |

in*, out |

NOR gate |

|

|

|

|

XOR |

|

in1, in2, out |

Exclusive OR gate |

|

|

|

|

NXOR |

|

in1, in2, out |

Exclusive NOR gate |

|

|

|

|

BUFA |

<no. of gates> |

in*, out* |

Buffer array |

|

|

|

|

INVA |

<no. of gates> |

in*, out* |

Inverter array |

|

|

|

|

ANDA |

<no. of inputs>, <no. of gates> |

in*, out* |

AND array |

|

|

|

|

NANDA |

<no. of inputs>, <no. of gates> |

in*, out* |

NAND array |

|

|

|

|

ORA |

<no. of inputs>, <no. of gates> |

in*, out* |

OR array |

|

|

|

|

NORA |

<no. of inputs>, <no. of gates> |

in*, out* |

NOR array |

|

|

|

|

XORA |

<no. of gates> |

in*, out* |

Exclusive OR array |

|

|

|

|

NXORA |

<no. of gates> |

in*, out* |

Exclusive NOR array |

|

|

|

|

AO |

<no. of inputs>, <no. of gates> |

in*, out |

AND-OR compound gate |

|

|

|

|

OA |

<no. of inputs>, <no. of gates> |

in*, out |

OR-AND compound gate |

|

|

|

|

AOI |

<no. of inputs>, <no. of gates> |

in*, out |

AND-NOR compound gate |

|

|

|

|

OAI |

<no. of inputs>, <no. of gates> |

in*, out |

OR-NAND compound gate |

|

|

|

|

Table 23-4 Standard gate types

514 Chapter 23: Digital Devices

Input nodes are listed before output nodes. In a gate array, the node order is: the input nodes for the first gate, the input nodes for the second gate,..., the input nodes for the final gate, the output node for the first gate, the output node for the second gate,..., the output node for the final gate. The number of output nodes is equal to the number of gates.

A compound gate contains two levels of logic. The phrase <no. of inputs> is the number of inputs per first-level gate, and <no. of gates> is the number of firstlevel gates. All of the first-level gate outputs are connected to one second-level gate, so the device only has one output. The node order is: the input nodes for the first first-level gate,..., the input nodes for the final first-level gate, and the output node. For an OA gate, the first-level gates are <no. of inputs> input OR gates, and they all feed into one AND gate, which produces the output.

Parameter |

Description |

Units |

|

|

|

TPLHMN |

Delay: min low to high |

sec |

|

|

|

TPLHTY |

Delay: typ low to high |

sec |

|

|

|

TPLHMX |

Delay: max low to high |

sec |

|

|

|

TPHLMN |

Delay: min high to low |

sec |

|

|

|

TPHLTY |

Delay: typ high to low |

sec |

|

|

|

TPHLMX |

Delay: max high to low |

sec |

|

|

|

Table 23-5 Standard gate timing model parameters

Special Component editor fields

Inputs <number of inputs>

The Component editor has a special 'Inputs' field for standard gates. It lets you specify the number of gate inputs. When you enter a value, the system places an output pin and the specified <number of inputs> pins on the display and you must drag them into place on the shape.

Tri-state gates

SPICE format

U<name> <tri-state gate type>[(<parameters>*)] +<digital power node> <digital ground node> +<input node>* <enable node> <output node>* +<timing model name> <I/O model name> +[MNTYMXDLY=<delay select value>] +[IO_LEVEL=<interface subckt select value>]

Examples:

A 3 input tri-state NOR gate:

U20 NOR3(3) $G_DPWR $G_DGND IN1 IN2 IN3 ENABLE OUT D0_GATE IO_STD MNTYMXDLY=0 IO_LEVEL=2

A 3 gate tri-state AND array with 2 inputs per gate:

UBX AND3A(2,3) $G_DPWR $G_DGND 1A 1B 2A 2B 3A 3B EN O1 O2 O3 DLY1 IO_ACT

Schematic format

PART attribute <name>

Example

U1

TIMING MODEL attribute <timing model name>

Example 74ALS

I/O MODEL attribute <I/O model name>

Example

IO_STD

516 Chapter 23: Digital Devices