Скобцовы Моделирование и тестирование

.pdf

представляют соответственно простые кубы и значения параметров для любых стандартных 3-входовых вентилей. В табл.2.9 в каждой строке представлен простой куб вентиля в порядке, указанном в табл.2.8.

На рис.2.9 представлен псевдокод типичной программы вычисления значения выхода, реализующей данный метод [44].

Вычисление(G,c,i)

{

u_values=FALSE;

for каждого входа v вентиля G

{

if v=c then return c i ;

if v=u then u_values=TRUE;

}

if u_values then return u; return c i ;

}

Рис.2.9 Сканирование входов

2.5.4 Метод счетчиков

Анализ программы рис.2.9 показывает, что для вычисления значения выхода стандартного вентиля в троичном алфавите достаточно знать:

имеет ли какой либо вход контролирующее значение c и при его отсутствии наличие неопределенного значения u на входах. Поэтому был предложен метод [44], в котором вместо хранения значений входов для каждого вентиля сохраняются значения двух счетчиков – c_count и u_count, где содержится число входов с контролирующим и неопределенным значением соответственно. При очередном вызове функции модели вентиля значение этих счетчиков может изменяться.

Например, при изменении 1 → 0 входа вентиля И счетчик 0_count

51

увеличивается на 1, в то время как при изменении 0→u увеличивается на 1

счетчик u_count. Тогда вычисление значения выхода вентиля сводится к проверке счетчиков. На рис.2.10 представлен метод вычисления значения

выхода.

Вычисление(G,c,i)

{

If c_count > 0 then return c i ; If u_count > 0 then return u; return c i ;

}

Рис.2.10 Счетчик значений входов

Более подробно вопросы построения многозначных моделей логических элементов будут изложены в разделе 3, где рассматривается единая система многозначных алфавитов и функций.

2.6 Модели задержек логических элементов

При логическом моделировании важнейшим фактором,

определяющим достоверность модели по отношению к реальной схеме,

является учет задержек распространения сигналов через элементы. В этом разделе мы рассмотрим способы представления задержек, их особенности и ограничения.

Простейшей формой модельной задержки является модель транспортной задержки, при которой логический элемент рассматривается состоящим из двух каскадов, как это показано на рис.2.11. При этом в первом каскаде реализуется его логическая функция (предполагается мгновенное распространение сигнала от входа до выхода), а второй каскад моделирует задержку распространения сигнала от входов элемента до его выхода.

52

&

∆T

∆T

&

Нулевая

задержка

Рис. 2.11 Модель транспортной задержки.

На практике применяются различные модели транспортной задержки. При моделировании без учета задержек элементов, в частности,

когда время задержки принимается равным нулю, используют модель с нулевыми задержками. Модель с нулевыми задержками применяется только для моделирования комбинационных и синхронных последовательностных схем.

Модель, в которой времена задержек всех логических элементов считаются одинаковыми, носит название модели с единой (или единичной)

задержкой. Благодаря тому, что элементам присвоены задержки,

появляется возможность обрабатывать асинхронные схемы с обратными связями и проводить хотя бы приближенный анализ временных соотношений в схеме. В общем случае, однако, следует учитывать то, что различные типы логических элементов обладают разными задержками.

Поэтому более адекватной является модель с номинальными задержками,

при которой каждому логическому элементу присваивается свое целочисленное значение задержки, измеряемое в единицах модельного времени. Для того чтобы осуществить соответствующее этому случаю моделирование, в качестве базовой единицы модельного времени обычно

53

используют наибольший общий делитель времен задержек ∆T элементов и

присваивают значения задержек в соответствии с их кратностью.

|

a |

|

|

|

|

1 |

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

d |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

& |

|

c |

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

k |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

e |

|

|

|

D |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

g |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

0 |

|

C |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.12 Пример схемы

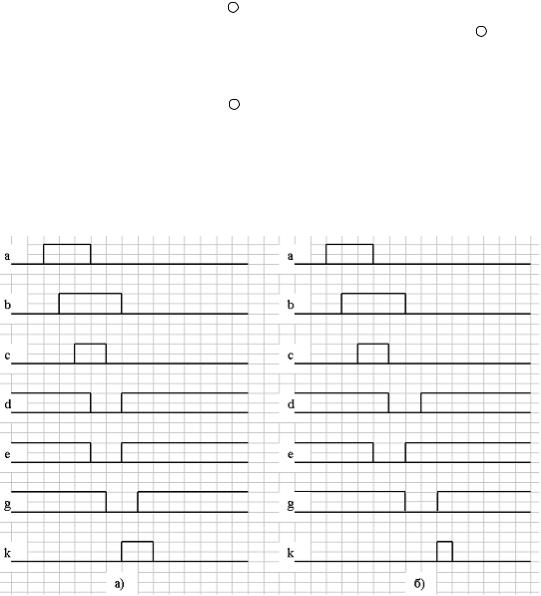

Рис. 2.13 Примеры моделирования: а) единичные задержки;

б)номинальные задержки (∆T=2 для элементов В, D и Е и ∆T=1 для

элементов А, С и D).

Пример. Пусть для схемы, показанной на рис. 2.12, выполняется моделирование с использованием модели с единичной задержкой. На

54

рис.2.13 а) представлены результаты логического моделирования с использованием модели единичных задержек в виде временных диаграмм сигналов на линиях схемы. На рис.2.13 б) показаны временные диаграммы для той же схемы, но с использованием модели номинальных задержек,

где время задержки элементов В, D и Е составляет 2 единицы, а для остальных элементов – 1 (здесь одно деление соответствует единице модельного времени).

В ряде случаев используют для одного и того же элемента различные значения задержек для переднего и заднего фронтов сигнала.

Например, в схемах на МОП-структурах время задержки спада сигнала ∆F

может в 3 раза превышать время задержки переднего фронта ∆R.

Следовательно, в данном случае при моделировании длительность

(положительного) импульса может увеличиваться (как это имеет место на

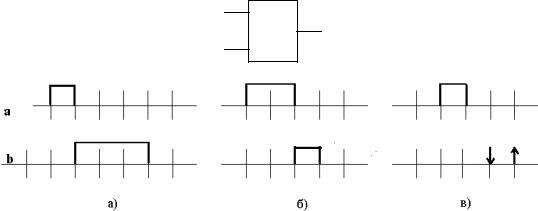

рис.2.14 а).

a

& b

1

Рис. 2.14. Различные задержки нарастания фронта и спада:

а) ∆R=1, ∆F=3; б) ∆R=2, ∆F= 1; в) ∆R=3, ∆F=1.

Соответственно большее значение задержки нарастания фронта по сравнению с задним фронтом может привести к уменьшению длительности импульса (рис.2.14 б). Вместе с тем, при некоторых

55

соотношениях времен задержек переднего фронта и спада возможны случаи, когда моделирование показывает невозможные с практической точки зрения события (рис. 2.14 в), когда задний фронт “обгоняет” передний. Для исключения подобных ситуаций в процессе моделирования следует предусматривать специальные меры.

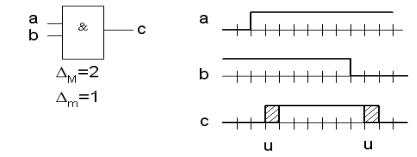

Определить точное значение задержки для данного типа логического элемента довольно трудно так как всегда существует разброс значений (в

силу технологических причин, влияния внешней среды и т.п. ). Поэтому иногда для повышения точности моделирования указывают некоторый диапазон ожидаемых задержек. Такую модель называют моделью с неопределенной задержкой. Модель, в которой в качестве концов диапазона указывают максимальное время задержки ∆M и минимальное время задержки ∆m, носит название модели с максимальной и минимальной задержками.

В качестве примера рассмотрим распространение сигнала через элемент И. Как показано на рис. 2.15, выходное значение изменяется от 0 к 1 при изменении входного сигнала от 0 к 1. Однако, поскольку в течение времени ∆m изменения не происходит, а после ∆M устанавливается 1, то в диапазоне от ∆m до ∆M присваивается неопределенное значение u.

Аналогично при моделировании заднего фронта также присваивается неопределенное значение u, как показано на рис.2.15.

Рис. 2.15 Образование неопределенного значения сигнала

56

С помощью максимальных и минимальных задержек можно промоделировать большое число сложных временных ситуаций,

встречающихся в реальной схеме. Вместе с тем такая модель часто показывает чересчур "пессимистические" результаты, когда большая часть линий схемы принимает неопределенные значения. Аналогичным образом при моделировании с неопределенной задержкой в соответствии с наихудшим случаем каждый раз при прохождении сигнала через элемент диапазон неопределенных значений u расширяется.

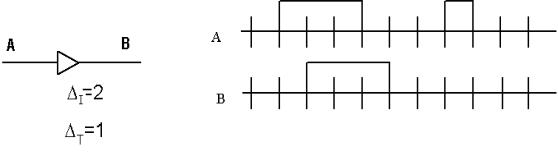

В заключение рассмотрим модель инерционной задержки ∆I. В

понятие инерционной задержки элемента вкладывают следующий смысл.

Если на вход элемента подается входной импульс продолжительностью меньше инерционной задержки ∆I, то элемент не пропускает его (выходной сигнал не изменяется). Введение такой задержки позволяет моделировать ситуации в реальных схемах, когда элементы не успевают срабатывать на коротких импульсах вследствие своей инерционности (например,

вследствие наличия емкости). Если, например, ∆I =2, то, как показано на рис. 2.16, при ширине импульса 1 (и менее) нельзя получить изменение сигнала на выходе элемента.

Рис. 2.16. Инерционная задержка.

Выше были рассмотрены различные виды задержек и связанные с ними проблемы. Для более точного моделирования можно рассматривать сочетания различных видов задержек. Однако это значительно

57

увеличивает время моделирования и неприемлемо с точки зрения практического использования. Реальный путь состоит в том, что следует учитывать влияние задержек с помощью моделей, не вызывающих трудностей при моделировании. Например, можно применять последовательно следующие средства:

1)логическая верификация с использованием только модели с единичными задержками;

2)моделирование с учетом различных задержек для подъема и спада сигналов;

3)моделирование с использованием модели с неопределенной задержкой;

4)моделирование с использованием статистических методов вычисления задержки.

2.7 Внутренние (машинные) модели схем

После ввода внешнего описания ДУ в компьютер, оно транслируется во внутреннее представление устройства, которое непосредственно используется в процессе логического моделирования. Существуют две

основные формы (модели) внутреннего представления ДУ –

компилятивная и интерпретативная. При компилятивной модели внешнее описание ДУ в виде структурной модели (схемы) или функциональной с использованием ЯРП транслируется в программу на некотором языке программирования (обычно ассемблере или С), которая непосредственно выполняет процесс моделирования. При интерпретативной модели внешнее описание транслируется в систему связанных таблиц, которые далее используются универсальной программой моделирования.

2.7.1 Компилятивная модель

В компилятивном методе моделирования описание схемы транслируется в последовательность операторов языка программирования

58

или машинных инструкций. Например, синхронная последовательностная схема, представленная на рис.2.17 может быть транслирована в следующую программу, представленную на рис.2.18.

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.17 Схема для компилятивной модели

LDA B

AND Q

INV

STA E

OR A

STA F

STA Q

Рис.2.18 Компилятивная модель

Алгоритм компилятивного моделирования [39] приведен в виде псевдокода на рис.2.19. Следует обратить внимание на то, что при этом необходимо предварительно ранжировать схему по уровням. Основным преимуществом компилятивного метода моделирования является его высокое быстродействие. К недостаткам следует отнести то, что модель при изменении схемы (в процессе проектирования) каждый раз должна компилироваться заново. Здесь, как правило, используется сквозное (а не событийное) моделирование, при котором на каждой итерации значение каждого логического элемента пересчитывается заново. Кроме этого,

59

необходимо предварительно выполнить обрыв обратных связей для последовательностных схем (для этого разработаны соответствующие алгоритмы). Но основной проблемой этого метода является учет временных задержек логических элементов. Поэтому данный метод, в

основном, применяется при моделировании комбинационных и синхронных последовательностных схем. При этом, как правило,

проверяется только логика, а не временные соотношения.

Компилятивное моделирование (схема, входные воздействия)

{

Чтение внешнего описания схемы;

Разрыв обратных связей (если это необходимо для схем с памятью);

Упорядочивание элементов по уровням;

Генерация компилятивного кода;

Чтение начального значения для каждого линии схемы; FOR каждого нового входного набора

{

FOR каждого уровня схемы

{

FOR каждого логического элемента в уровне

{

Выполнение компилятивного кода логического элемента;

}

}

IF вновь вычисленные значения выходов и псевдовыходов обратных связей совпадают с предыдущими

THEN вывод результатов моделирования;

ELSE присваивание псевдовходам вновь вычисленных значений псевдовыходов обратных связей;

}

}

Рис.2.19 Компилятивное моделирование

60