Скобцовы Моделирование и тестирование

.pdf

Для побитовой операции И все тэги для их распространения должны

быть одного знака. Пусть задан положительный тэг переменной a, а

переменная b не отмечена тэгом. Если по крайней мере один из битов в

векторе b отличен от нуля и v(a) ≠ 2n − 1, то v( f ) = v(a) & v(b) |

и выходу |

|

присваивается v( f ) + ∆ . |

Для положительных тэгов для обеих переменных |

|

a и b в случае, |

когда v(a) ≠ 2n − 1 и v(b) ≠ 2n − 1 |

полагаем |

v( f ) = v(a) & v(b) и выходу присваивается также v( f ) + ∆ . Аналогичные действия выполняются для отрицательных тэгов.

Для поразрядного НЕ v( fi ) = v(ai ) , где0 ≤ i < n . Для положительного тэга на a выходу присваивается значение v( f ) − ∆ .

Распространение тэгов через условные операторы if требует препроцессорной обработки программы. Достижимость процесса из условного оператора определяется путем анализа блок-схемы. Если каждый процесс имеет один вход и один выход, то все операторы в пределах данного процесса имеют одинаковые свойства достижимости.

Без потери общности предполагается, что каждый условный оператор является бинарным. Для каждого условного оператора определяется множество достижимых процессов при условии истинности управляющей переменной с. Это множество обозначается Pc. Аналогично через Pс ,

обозначается множество процессов, достижимых при нулевом значении управляющей переменной c. При обработке условных операторов в процессе моделирования возможны два случая:

1)Нет тэга в управляющей переменной. В этом случае моделирование протекает обычным образом. В соответствующих процессах выполняются операторы, для которых в случае необходимости вносятся и распространяются тэги.

2)Если тэг присоединен к управляющей переменной c, то это ведет к неправильному ветвлению при достижении данного условного оператора.

151

Пусть c имеет положительный тэг. Если значение c равно 1, то тэг не распространяется. И наоборот, если c=0, то тэг вносится во все

переменные в процессах Pс − Pc . При наличии тэга в условии операции

присваивания пропускаются, следовательно, к переменным выхода присоединяется тэг. Если новое значение выхода после присваивания меньше старого, то присваивается положительный тэг. Если новое значение больше старого, то присваивается отрицательный тэг. Если же значения одинаковы, либо старое значение не определено, то тэг не вносится.

4.10.8 Функциональные модели неисправностей автоматного уровня

Конечные автоматы (КА) являются классической функциональной

моделью последовательностных схем (систем с памятью). В качестве

меры покрытия при этом чаще всего используются две меры, основанные на представлении КА графом переходов-выходов: 1) покрытие состояний,

которая показывает число «посещенных» состояний (в идеале все состояния автомата должны быть посещены в процессе диагностического

эксперимента); 2) покрытие переходов, которое показывает число

пройденных переходов на данной тестовой последовательности (для полного теста должны быть все переходы). Некоторые исследователи рассматривают только особо важные с точки зрения пользователя переходы, которые подлежат проверке при тестировании [64,65]. Кроме этого, используется мера покрытия путей в графе переходов-выходов автомата или системном графе процессора [66]. В работе [67] для тестирования последовательностных схем используется классический математический аппарат булевых функций. Указанные меры покрытия являются приближенными, наиболее полно вопросы тестирования последовательностных схем решаются в теории экспериментов с

152

автоматами [68]. Но, к сожалению, при этом длина тестовых последовательностей слишком велика, поскольку при этом проверяется вся таблица переходов-выходов автомата. Поэтому некоторые исследователи для тестирования выделяют определенное подмножество автоматов,

критичных с точки зрения тестирования. Расширенный конечный автомат и управляющий автомат образуют редуцированный автомат посредством разбиения битов переменных состояния на информационные и управляющие.

4.10.9 Функциональные неисправности микропроцессоров

В классической работе [69] микропроцессор представляется в виде системного графа (СГ), основанного на его архитектуре и наборе команд.

Вершины этого графа соответствуют регистру или группе регистров МП.

Пусть R={R1, R2,…,Rn } - множество всех программно доступных

регистров МП и I={I1,...,Ip} – его множество команд. Тогда вершины графа представляют регистр (или группу эквивалентных регистров) и

специальные вершины IN и OUT. Вершина IN соответствует источнику входных данных МП (ОЗУ и т.д.), а вершина OUT - приемнику выходных данных. Они включают в себя адреса, данные и управляющие сигналы,

которые принимает (IN) и посылает (OUT) МП. Если существует хотя бы одна команда во время выполнения которой информация передается из

регистра |

Ri в регистр |

Rj |

, то в СГ строится ребро, направленное от |

вершины |

Ri к вершине |

Rj |

. Если существует хотя бы одна команда, при |

которой информация передается с входов МП в регистр Ri, то в СГ

проводится ребро из вершины IN к вершине Ri. Аналогично, если существует хотя бы одна команда, при которой информация передается из

Ri на выходы МП, то в СГ строится ребро из вершины Ri к вершине

OUT. При таком подходе предполагается, что каждая команда Ii состоит из микрокоманд Ii ={m1, m2,..., mki}, которые выполняются последовательно.

153

Каждая микрокоманда в свою очередь состоит из множества

микроинструкций |

mi = {M i1, M i2 |

,..., M iq }, |

которые |

выполняются |

|

|

i |

|

|

параллельно.

В соответствии с основными функциональными блоками МП рассматриваются следующие модели функциональных неисправностей. 1. Модель неисправности функции дешифрации адресов регистров. Пусть fd (Ri) обозначает функцию дешифрации адреса регистра. Тогда при этой неисправности возможно:

(вместо адреса Ri выбирается адрес Rj ); (адрес не выбирается);

в) fd (Ri)= {Ri ,Rj} (вместо адреса Ri выбирается два адреса Ri и Rj). 2.Модель неисправности функций хранения данных. Предполагается, что любой разряд регистра может иметь константные неисправности 0,1.

3. Модель неисправности функций передачи данных. При этом любое число линий может иметь константные неисправности 0,1 и любая пара линий может замкнуться (сигналы на этих линиях принимают одинаковые значения).

4.Модель неисправности дешифрации инструкций и функций управления последовательностью операций. При этом предполагается, что может произойти одно или несколько следующих событий:

а) одна или несколько микроинструкций в команде не выполняется;

б) дополнительно выполняются микроинструкции, которые не должны быть в данной команде;

в) дополнительно выполняются микрокоманды, которых нет в последовательности данной команды.

При этом предполагается, что число операций записи информации в регистры МП не увеличивается. Кроме этого считаем, что число микрокоманд в команде (даже неисправной) не превышает некоторого

154

числа К, а число микроинструкций в микрокоманде не превышает также числа М.

5. Модели неисправностей функций обработки данных. Специальная модель для этого типа неисправностей не вводится. Считается, что либо известен полный тест АЛУ, либо его можно построить, зная структуру АЛУ на вентильном уровне.

4.10.10 Неисправности интерфейса

При использовании современной технологии проектирования сложных многопроцессорных систем, основанной на «интеллектуальных ядрах» (IP cores) акцент тестирования смещается в сторону проверки интерфейса между этими компонентами [70]. При этом неявно подразумевается, что сами ядра исправны (их тестирование проведено в процессе разработки). Следует отметить, что дополнительные сложности при этом возникают из-за кратной синхронизации таких сложных систем.

Интерфейс между компонентами с разными синхронизирующими

воздействиями является существенно асинхронным, что создает дополнительные трудности.

Таким образом, меры покрытия неисправностей, используемые при тестировании программного обеспечения, могут быть распространены на функциональное тестирование ЦС, представленных с помощью языков описания аппаратуры. Данный подход позволяет тестировать современные сложные многопроцессорные ЦС, проверка которых невозможна на вентильном уровне из-за сложности и их функциональных особенностей.

155

5. МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ С НЕИСПРАВНОСТЯМИ

Моделирование ЦУ с неисправностями является одним из важнейших разделов логического моделирования и используется в системах автоматизированного проектирования и диагностики ДУ при решении следующих задач:

–определение эффективности тестовой последовательности – её полноты и диагностических свойств;

–построение диагностических словарей для поиска неисправностей в логических схемах;

–генерация проверяющих тестов (в качестве инструмента определения эффективности генерируемых наборов);

–анализ поведения схемы и ее свойств с неисправностью.

–Отметим, что наличие неисправности может существенно изменить поведение схемы и привести к следующим последствиям:

–неисправность может вызвать состязания сигналов (отсутствующие в исправной схеме);

–неисправность может вызвать осцилляцию (бесконечное изменение сигналов);

–неисправность может помешать установке схемы с памятью в начальное состояние;

–неисправность может преобразовать комбинационную схему в последовательностную или синхронную – в асинхронную и т.д.

Для решения этих задач программам моделирования неисправных схем требуется следующая информация:

–описание логической схемы;

–описание тестовой входной последовательности;

–модели и список обрабатываемых неисправностей.

156

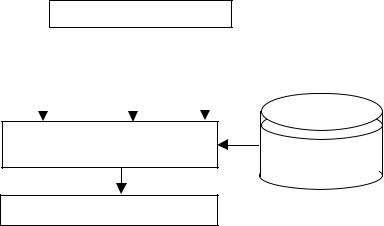

Из рассмотренных в предыдущем разделе моделей неисправностей здесь

чаще всего используются одиночные константные неисправности. Процесс

моделирования неисправных цифровых схем представлен на рис. 5.1.

Входные воздействия

|

|

|

|

|

|

Список |

|

|

Модель |

||

неисправностей |

|

|

схемы |

||

|

|

|

|

|

|

|

|

|

|

|

|

Моделирование

неисправностей

Библиотека

Результаты моделирования

Рис. 5.1 Моделирование неисправностей

Здесь неисправности из сокращенного списка вводятся в модель схемы, далее моделируется поведение схемы на входном наборе с последующим анализом. Если неисправность проверяется (дает выходную реакцию, отличную от реакции исправной схемы), то она удаляется из списка и рассматривается следующая. В противном случае подается следующий входной набор. Процесс продолжается до тех пор, пока список неисправностей не будет пуст. Отметим, что анализ неисправных схем может существенно превышать время моделирования исправных схем.

Поэтому при моделировании неисправных схем решающим фактором является быстродействие (в то время как для исправных схем важна прежде всего адекватность).

По сравнению с моделированием исправных ДУ при моделировании неисправностей нужно дополнительно выполнить следующие действия:

1.Определение множества моделируемых неисправностей;

2.Внесение влияния неисправностей;

157

3.Распространение влияния неисправностей;

4.Определение проверяемости неисправностей.

Различают условно проверяемые неисправности и проверяемые

неисправности. Неисправность считается условно проверяемой, если в результате моделирования на внешнем выходе в неисправной схеме устанавливается неопределенное значение u, а в исправной - определенное значение 0 или 1. Неисправность считается проверяемой, если в результате моделирования хотя бы на одном внешнем выходе исправной и неисправной схем устанавливаются различные определенные значения.

Методы моделирования ДУ с неисправностями, в основном, отличаются различной техникой распространения влияния неисправностей.

5.1.Последовательное моделирование

Впростейшем случае моделирование неисправностей может быть выполнено любым методом моделирования исправных ДУ путем внесения неисправности в схему в процессе моделирования. При этом, как правило,

выполняется моделирование исправной схемы в двоичном алфавите,

результаты которого сохраняются для последующего сравнения с выходными реакциями неисправных схем. Далее последовательно выполняется логическое моделирование на тестовой последовательности для каждой неисправной схемы в отдельности. Это производится путем внесения влияния отдельной неисправности в описание схемы и моделирования в двоичном алфавите. В процессе моделирования выходные реакции неисправной схемы после каждого входного набора сравниваются с хранимыми результатами исправной схемы. В случае их расхождения данная неисправность считается проверяемой и моделирование прекращается (для оставшихся входных наборов не выполняется). Этот процесс повторяется последовательно для каждой неисправности из обрабатываемого списка.

158

Для исправного устройства моделирование на одном наборе выполняется один раз. В случае неисправного ДУ при наличии N f

неисправностей в наихудшем случае схема моделируется N f раз, так как необходимо промоделировать N неисправных и одно исправное ДУ.

Соответственно, время моделирования может возрасти в N f +1 раз. Это

является основным недостатком данного простого метода. К

преимуществам метода можно отнести то, что здесь легко моделировать не только константные неисправности, но и неисправности любого другого типа, которые были рассмотрены в предыдущем разделе. При этом проще учесть такие эффекты присутствия неисправности как состязания,

осцилляции и т.п., что вызывает определенные проблемы в других методах. Кроме этого, при таком подходе можно локально моделировать неисправности и на электрическом (аналоговом) уровне. Очевидно, что затраты оперативной памяти при этом методе практически не превышают затрат моделирования исправной схемы. Отметим, что для повышения скорости моделирования при этом методе можно (и удобно) использовать аппаратные ускорители и многопроцессорные системы. В последнее время этот метод все чаще применяется на функциональном уровне, например,

для моделирования устройств, описанных на VHDL. Это обуславливается тем, что разработка программ моделирования неисправностей на этом уровне является слишком сложной и чаще проще использовать готовые средства и выполнить моделирование для каждой функциональной неисправности отдельно. Отметим, что некоторые программные средства имеют встроенные средства для внесения функциональных неисправностей.

Однако для повышения эффективности моделирования неисправных схем разработаны специальные методы, которые мы рассмотрим в последующих разделах.

159

5.2Параллельное моделирование

Впараллельном методе моделирования [71,1] влияние неисправностей распространяется параллельно для группы схем. При этом

вгруппу входят одна исправная и множество неисправных схем. Метод основан на использовании параллелизма при выполнении поразрядных логических операций в процессе моделировании логических элементов.

Если компьютер имеет P-разрядное машинное слово, то обычно одновременно моделируется поведение P схем (одна исправная и P-1

неисправных). Поэтому все неисправности ДУ разбиваются на группы,

содержащие по P-1 неисправностей и моделирование схемы выполняется

]N/P-1[ раз, где N – количество всех неисправностей. Если схема имеет M

внешних выходов, то число проходов моделирования ограничено снизу следующим выражением ]N/(P-1)M[. Здесь ] [ означает наименьшее сверху целое число.

5.2.1 Параллельное моделирование в двоичном алфавите

Рассмотрим сначала случай моделирования в двоичном алфавите.

При этом каждой линии схемы соответствует одно машинное слово.

Внесение влияния неисправностей обычно осуществляется с помощью специальных масок неисправностей. Так, например, неисправность константа 1 вносится путем выполнения операции ИЛИ с маской неисправности, содержащей 1 в разряде, соответствующем этой неисправности. Аналогично неисправность константа 0 вносится с помощью операции И с маской, содержащей 0 в разряде, соответствующем данной неисправности. Рассмотрим 2-входовой вентиль И с константными неисправностями, представленный на рис.5.2. Допустим, что он является фрагментом некоторой логической схемы. Пусть А, B и C – 4-разрядные

(для простоты) машинные слова, хранящие значения сигналов для входов и выхода этого вентиля. Пусть левый разряд представляет исправную

160