Скобцовы Моделирование и тестирование

.pdf

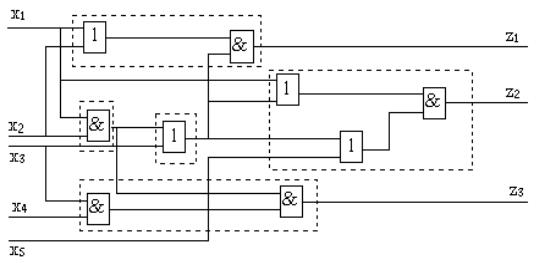

Рис.5.17 Выделение одновыходных подсхем

На схеме рис.5.17 максимальные одновыходные подсхемы отмечены пунктиром. В связи с этим процедура моделирования неисправности на одном входном наборе имеет две фазы - прямую и обратную. В прямой фазе осуществляется выбор неисправности, связанной с выходом элемента,

являющегося корневым для некоторой максимальной одновыходной подсхемы и выполняется распространение влияния неисправности. Если неисправность на выходе корневого элемента проверяется, то могут проверяться и неисправности, расположенные на линиях подсхемы. В этом случае выполняется обратная фаза, выявляющая проверяемые неисправности внутри подсхемы. При этом, очевидно, могут быть обнаружены только константные неисправности, инверсные значениям,

установившимся при моделировании на линиях исправной подсхемы.

Очевидно, что в случае непроверяемости неисправности на выходе корневого элемента неисправности поддерева заведомо не обнаруживаются. Этот метод получил дальнейшее развитие, в котором предложен метод, моделирующий одну неисправность параллельно на

множестве наборов теста (parallel pattern single fault propagation-PPSFP)

[44]. Технически это выполняется путем работы со всеми битами

191

машинного слова. Значения линий схемы, соответствующие тестовым наборам хранятся в соответствующем бите слова. Моделирование логических элементов осуществляется при помощи побитовых логических операций. Весь тест разбивается на группы по P тестовых наборов, где P -

длина машинного слова. Моделирование проводится сразу на P наборах.

То есть скорость увеличивается приблизительно в P раз.

Очевидно, что в основе высокого быстродействия рассматриваемого метода лежит организация параллельных вычислений в процессе прямой и обратной фазы. Эффективность организации параллельных вычислений зависит от используемого алфавита и системы многозначных функций в нем. В различных работах применяются различные алфавиты: в

большинстве случаев используются простейший двоичный алфавит

B2={0,1} или троичный алфавит E3={0,1,u}. Однако применение данных алфавитов делает необходимым раздельное моделирование исправного и неисправного ДУ. При этом необходимо хранить значения сигналов на линиях исправной и неисправной схем в различных ячейках. Это приводит к излишним затратам времени и памяти. Поэтому мы используем универсальный 16-значный алфавит B16 (Табл.3.1), представленный в подразделе 3.1. При этом элементы базового алфавита B4 имеют следующую интерпретацию: 0(1)=00(11) - значения сигналов в исправной и неисправной схемах совпадают и равны 0(1); D'(D)=01(10) - значения сигналов в исправной и неисправной схемах различны и равны 0(1) - в

исправном ДУ, 1(0) - в неисправном ДУ. Поэтому если значения сигналов в исправном и неисправном устройствах совпадают, то на линии устанавливается 0 или 1, если различны - то D’ или D. Использование алфавита B16 позволяет моделировать исправную и неисправную схемы одновременно, что, в то же время устраняет необходимость хранить дополнительно массив значений исправного ДУ. Таким образом,

применение 16-значного алфавита приводит к сокращению ресурсов

192

времени и памяти. Параллельные вычисления выполняются при помощи единой системы многозначных функций, описанной в подразделе 3.2. При вычислениях в прямой фазе применяются прямые многозначные функции

(Табл.3.5). Аналогично, для решения задачи обратной фазы используются обратные многозначные функции (Табл.3.7). При этом в соответствии со способом кодирования алфавита B16 (Табл.3.1) и описания поведения многозначной функции с помощью четырех характеристических булевых функций значения сигналов на некоторой линии g ДУ хранятся в четырех машинных словах. В них i-е биты содержат код (gi0 ,giD′ ,giD ,g1i ) значения gi,

полученного в результате моделирования на i-м наборе из текущей группы.

Покажем на примере вентиля f=x1 x2, как выполняется распространение влияния константной неисправности x1≡1 параллельно для 8 наборов. Предположим, что в исправном устройстве на данных 8

наборах мы имеем следующие значения входов: x1=000111uu, x2=01u01u01.

Всоответствии с методом кодирования алфавита B16 (Табл.3.1)

характеристические компоненты, определяющие значения x1 и x2 на 8

наборах, имеют следующие значения:

x10 =(11100011), x1D′ =(00000011), x1D =(00000011), x11 =(00011111), x20 =(10110110), x2D′ =(00100100), x2D =(00100100), x12 =(01101101).

До выполнения процедуры распространения необходимо внести влияние неисправности на соответствующую линию схемы. Поэтому в нашем случае вносим влияние неисправности для входа вентиля x1: x1=(D' D' D' 1 1 1 F1 F1) или покомпонентно:

x10 =(00000000), x1D′ =(11100011), x1D =(00000000), x11 =(00011111).

193

Далее выполняем распространение влияния неисправности x1≡1

параллельно, используя характеристические функции f 0 , f D' , f D , f 1 для

вентиля И (Табл.3.5). В результате получаем:

f 0 =(10110110), f D' =(01100101), f D =(00000100), f 1 =(00001101),

что соответствует f=(0 D' G0 0 1 u 0 F1). Как видно из полученного вектора значений для выхода вентиля f, на втором наборе его значение равно D’. В

соответствии с интерпретацией элементов алфавита B4 это означает, что на втором наборе рассматриваемая неисправность обнаруживается на выходе вентиля. Если в результате распространения влияния неисправности хотя бы для одного набора на каком-либо выходе получается значение D или D',

то данная неисправность проверяется данным тестом.

В случае успешного завершения прямого распространения влияния неисправности на выходе корневого элемента к внешним выходам схемы необходимо выполнить обратное распространение влияния неисправности по соответствующей подсхеме. Используя обратные функции (Табл.3.7),

следует параллельно по наборам распространить критические значения с выхода корневого элемента на линии подсхемы, учитывая их значения,

установившиеся в результате прямой фазы моделирования. Очевидно, что соответствующие неисправности на линиях, получивших значения D или

D' хотя бы на одном из наборов, также проверяются. При этом следует проверять значения линий только на тех наборах, для которых были получены критические значения D или D’ хотя бы на одном из внешних выходов схемы. Покажем на примере вентиля И f=x1 x2 как выполняется распространение влияния неисправностей в обратной фазе. Пусть в исправном устройстве на входах вентиля на 8 наборах установились следующие значения x1=(0010111u), x2=(01011u01). Тогда в компонентах имеем:

x10 =(11010001), x1D′ =(00000001), x1D =(00000001), x11 =(00101111),

194

x20 =(10100110), x2D′ =(00000100), x2D =(00000100), x12 =(01011101).

Предположим, что на выходе вентиля установились следующие значения

f=(0D'D'01u0u), чему соответствует следующее компонентное представление:

f 0 =(10010111), f D' =(01100101), f D =(00000101), f 1 =(00001101).

Выполняя вычисления с помощью обратных функций для вентиля И из

Табл.3.7, получаем значения для входа x1:

x10 =(10010001), x1D′ =(01000001), x1D =(00000001), x11 =(00101111),

Затем вычисляем значения для второго входа x2:

x20 =(10000110), x2D′ =(00100100), x2D =(00000100), x12 =(01011101).

Таким образом, имеем x1=(0 D' 1 0 1 1 1 u), x2=(0 1 D' 1 1 u 0 1). Из

полученных результатов определяем, что на втором наборе проверяется неисправность x1≡1 входа x1, на третьем наборе проверяется неисправность x2≡1. При определении проверяемости неисправности в данном случае надо просматривать только значения, соответствующие второму и третьему наборам, так как неисправность проявляется на выходе только на этих наборах.

Ниже на рис.5.18 представлен псевдокод алгоритма параллельного

(по наборам) и одиночного (по неисправностям) моделирования неисправностей. Основным является цикл по неисправностям, в процессе которого каждая неисправность из списка моделируется на группах наборов, пока тест не будет исчерпан и не будет выявлено, что она проверяется. При выборе неисправности корневого элемента одной из максимальных одновыходных подсхем критерием выбора, как правило,

является близость к внешним выходам схемы. В основе прямого распространения влияния неисправности лежит алгоритм параллельного

(по группе наборов) моделирования в многозначном алфавите.

Моделирование реализуется событийным интерпретативным алгоритмом.

195

Если неисправность корневого элемента проверяется, то выполняется обратное распространение влияния неисправности, при котором мы движемся по подсхеме от выхода корневого элемента к ее входам. При обратном проходе также используется событийный алгоритм.

Одиночное_распространение_неисправностей(схема, тест)

{

Ввод_схемы();

Ввод_теста();

Разбиение_схемы_на_поддеревья();

Инициализация_схемы();

Генерация_списка_неисправностей(); while(список неисправностей не пуст)

{

Выбор_неисправности();

while(есть тестовые наборы и неисправность не обнаруживается)

{

Формирование_группы_наборов();

Прямое_распространение_влияния_неисправности(); if(неисправность проверяется)

{

if(неисправность на выходе корневого элемента подсхемы)

Обратное_распространение_влияния_неисправностей();

Сокращение_списка_неисправностей();

}

}/* конец цикла по наборам */ } /* конец цикла по неисправностям */

Вывод_списка_непроверенных_неисправностей();

Вывод_значения_полноты_теста();

}

Рис.5.18 Алгоритм параллельного (по наборам) и одиночного (по

неисправностям) моделирования неисправностей

196

5.6 Моделирование неисправностей задержек распространения сигналов

С внедрением КМОП-технологии возник новый класс физических неисправностей, которые проявляются в изменении времени распростра-

нения сигналов [74]. Правильное функционирование цифрового устройства возможно только в том случае, если времена распространения сигналов вдоль путей логической схемы лежат в определенных пределах.

Когда время распространения сигнала выходит за эти пределы, говорят,

что имеет место неисправность типа изменения задержки сигнала. В

подавляющем большинстве эти неисправности приводят к увеличению времени распространения сигналов. Поэтому мы будем рассматривать только неисправности типа увеличения задержки сигналов. Предложено два типа моделей для подобных неисправностей. Первая модель, напри-

мер, используемая в работе [75], оперирует с задержками сигналов логических элементов. Вторая - с задержками сигналов путей логических схем. Мы будем использовать второй тип модели - задержки сигналов вдоль путей, который был обоснован в работе [74]. В настоящем разделе будет показано как универсальные многозначные модели, разработанные в разделе 3, могут быть использованы для моделирования данных неисправностей.

Обычно различают неисправности типов задержка переднего фронта

(0→ 1) и задержка заднего фронта (1→ 0). В определенном смысле задержка переднего фронта соответствует неисправности const0, так как она в течение некоторого времени ведет себя также как эта константная неисправность. Если это время значительно, то при задержке переднего фронта схема ведет себя почти также как и при неисправности const0 (в

случае ее проверяемости). Аналогично задержка заднего фронта соответ-

ствует неисправности const1.

197

Наиболее распространенный метод обнаружения неисправностей задержка сигналов заключается в следующем. Сначала на схему подается в момент времени t1 входной набор Х1. После стабилизации сигналов в схеме в момент времени t2 подается второй входной набор Х2. При этом передний фронт сигнала распространяется вдоль проверяемых путей в схеме от внешних входов к внешним выходам. Измеряя реальную задержку распространения сигналов и сравнивая ее с эталонной, можно обнаружить неисправности задержки распространения сигналов тестируемых путей в схеме. Таким образом для проверки подобных неисправностей необходима пара входных наборов <Х1,X2>. Значения сигналов в схеме,

установившиеся на наборе Х1 будем называть начальными значениями для пары <X1,X2>. Аналогично определим конечные значения, которые устанавливаются на наборе Х2 (в схеме не содержащей неисправности типа задержка сигнала).

|

x1 |

F0 |

G1 |

|

|

|

|

|

|

|

|

|

G5 |

|

|

|

|||||||

|

|

|

|

x6 |

|

F0 |

|

|

|

|

|

||||||||||||

|

& |

|

|

|

|

|

|

|

|||||||||||||||

|

1→0 |

|

|

|

|

|

|

|

|

|

|

x10 |

|||||||||||

|

|

|

|

|

1→0 |

|

|

|

|

|

& |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G4 |

|

|

|

|

F0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

x9 |

F0 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1→0 |

|

|

|

|

|

|

||||

|

|

|

x3 |

|

F0 |

|

G2 |

|

|

|

|

|

|

|

G6 |

|

x11 1 1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

||||||

|

|

|

|

|

|

|

|

|

x7 |

|

F1 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

1→0 |

|

|

& |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

F1 |

||||||||||||||

|

|

|

|

|

|

|

0→1 |

|

|

|

|

→0 |

|

|

|

||||||||

|

|

|

x4=1 |

|

|

|

|

|

|

|

|

G3 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рис.5.19 Пример схемы с неисправностями типа "задержка

распространения сигнала"

198

Согласно [74] пару входных наборов <Х1,X2> будем называть устойчивым тестом для задержки распространения сигналов по пути Р,

если она проверяет эту неисправность независимо от других неис-

правностей типа задержка сигнала, не расположенных на данном пути Р.

Например, для схемы, представленной на рис.5.19, пара наборов <11110, 01010> (значения даны в порядке x1, x2 , x3, x4, x5 ) является устойчивым тестом для неисправности задержки пути P1 = (x3, x7 , x9 , x10 ) . Анализ поведения схемы на этой паре наборов показывает, что задержка на пути

Р1 будет обнаружена независимо от наличия задержек на других путях схемы (например, на путях P2 = (x1, x6 , x10 ) или P3 = (x3, x6 , x10 ) ). Важность понятия устойчивого теста обуславливается тем, что в реальных схемах задержки распространения сигналов могут изменяться вследствие технологических причин. Поэтому для того, чтобы неисправность задержки данного пути не была компенсирована другими неисп-

равностями, необходимо использовать устойчивые тесты.

Согласно [74], пару входных наборов будем называть неустойчивым тестом для задержки распространения сигналов по пути Р, если она проверяет эту неисправность при условии, что входы логических элементов пути Р, не принадлежащие ему, принимают конечные значения до того, как изменение сигнала вдоль пути Р достигает этих элементов.

Например, на рис.5.19 указанная выше пара наборов является неус-

тойчивым тестом для неисправности «задержка распространения сигнала» вдоль пути P4 = (x3, x7 , x9 , x11,) , так как она проверяет ее при условии, что значение сигнала на х8 установится в 1 до прибытия на элемент G6

изменения сигнала вдоль пути Р4. Отметим, что эта пара наборов для задержки сигналов путей P2 = (x1, x6 , x10 ) и P3 = (x3, x6 , x10 ) не является даже устойчивым тестом.

199

Непосредственно из определения неустойчивого теста вытекает следующее. Для того, чтобы пара наборов < X1, X 2 > была неустойчивым тестом пути Р необходимо и достаточно выполнение условия всех элементов Gk пути

dGk |X =X 2 = 1,

dX ik

где xik - вход Gk, принадлежащий пути. То есть выход элемента Gk должен зависеть от входа xik, на который приходит изменение сигнала по пути Р,

при конечных (установившихся) значениях остальных входов этого элемента. Для устойчивого теста данное условие является необходимым,

но недостаточным. Например, для элемента G6 схемы рис.5.19 это условие выполняется, но пара наборов < X1, X 2 > не является устойчивым тестом для пути P4 = (x3, x7 , x9 , x11,) . Можно показать, что кроме приведенного выше условия необходимо, чтобы на паре < X1, X 2 > F 01 F10 = 1 (где

F 01, F10 - ориентированные булевы дифференциалы [1] ) .

В работах [74,76] для анализа неисправностей типа «задержка распространения сигнала» использовалась шестизначная логика (которая также кратко будет рассмотрена в конце данного раздела). Мы, в основном будем использовать следующее подмножество D5 универсального алфа-

вита

B16 : 0 = {00},1 = {11}, F0 = {00 10}, F1 = {11 01},u = {00 01 10 11}.

При анализе задержек распространения сигналов на паре < X1, X 2 >

переменных внешних входов, изменяющихся 0→ 1 (передний фронт) прис-

воим значение F1. Аналогично переменным, с изменением 1→ 0 (задний фронт) припишем F0. Переменные входов, сохраняющие значения на этой паре наборов, получают значения 0 и 1 соответственно. После присваивания значений переменным внешних входов следует выполнить моделирование в алфавите D5. Например, для пары наборов < X1, X 2 >

200