Скобцовы Моделирование и тестирование

.pdf

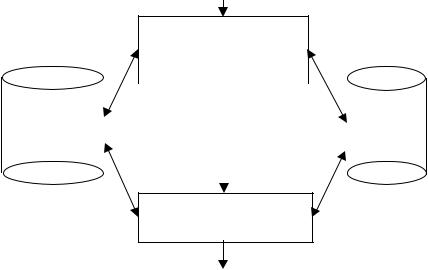

Фаза1 имеет низкие вычислительные затраты, не ориентирована на конкретную неисправность)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Непроверямые |

|

|

|

|

|

|

Тестовый |

неисправности |

|

|

|

|

|

|

набор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Фаза2 ориентирована на конкретную неисправность

Рис.6.18 Структура системы генерации тестов

Псевдокод укрупненного алгоритма генерации тестов первого этапа представлен на рис.6.19.

Первая фаза(схема)

{

While(полнота или время не достигнуты)

{

Генерация теста(t);

Моделирование неисправностей(t);

p=число вновь проверяемых неисправностей(t);

if(p приемлемо) then включение t в тест;

}

}

Рис.6.19 Первая фаза генерации тестов

Первая фаза заканчивается при достижении необходимой для первой фазы полноты теста, определяемой пользователем, либо вследствие лимита времени. При этом число неисправностей, проверяемых одним тестовым набором, сначала достаточно велико, а затем быстро уменьшается. Соответственно число не включенных в тест входных наборов быстро возрастает. В конце первой фазы формируется множество

261

7. ПОСТРОЕНИЕ ТЕСТОВ ДЛЯ УСТРОЙСТВ С ПАМЯТЬЮ

Одной из самых сложных проблем при создании систем автоматизированного проектирования и диагностики дискретных устройств является задача разработки алгоритмов моделирования и генерации проверяющих тестов ДУ с памятью. Это объясняется дополнительными трудностями, возникающими из-за неопределенности начального состояния ДУ с памятью и возможных состязаний сигналов. В

силу этих обстоятельств методы построения проверяющих тестов и моделирования неисправных ДУ с памятью разработаны значительно хуже. Кроме того, применение методов контролепригодного проектирования, позволяющих свести диагностику ДУ с памятью к диагностике комбинационных ДУ не всегда возможно и эффективно [1,44].

Поэтому в настоящий момент данная задача является по-прежнему актуальной.

Существующие подходы к тестированию устройств с памятью можно классифицировать на две группы: методы, основанные на теории экспериментов с конечными автоматами (КА), и структурные методы построения тестов. Методы из первой группы в качестве модели ДУ с памятью используют конечный автомат. В основе построения проверяющего эксперимента или теста лежит построение диагностической последовательности (ДП) [93]. В случае, когда ДП не может быть построена, применяются модифицированные проверяющие эксперименты

[94], основанные на использовании уникальной последовательности.

Также при построении проверяющих экспериментов применяются синхронизирующая и установочная последовательности [95]. К

преимуществам алгоритмов, основанных на теории экспериментов с автоматами, можно отнести высокую полноту проверки неисправностей полученными тестами. Необходимость построения автоматной модели

266

исходной логической схемы, экспоненциальный рост сложности

табличного представления автомата 2n 2n = 22n (n – количество

элементарных ячеек памяти – триггеров или линий обратных связей, 2n -

количество состояний автомата Рис.7.1) и большая длина получаемых тестов сделала автоматные методы не очень привлекательными с практической точки зрения построения проверяющих тестов для интегральных схем.

Структурные методы генерации проверяющих тестов в качестве модели ДУ используют логическую схему или его укрупненное структурное описание. ДУ на логическом уровне, как правило,

описываются разработчиками в виде логической схемы, поэтому необходимость в каких-либо дополнительных построениях отсутствует.

Как было сказано ранее (глава 1), ДУ без памяти представляются комбинационными логическими схемами, ДУ с памятью – последовательностными логическими схемами [1,39,44]. В большинстве структурных методов для ДУ с памятью процесс построения проверяющего теста заключается в получении входной последовательности, различающей исправное и неисправное ДУ, с

помощью применения разнообразных многозначных моделей и алгоритмов активизации критических путей, а также некоторых других подходов [1]. В этом случае сложность построения тестов для ДУ с памятью определяется числом линий обратных связей n, значения сигналов на которых определяет текущее состояние ДУ с памятью.

Напомним, что состояние конечного автомата соответствует и определяется вектором значений сигналов линий обратных связей или иначе переменных состояния ДУ с памятью. Как, уже говорилось ранее, в

случае автоматного подхода сложность построения теста определяется числом состояний конечного автомата, которое может достигать числа 2n .

267

Очевидно, что даже при небольшом числе линий обратных связей сложность построения теста автоматными методами может быть высокой.

Существует так называемая проблема «взрыва состояний» - начиная с некоторого значения n, число состояний КА резко возрастает (происходит

"взрыв" их количества). С другой стороны использование структурной модели последовательностных логических схем и многозначных моделей обеспечивает относительно невысокую по числу переменных состояния,

сложность структурных алгоритмов. Однако в силу некоторых особенностей структурных методов получаемые тесты обладают недостаточно высокой полнотой по сравнению с автоматными методами.

Поэтому в данной главе нами, кроме классических автоматного и структурного подхода, рассматриваются комбинированные методы построения тестов для ДУ с памятью, в которых осуществляется попытка объединить преимущества автоматных и структурных методов.

7.1 Структурный подход

Известные структурные методы построения тестов для цифровых устройств с памятью являются обобщением рассмотренных в главе 6

методов для комбинационных схем на последовательностные. Наиболее распространённый на практике подход к построению тестов для последовательностных схем основан на преобразовании их в так называемый комбинационный эквивалент (КЭ).

7.1.1 Итеративные комбинационные схемы

В комбинационном эквиваленте, получаемом путём условного обрыва обратных связей, вектор Y = ( y1, y2 ,..., yn ) представляет так

называемые псевдовходы, |

~ |

~ |

~ |

~ |

- псевдовыходы |

а вектор Y |

= ( y1 |

, y2 |

,..., yn ) |

||

(Рис.7.1) [1,44]. |

|

|

|

|

|

268

|

X |

|

Комбинационная |

|

Z |

|

|

|

X |

|

|

Комбинационная |

Z |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

~ |

|

|

|

|

|

|

~ |

|

||||||

|

|

|

логическая схема |

|

|

|

|

|

|

логическая схема |

|

||||||

|

Y |

|

|

Y |

|

|

|

Y |

|

|

Y |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б) Комбинационный эквивалент |

||||

|

|

|

|

Триггеры |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

последовательностной логической |

||||||

|

|

|

|

F/F |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

схемы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Синхроимпульс

CLOCK

а) Последовательностная логическая схема

Рис. 7.1 Преобразование последовательностной логической схемы в комбинационный логический эквивалент

Если рассматривается поведение последовательностной схемы в течение t тактов, то t комбинационных эквивалентов соединяются последовательно в итеративную комбинационную схему (ИКС), как показано на Рис.7.2. Здесь произвольная j-я итерация I j итеративной

комбинационной схемы соответствует состоянию исходной последовательностной схемы на j-м такте времени. При этом компоненты векторов X j , Z j соответствуют линиям первичных входов и выходов

~

соответственно, Y j , Yj - псевдовходам и псевдовыходам соответственно на

~

j-м такте. Также очевидно, что Yj , Yj - это линии, определяющие состояние последовательностного ДУ в начале и в конце j-го такта соответственно.

Рис.7.2 Структура комбинационной итеративной схемы из t КЭ

269

Далее при генерации тестов можно применять один из методов,

разработанных для комбинационных схем, с учётом специфики последовательностных. В качестве примера рассмотрим простейший триггер, представленный на рис.7.3, и его комбинационный эквивалент на

рис.7.4.

X1 |

|

|

X1 |

|

|

||

|

& |

Z |

|

& |

Z |

||

|

|

||||||

|

|

|

|

|

|

||

~

Y

|

|

& |

|

Y |

|

& |

|

|

|

|

|

|

|

||

X2 |

|

|

V≡1 |

X2 |

|

|

V≡1 |

|

|

|

|

|

|

||

Рис.7.3 Триггер |

Рис.7.4 Комбинационный эквивалент |

||||||

|

|

|

|

|

триггера |

||

Рассмотрим построение |

теста, который проверяет неисправность |

||||||

V ≡ 1 на нижнем плече триггера на основе методов с использованием |

|||||||

шестизначного |

алфавита T6, |

рассмотренных |

в разделе 6. Процесс |

||||

построения |

теста |

начинается |

|

с |

внесения |

значения |

V1=D', |

|||

соответствующего неисправности const 1, |

в итеративной схеме из одного |

|||||||||

комбинационного эквивалента, как это показано на рис.7.5. |

|

|||||||||

|

|

|

x11=1 |

|

|

|

|

|

||

|

|

|

|

|

& |

|

D |

z1=D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y1 =D |

|

|

|

|

|

y1=1 |

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x12=1 |

|

V1=D’ |

|

|

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Рис.7.5 Построение тестовой последовательности – 1 КЭ

270